Semiconductor device and preparation method thereof

A technology of semiconductors and devices, applied in the field of semiconductor devices and their preparation, can solve the problems that the performance requirements of large-scale interconnection structures cannot be balanced with the performance requirements of small-scale interconnection structures

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

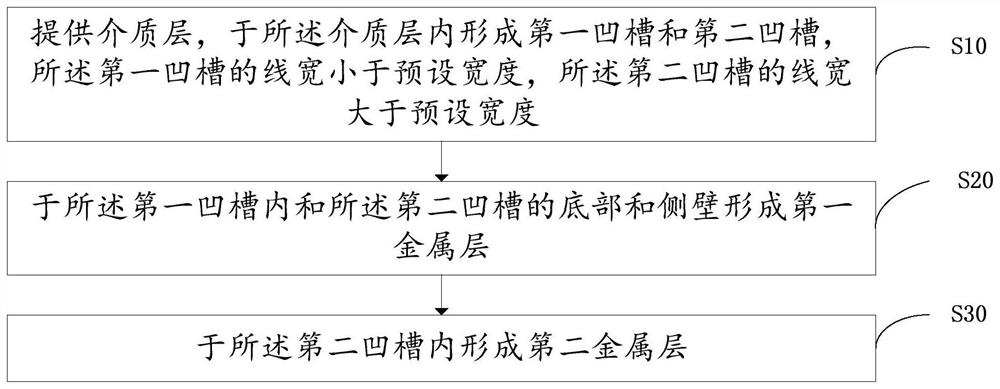

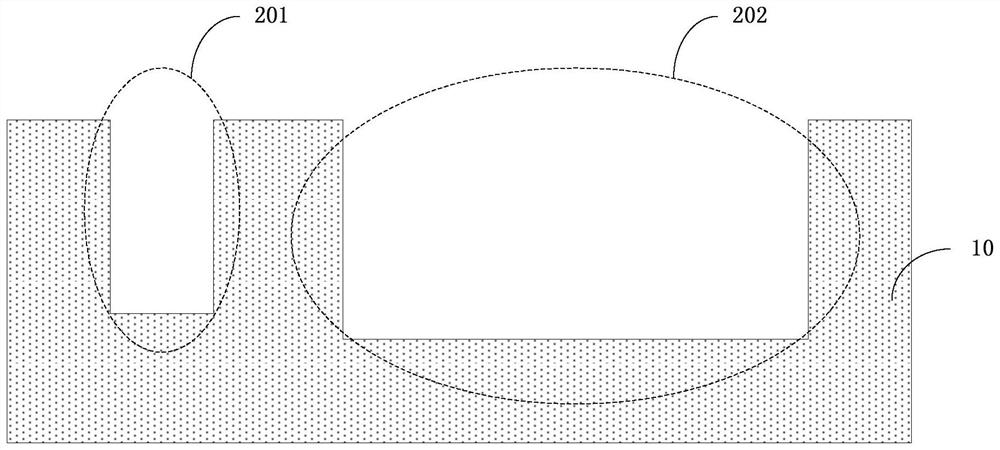

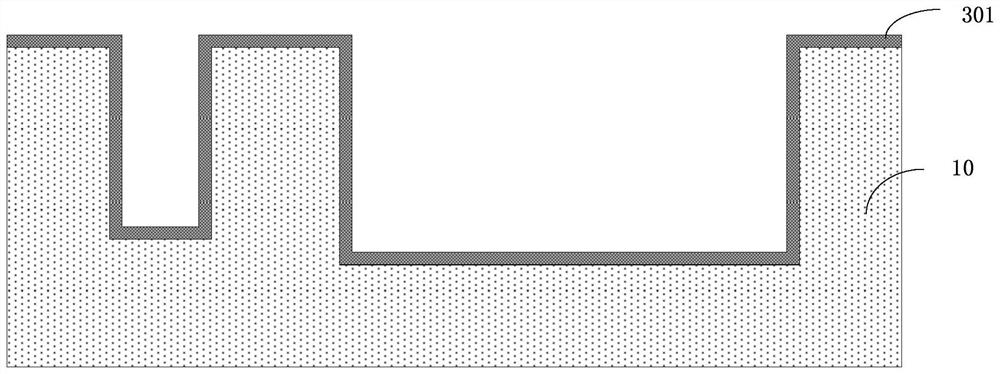

[0032] Such as figure 1 As shown, a method for preparing a semiconductor device is provided, comprising: providing a dielectric layer 10, forming a first groove 201 and a second groove 202 in the dielectric layer 10, the line width of the first groove 201 is smaller than that of the second groove The line width is 202; the first metal layer 401 is formed in the first groove 201; the second metal layer 402 is formed in the second groove 202.

[0033] S10: Provide a dielectric layer 10, and form a first groove 201 and a second groove 202 in the dielectric layer 10, the line width of the first groove 201 is smaller than the line width of the second groove 202, such as figure 2 shown.

[0034] In one embodiment, the first groove 201 penetrates the dielectric layer 10 , and the second groove 202 penetrates the dielectric layer 10 .

[0035] In one embodiment, the dielectric layer 10 includes silicon dioxide, other low dielectric constant materials, and the like.

[0036] In one...

Embodiment 2

[0069] Such as Figure 7 As shown, a semiconductor device is provided, comprising: a dielectric layer 10; a first groove 201 located in the dielectric layer 10; a second groove 202 located in the dielectric layer 10, and the line width of the first groove 201 is smaller than that of the second groove. The line width of the groove 202 ; the first metal layer 401 is located in the first groove 201 ; the second metal layer 402 is located in the second groove 202 .

[0070] In one embodiment, the line width of the first groove 201 is smaller than the preset width, and the line width of the second groove 202 is larger than the preset width.

[0071] In one embodiment, the predetermined width is between 20nm˜40nm, for example, the predetermined width may be 20nm, 25nm, 30nm, 35nm, 40nm.

[0072] In one embodiment, the line width of the first groove 201 is less than 30nm, for example, the line width of the first groove 201 can be 7nm, 10nm, 15nm, 20nm, 28nm, the line width of the se...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Width | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More