Wafer etching method

A wafer, etch depth technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve the problem of poor etch depth uniformity of the first material layer, so as to improve the uniformity of etch depth and meet the performance requirements Requirement, loss reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

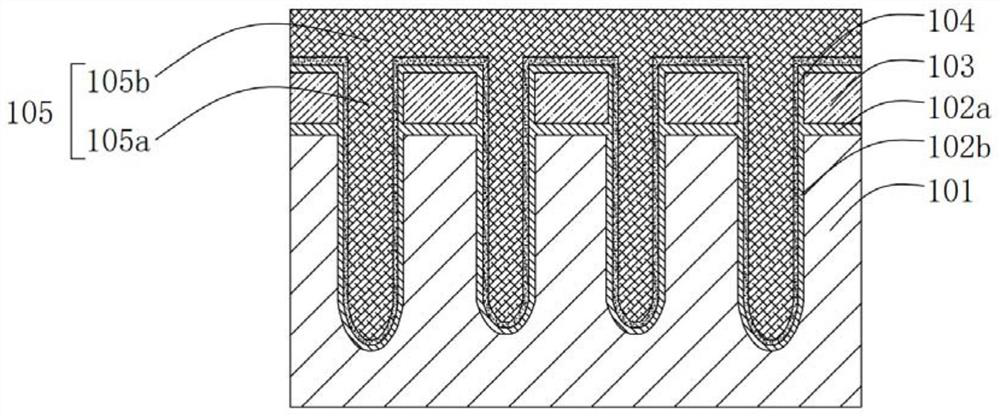

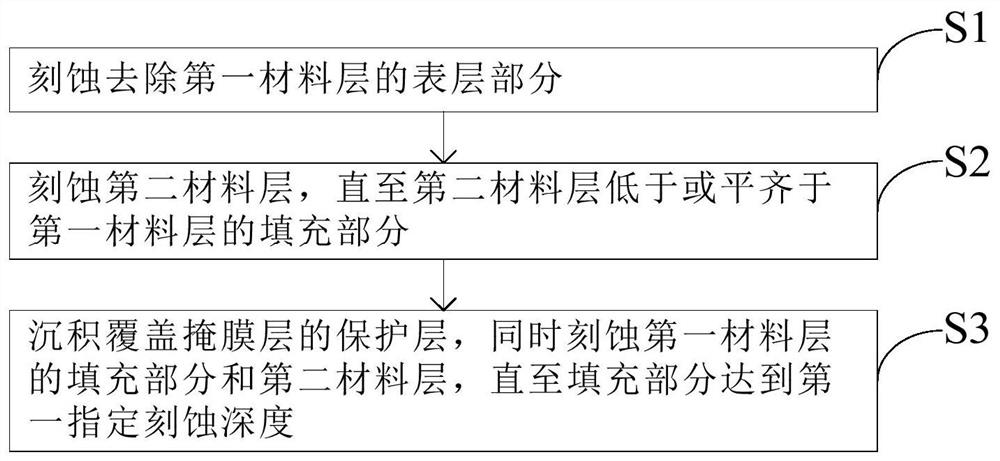

[0047] The wafer etching method provided in this embodiment is, for example, applied to the etching back method of the first material layer (such as tungsten). Before performing the etching back method, the wafer to be etched has a morphology as figure 1 As shown, the wafer includes a substrate 101, a mask layer 103 disposed on the substrate 101, and a first material layer 105, wherein the substrate 101 is, for example, a silicon wafer (Si), and the mask layer 103 is, for example, Silicon nitride (SiN) or silicon oxide (SiO 2 ), optionally, a natural oxide layer 102a is formed between the substrate 101 and the mask layer 103, and the natural oxide layer 102a is, for example, a natural oxide layer of silicon (ie, silicon oxide). Trenches or holes are correspondingly formed on the silicon wafer 101 , the natural oxide layer 102 a and the mask layer 103 . Optionally, the upper surface of the mask layer 103 and the sides of the groove or hole are covered with a silicon oxide laye...

no. 2 example

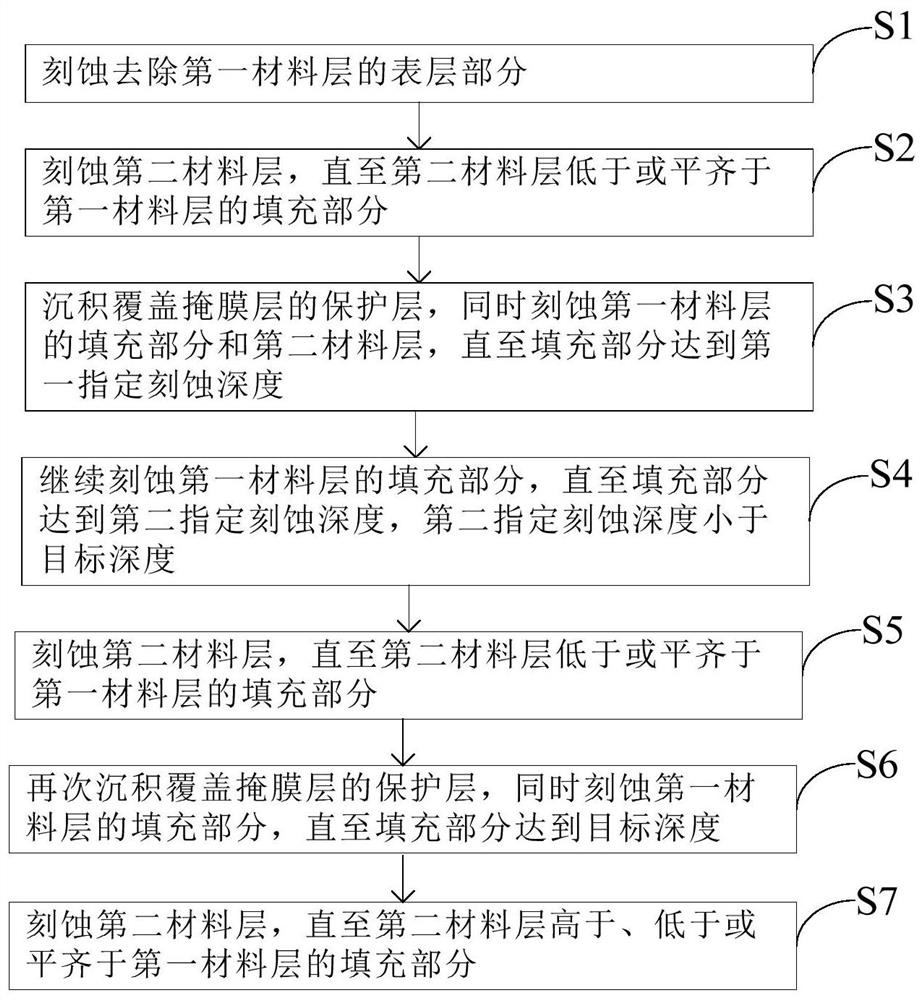

[0060] The wafer etching method provided in this embodiment is an improvement made on the basis of the above-mentioned first embodiment, that is, for the situation that the above-mentioned first specified etching depth is less than the preset target depth, in order to reduce the etching etch time, and ensure the uniformity of etch depth between trenches or holes of different widths, please refer to image 3 , the above-mentioned wafer etching method comprises the following steps:

[0061] S1. Etching and removing the surface layer portion 105b of the first material layer 105;

[0062] After step S1 is completed, the etched topography of the wafer is as follows Figure 4A As shown, the surface portion 105b of the first material layer 105 is almost completely removed, at this time, the initial etching depth of the filling portion 105a of the first material layer 105 is H0, and the initial etching depth of the second material layer 104 is h0.

[0063] S2. Etching the second mat...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More