Fault positioning method and fault positioning device

A fault location and fault location technology, applied in short-circuit testing, optical testing flaws/defects, electrical radiation detectors, etc., can solve the problems of location failure, high failure rate, missed leakage points, etc. Sample structure, the effect of shortening positioning time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

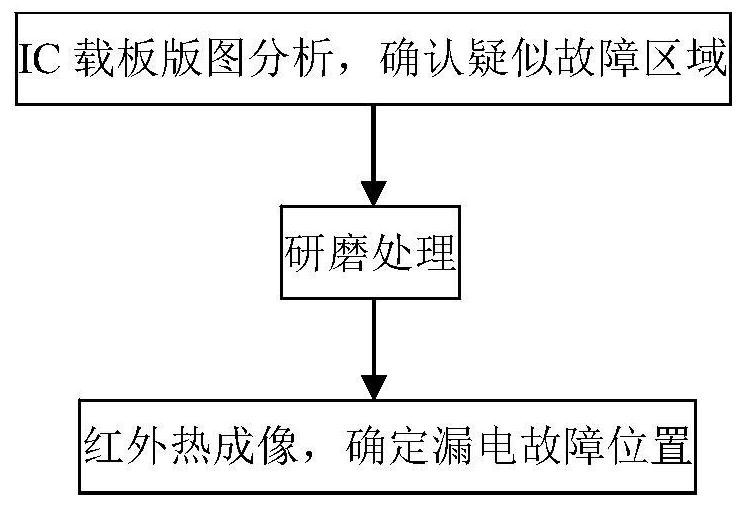

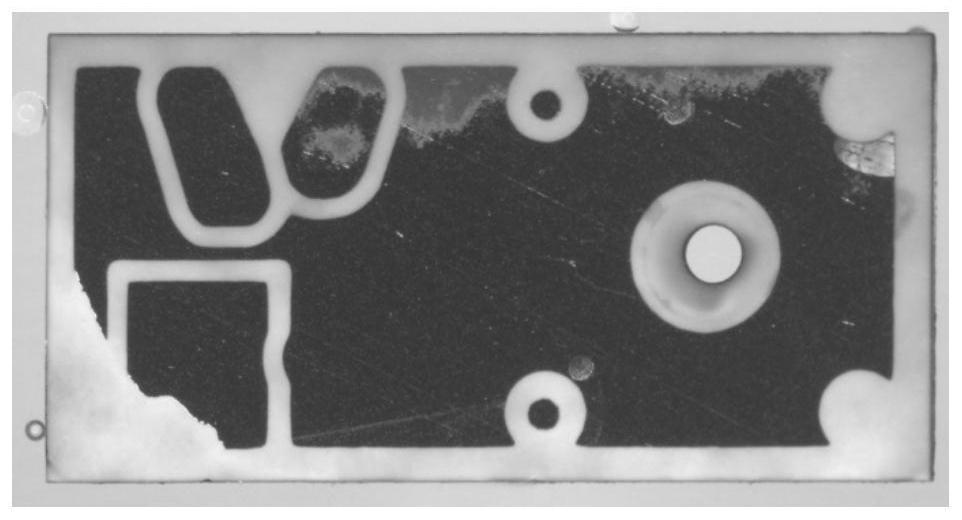

[0084] Such as figure 1 As shown, this embodiment provides an IC carrier board ( figure 2 It is the structural schematic diagram of the IC carrier board) the positioning method of the leakage fault position, specifically including:

[0085] 1. Use impedance testing equipment to perform impedance test on the faulty IC carrier board, and record the abnormal impedance value (impedance ≤ 10 8 Ω).

[0086] During the test, the magnitude of the leakage current is controlled, and it is controlled at the μA level to minimize the secondary damage of the current.

[0087] 2. Use the layout of the IC carrier board to conduct impedance tests on the lines that may have problems one by one, and continuously narrow the scope until the smallest suspected fault area is determined, such as confirming which layer the suspected fault area is on the carrier board, and which lines are in between Wait.

[0088] 3. Carry out plane grinding for the suspected faulty area identified on the IC carri...

Embodiment 2

[0096] This embodiment provides a method for locating the location of an IC carrier board leakage fault, which specifically includes:

[0097] 1. Use impedance testing equipment to perform impedance test on the faulty IC carrier board, and record the abnormal impedance value (impedance ≤ 10 8 Ω).

[0098] During the test, the magnitude of the leakage current is controlled, and it is controlled at the μA level to minimize the secondary damage of the current.

[0099] 2. Use the layout of the IC carrier board to conduct impedance tests on the lines that may have problems one by one, and continuously narrow the scope until the smallest suspected fault area is determined, such as confirming which layer the suspected fault area is on the carrier board, and which lines are in between Wait.

[0100] 3. Carry out plane grinding for the suspected faulty area identified on the IC carrier board. The grinding method is ordinary mechanical grinding. First, use coarse sandpaper to grind, ...

Embodiment 3

[0106] This embodiment provides a method for locating the location of an IC carrier board leakage fault, which specifically includes:

[0107] 1. Use impedance testing equipment to perform impedance test on the faulty IC carrier board, and record the abnormal impedance value (impedance ≤ 10 8Ω).

[0108] During the test, the magnitude of the leakage current is controlled, and it is controlled at the μA level to minimize the secondary damage of the current.

[0109] 2. Use the layout of the IC carrier board to conduct impedance tests on the lines that may have problems one by one, and continuously narrow the scope until the smallest suspected fault area is determined, such as confirming which layer the suspected fault area is on the carrier board, and which lines are in between Wait.

[0110] 3. Carry out plane grinding for the suspected faulty area identified on the IC carrier board. The grinding method is ordinary mechanical grinding. First, use coarse sandpaper to grind, a...

PUM

| Property | Measurement | Unit |

|---|---|---|

| impedance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More