Heterosynaptic electronic device based on two-dimensional ferroelectric semiconductor and preparation method of heterosynaptic electronic device

An electronic device and semiconductor technology, applied in the field of heterologous synaptic electronic devices and their preparation, can solve problems such as difficulty in simulating heterologous synaptic plasticity, and achieve the effects of reducing operating voltage and avoiding air oxidation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

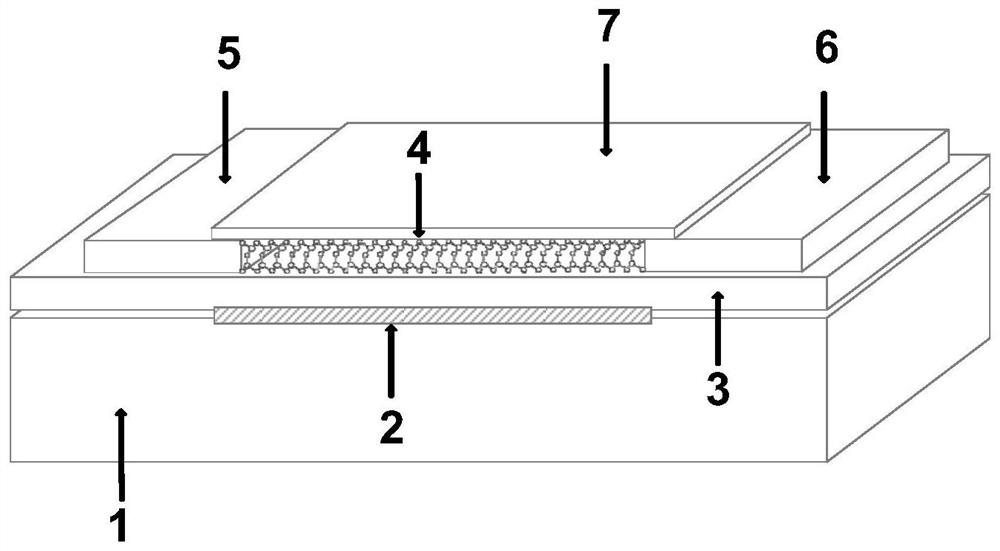

[0041] A preferred embodiment of the present invention provides a method for preparing a heterosynaptic electronic device based on a two-dimensional ferroelectric semiconductor. The specific steps are as follows:

[0042] 1) On SiO 2 A metal Au electrode was prepared on the substrate: first, the heavily doped Si / SiO 2 Strip mask patterns with 5 μm intervals and 10 μm width were etched on the substrate, and then thermal evaporation coating equipment was used to A 50nm-thick Au film was deposited on the substrate at a rate of 50nm, and then the substrate was immersed in an acetone solution for 30min and then lifted-off to obtain a patterned Au electrode.

[0043] 2) Preparation of PVA dry transfer film: first prepare a 10wt% PVA aqueous solution, and then take 5mL of the solution and drop it on the cleaned SiO 2 The substrate is then placed on a heating plate at a temperature of 50°C and baked for 10 minutes to obtain a PVA film; then a blade cuts a 3mm×3mm PVA film and place...

Embodiment 2

[0048] A preferred embodiment of the present invention provides a method for preparing a heterosynaptic electronic device based on a two-dimensional ferroelectric semiconductor. The specific steps are as follows:

[0049] 1) Preparation of encapsulation layer h-BN and graphene electrode: choose Si / SiO 2 As a supporting substrate, use mechanical exfoliation to obtain few-layer h-BN samples from h-BN crystals, and obtain single-layer or few-layer graphene samples from graphite layered crystals. location marker.

[0050] 2) Preparation of PVA dry transfer film: first prepare a 10wt% PVA aqueous solution, and then take 5mL of the solution and drop it on the cleaned SiO 2 Substrate, then place it on a heating plate at a temperature of 50°C and bake for 1 hour to obtain a PVA film; then a blade cuts out a PVA film with a size of about 3mm×3mm, and places it on a transparent glass sheet with the flat side facing up. On the PDMS substrate, finally obtain the PVA dry transfer film. ...

Embodiment 3

[0055] 1) On SiO 2 Metallic Pt electrodes prepared on the substrate: on Si / SiO 2 The substrate self-assembles a layer of monomolecular film, and a hard metal mask plate containing electrode patterns with a spacing width of 7um is placed on the substrate, and then thermal evaporation coating equipment is used to A 50nm-thick Pt film was deposited on the substrate at a rate of 50 nm, and a patterned Pt electrode was obtained by removing the metal mask.

[0056] 2) Preparation of PVA dry transfer film: first prepare a 10wt% PVA aqueous solution, and then take 5mL of the solution and drop it on the cleaned SiO 2 The substrate is then placed on a heating plate at a temperature of 50°C and baked for 10 minutes to obtain a PVA film; then a blade cuts a 3mm×3mm PVA film and places it on a PDMS substrate of the same size adhered to one end of a transparent glass sheet. Thus a PVA dry transfer film was obtained.

[0057] 3) PVA dry transfer of Pt electrodes: With the aid of a micros...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com