Vertical structure LED chip and manufacturing method thereof

A LED chip and vertical structure technology, applied in the direction of electrical components, circuits, semiconductor devices, etc., can solve problems such as the complexity of the LED chip manufacturing process, achieve current distribution and expansion performance improvement, excellent light transmittance, and reduce process difficulty. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0078] Various embodiments of the invention will be described in more detail below with reference to the accompanying drawings. In the various drawings, the same elements are denoted by the same or similar reference numerals. For the sake of clarity, various parts in the drawings have not been drawn to scale.

[0079] The invention can be embodied in various forms, some examples of which are described below.

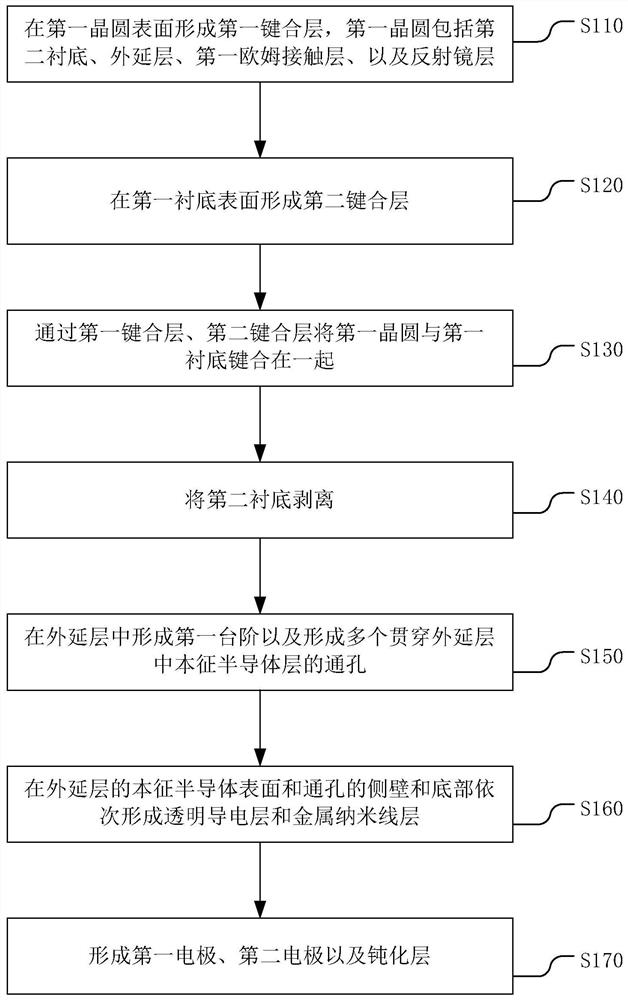

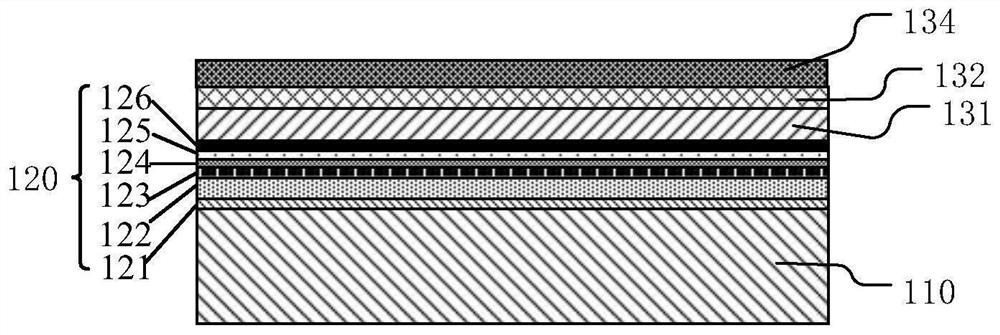

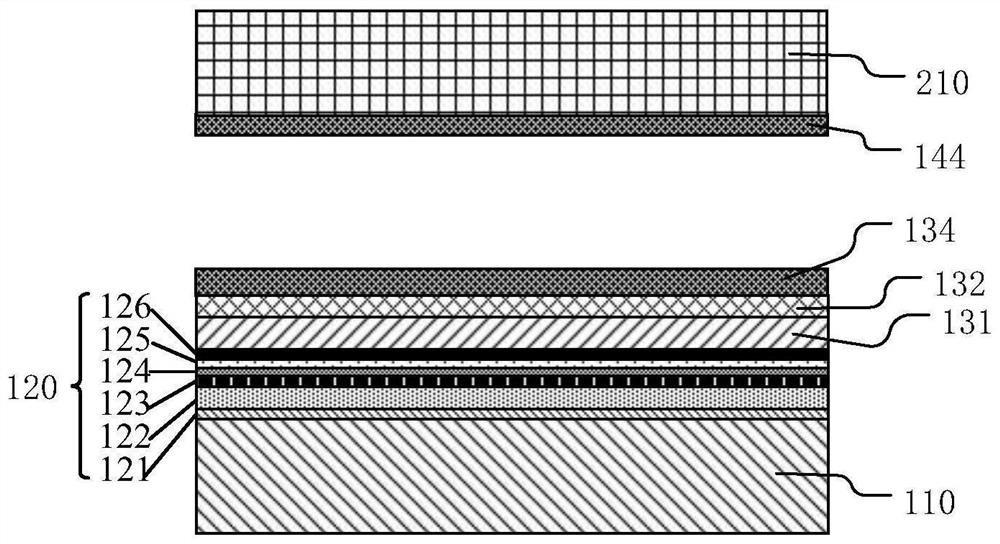

[0080] figure 1 A schematic flowchart of a method for manufacturing a vertical structure LED chip according to an embodiment of the present invention is shown. Figures 2a to 2g The structural cross-sectional views of different stages in the manufacturing process of the vertical structure LED chip provided according to the embodiment of the present invention are shown. image 3 show Figure 2e A top view of the semiconductor structure shown. The manufacturing method provided in this embodiment operates on the entire wafer. For the convenience of understanding, the d...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Diameter | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com