SOI wafer with high heat dissipation performance and preparation method of SOI wafer

A high heat dissipation, wafer technology, applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve the problem of low thermal conductivity of buried oxide layer, device channel current drop, application limitations of semiconductor-on-insulator technology, etc. problem, to achieve the effect of improving utilization rate, increasing integration, and improving heat dissipation performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

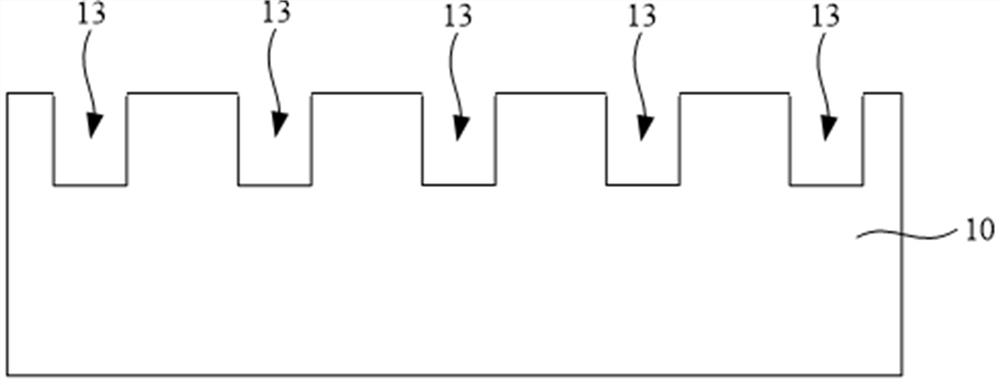

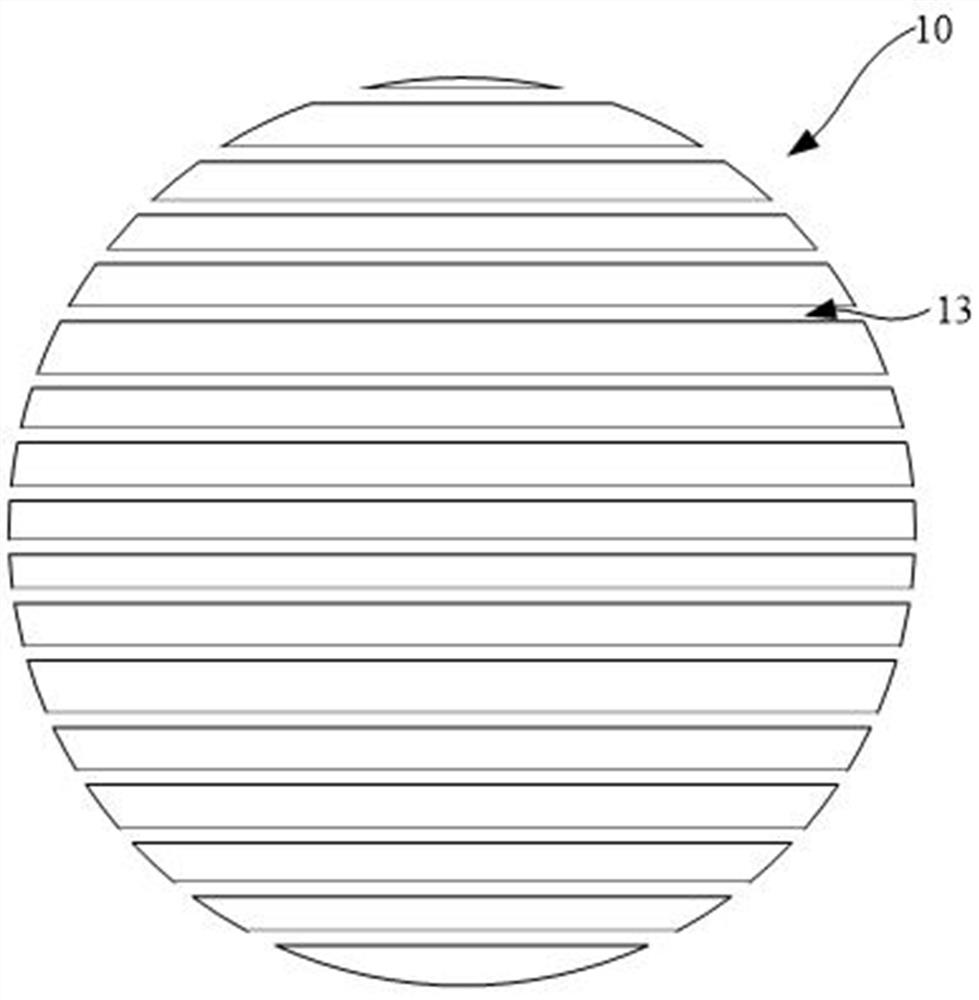

[0026] Embodiments of the present invention are described below through specific examples, and those skilled in the art can easily understand other advantages and effects of the present invention from the content disclosed in this specification. The present invention can also be implemented or applied through other different specific implementation modes, and various modifications or changes can be made to the details in this specification based on different viewpoints and applications without departing from the spirit of the present invention.

[0027] For example, when describing the embodiments of the present invention in detail, for the convenience of explanation, the cross-sectional view showing the device structure will not be partially enlarged according to the general scale, and the schematic diagram is only an example, which should not limit the protection scope of the present invention. In addition, the three-dimensional space dimensions of length, width and depth sho...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More