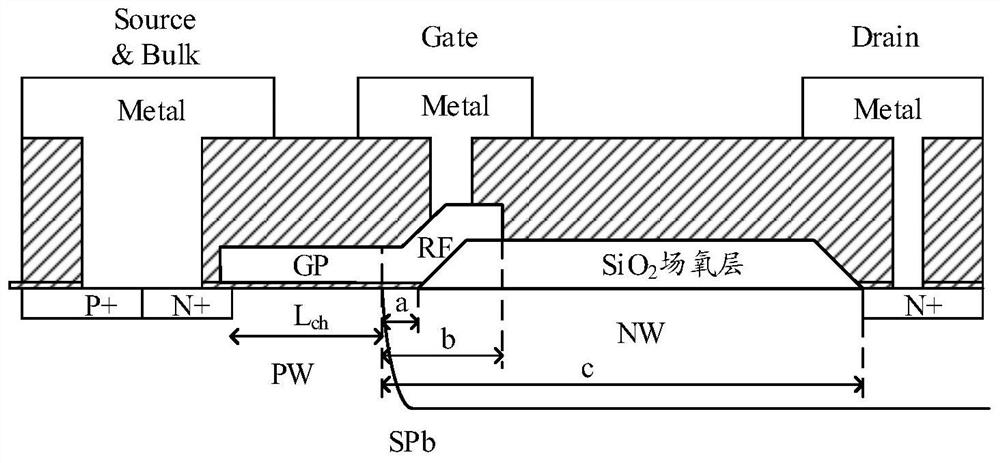

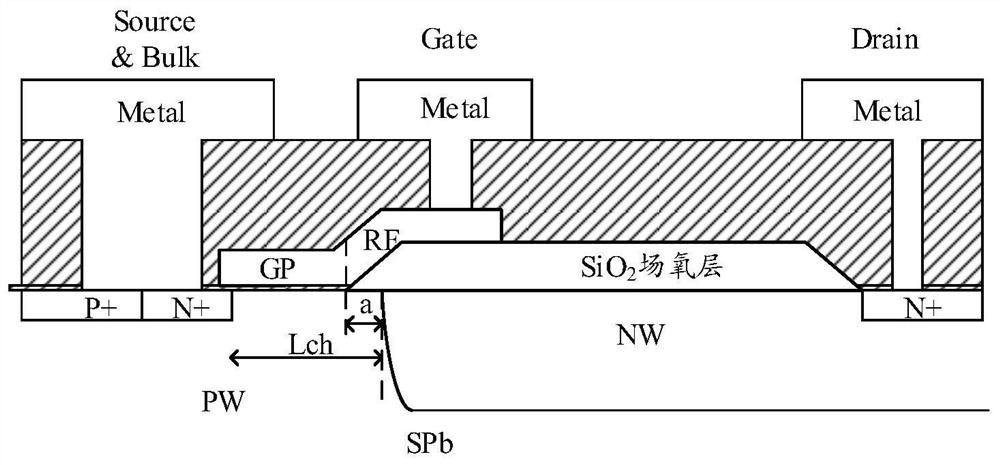

SiC LDMOS device and manufacturing method thereof

A manufacturing method and device technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as poor performance and low switching frequency, and achieve the effect of eliminating Cgd, small Cgd, and improving switching frequency and performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0046] In order to make the purpose, technical solutions and advantages of the application more obvious and understandable, the following will clearly and completely describe the application in conjunction with the embodiments of the application and the corresponding drawings, wherein the same or similar symbols throughout represent the same or similar elements or elements having the same or similar functions. It should be understood that the various embodiments of the application described below are only used to explain the application, and are not intended to limit the application, that is, based on the various embodiments of the application, those skilled in the art will not make an inventive step. All other embodiments obtained under the premise of labor all belong to the protection scope of this application. In addition, the technical features involved in the various embodiments of the present application described below may be combined with each other as long as they do ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More