A filter chip wafer-level packaging structure and packaging process

A wafer-level packaging and filter technology, which is applied in the manufacturing of semiconductor devices, electric solid-state devices, and semiconductor/solid-state devices, etc., and can solve the problems of insufficient structural strength of packaged chips, insufficient mechanical strength of silicon-capped wafers, and inability to reduce thickness. , to achieve the effect of improving the structural strength of the chip package, increasing the thickness of the thinning process, and reducing the process cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The preferred embodiments of the present invention will be described below with reference to the accompanying drawings. It should be understood that the preferred embodiments described herein are only used to illustrate and explain the present invention, but not to limit the present invention.

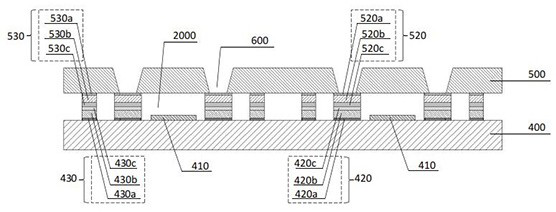

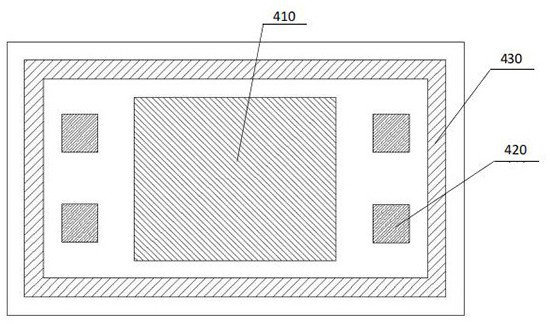

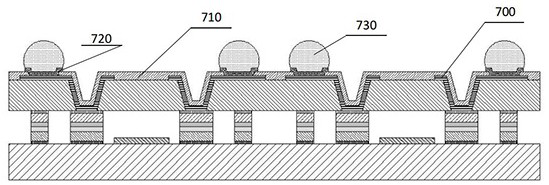

[0035] The embodiment of the present invention proposes a filter chip wafer-level packaging structure, which utilizes metal fusion bonding and eutectic bonding to realize wafer-level packaging in which a silicon cover is attached and a filter cavity is formed. When the metal bonding layer is formed on the filter wafer and the silicon cap wafer, a Cu intermediate layer is added to thicken the thickness of the entire metal stack, so that the total thickness of the metal stack on both sides reaches or exceeds 3~6 microns. Bonding is performed using the thickness of the metal stack itself to form a cavity of sufficient height without the need to etch the silicon-silicon cap substrate...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| distance | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More