Semiconductor structure and preparation method thereof, three-dimensional memory and storage device

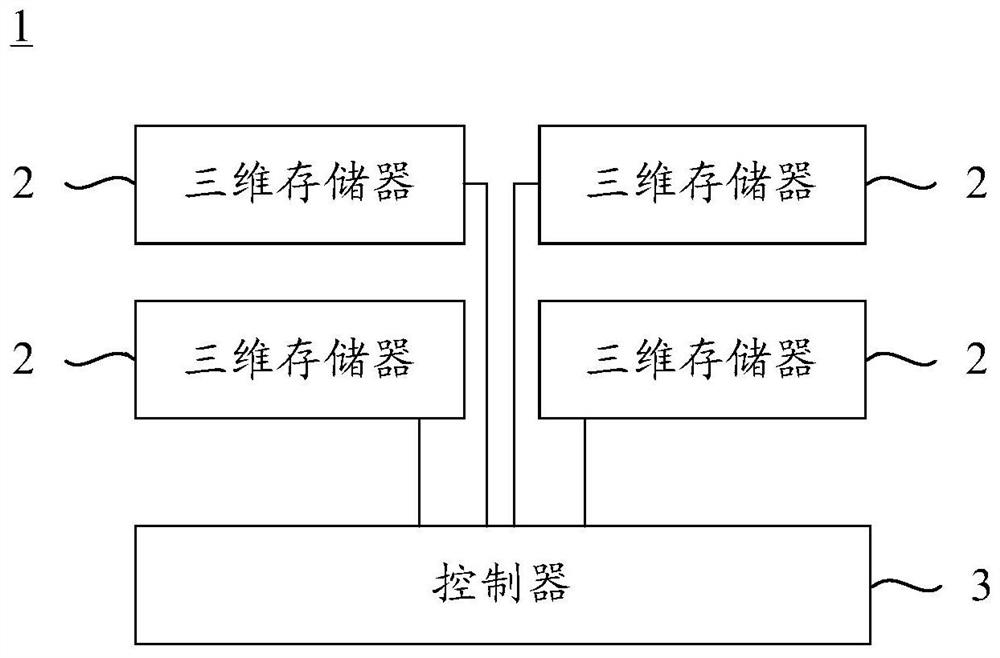

A semiconductor and isolation structure technology, which is applied in the field of semiconductor chips, can solve the problems of low integration of peripheral circuits of three-dimensional memory, and achieve the effects of improving cross-sectional characteristics, increasing integration, and reducing integration area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

preparation example Construction

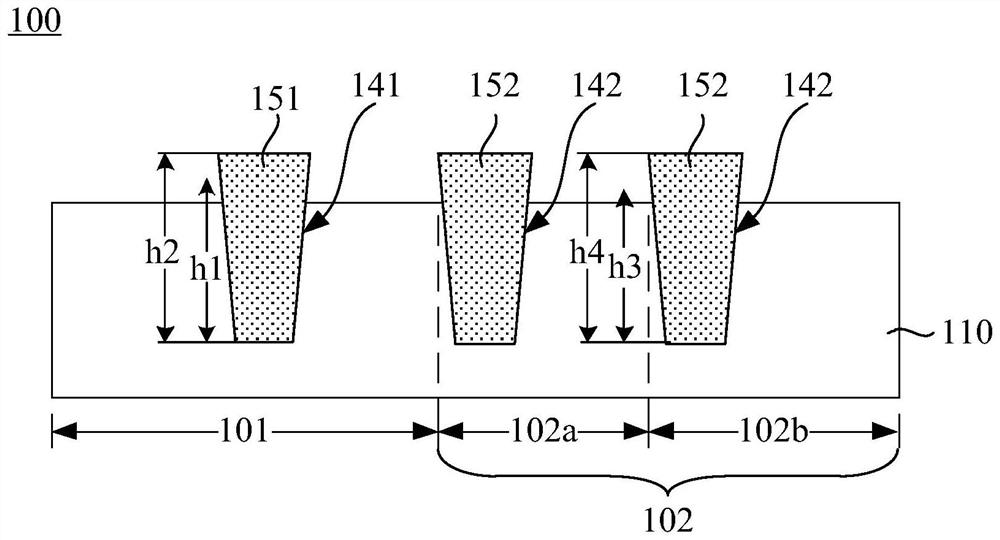

[0087] suggest a Figure 4A The manufacturing method of the semiconductor structure 100 shown includes: forming a first gate oxide layer 121 on the substrate 110, the first gate oxide layer 121 is located in the high voltage well region 101; then forming a first isolation structure 151 and a second isolation structure 152, Wherein, the first isolation structure 151 is located in the high voltage well region 101 , and the second isolation column 152 ′ is located in the low voltage well region 102 ; and then the second isolation structure 152 ′ is thinned to form the second isolation structure 152 .

[0088] However, during the fabrication of this semiconductor structure 10, as Figure 4B As shown, the gate oxide layer of the high-voltage well region 101 will be formed synchronously, which may easily cause damage to the first gate oxide layer 121 of the high-voltage well region 101 due to the hard mask integration process (such as Figure 5 shown).

[0089] Based on this, in o...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More