Semiconductor packaging structure and preparation method

A packaging structure and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as high integration density and large transmission bandwidth.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

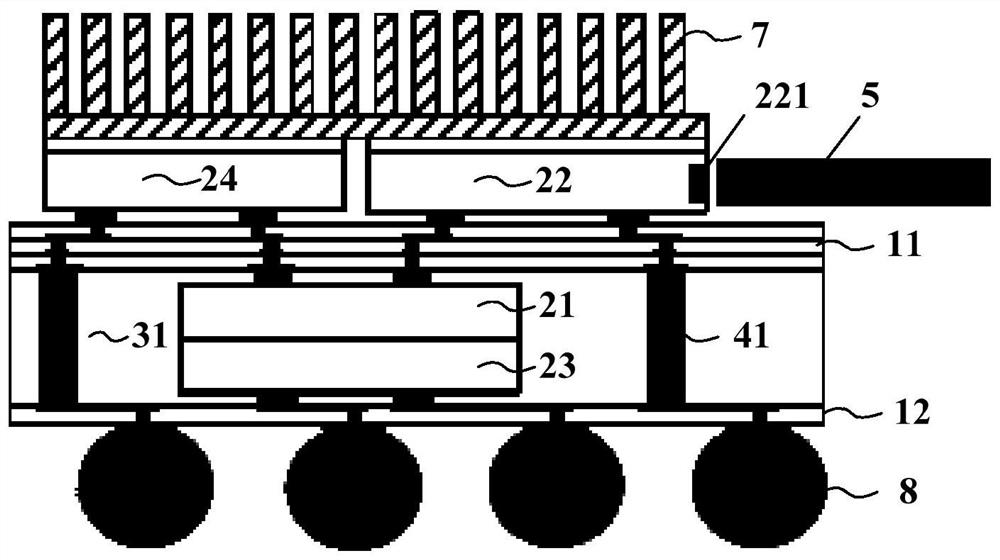

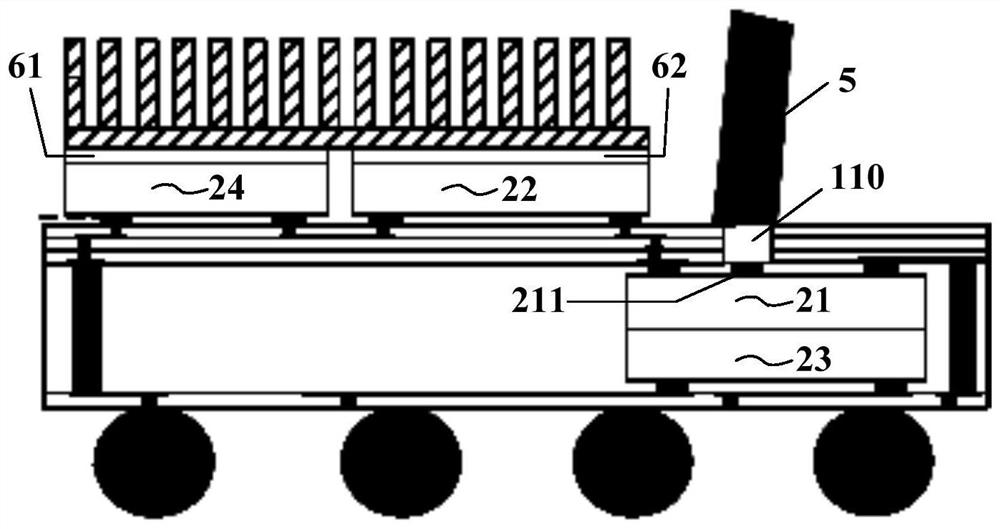

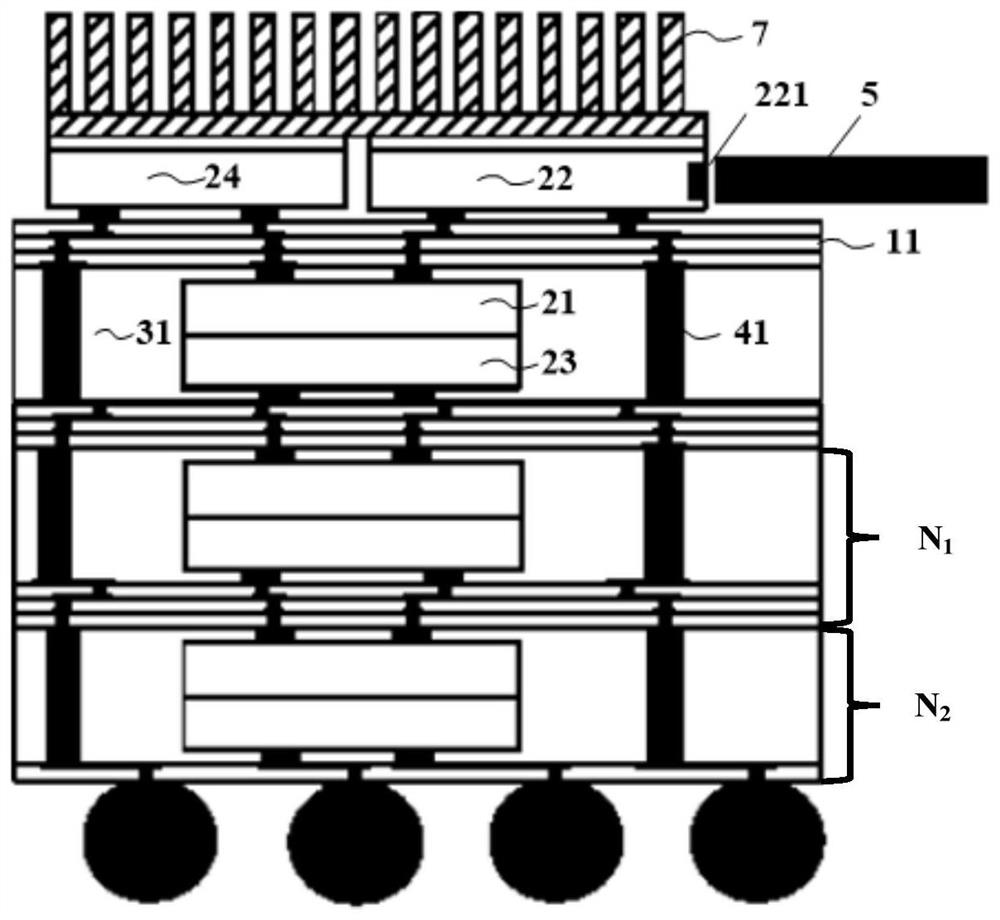

[0050] This embodiment provides a semiconductor packaging structure, such as figure 1 shown, including:

[0051] The second rewiring structure 12; the first functional chip 21 and the pressure supply chip 23 located on the side of the second rewiring structure 12, the pressure supply chip 23 is flip-chip mounted on the side of the second rewiring structure 12, The first functional chip 21 is installed on the side of the pressure supply chip 23 away from the second rewiring structure 12; it is located on the side of the second rewiring structure 12 and covers the side of the first functional chip 21 The wall and the first plastic sealing layer 31 of the side wall of the pressure supply chip 23; the first conductive connection located on the side of the first functional chip 21 and the pressure supply chip 23 and penetrating through the first plastic sealing layer 31 Part 41; the first rewiring structure 11 located on the side of the first plastic encapsulation layer 31 away fr...

Embodiment 2

[0063] This embodiment provides a method for preparing a semiconductor packaging structure, and the schematic flow chart is as follows Figure 5 shown, including the following steps:

[0064] Step S1: forming a second rewiring structure 12;

[0065] Step S2: forming a first conductive connector 41 on one side of the second rewiring structure 12 and electrically connecting with the second rewiring structure 12;

[0066] Step S3: Provide the first functional chip 21 and the pressure supply chip 23, flip-chip the pressure supply chip 23 on the side of the second rewiring structure 12, and mount the first functional chip on the pressure supply chip On the side away from the second rewiring structure, the first conductive connector 41 is located on the side of the first functional chip 21 and the pressure supply chip 23;

[0067] Step S4: Forming a first plastic encapsulation layer 31 on one side of the second rewiring structure 12, the first plastic encapsulation layer 31 covers...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More