Memory system and operating method thereof

A technology of memory, memory chips, applied in the field of memory systems, to achieve the effects of easy manufacturing process and shipment control, avoiding restrictions, large margins and durability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

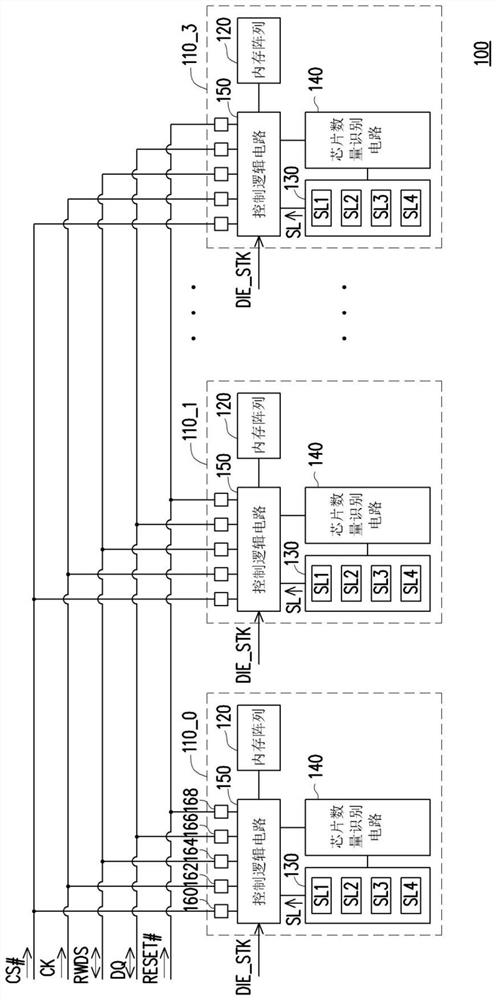

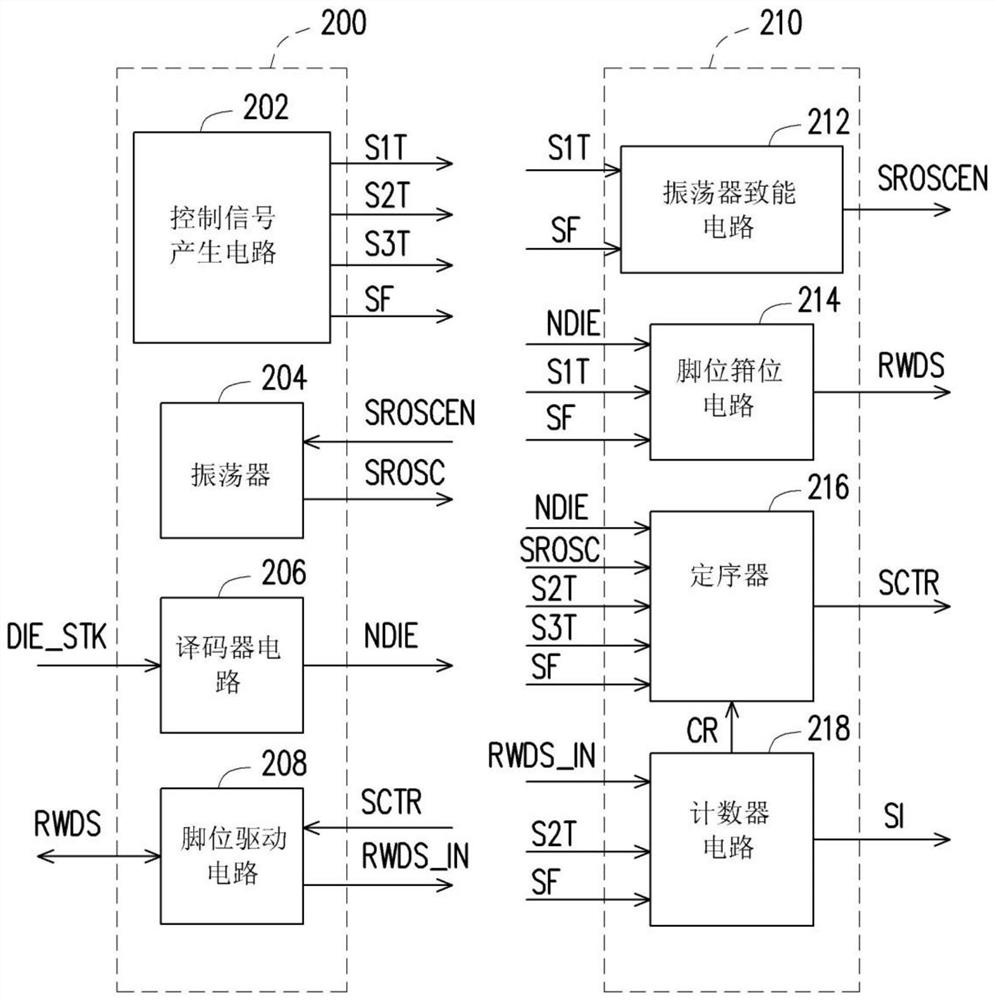

[0023] Reference will now be made in detail to the exemplary embodiments of the present invention, examples of which are illustrated in the accompanying drawings. Wherever possible, the same reference numbers will be used in the drawings and description to refer to the same or like parts.

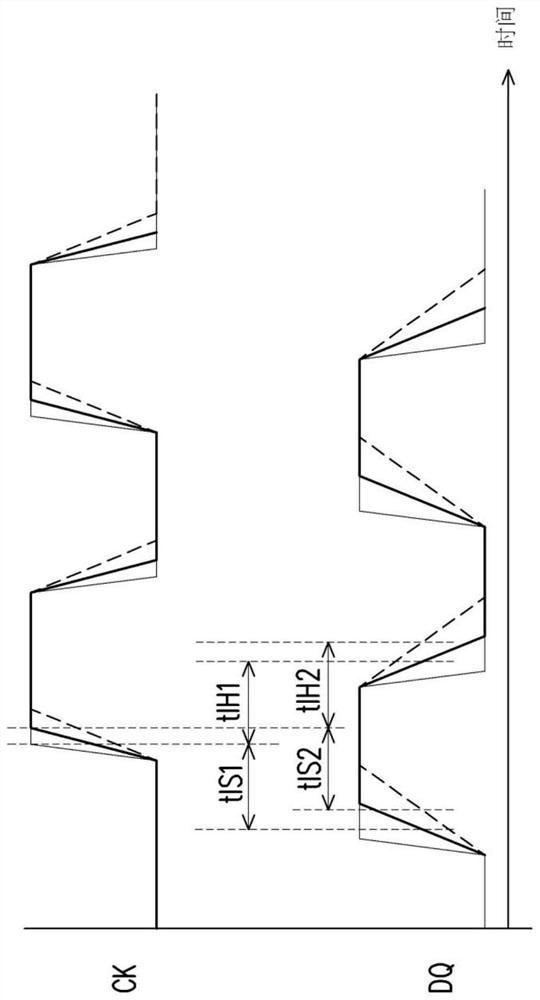

[0024] exist figure 1 In , the thin solid line represents the signal waveform received outside the package structure of the memory system. The thick solid line represents the signal waveform received by the memory chip when there is only one memory chip in the package structure. The dotted line represents the signal waveform received by the memory chip when two memory chips are stacked in the package structure.

[0025] Due to the influence of the input capacitor on the pin, the signal waveform of the thick solid line and the dotted line will have a signal delay compared with the signal waveform of the thin solid line, and the delay of the data signal DQ will be greater than the delay of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More