ESD protection structure and preparation method thereof

A technology of ESD protection and control gate, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problem of high static leakage and achieve the effect of ultra-low leakage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0044] As shown in FIG. 4, this embodiment provides an N-type ESD protection structure, the N-type ESD protection structure includes: full consumption

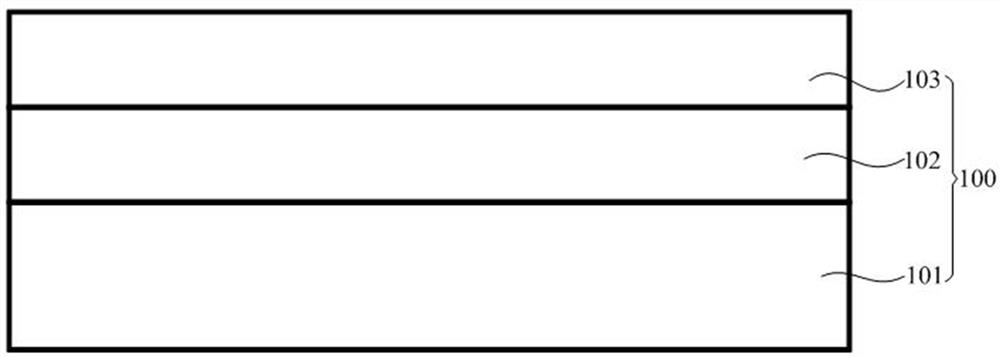

[0045] The fully depleted silicon-on-insulator 100 sequentially includes a silicon substrate 101, a buried oxide layer 102 and a top layer of silicon from bottom to top

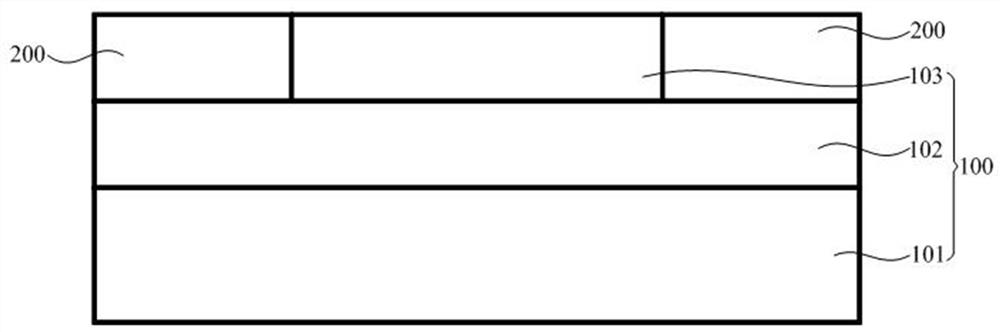

[0046] The silicide layer 200 is formed on the upper surface of the buried oxide layer 102, and is formed on both sides of the top layer silicon 103

[0047] Specifically, the silicide layer 200 sequentially includes silicide and metal silicide (not shown in the figure) from bottom to top,

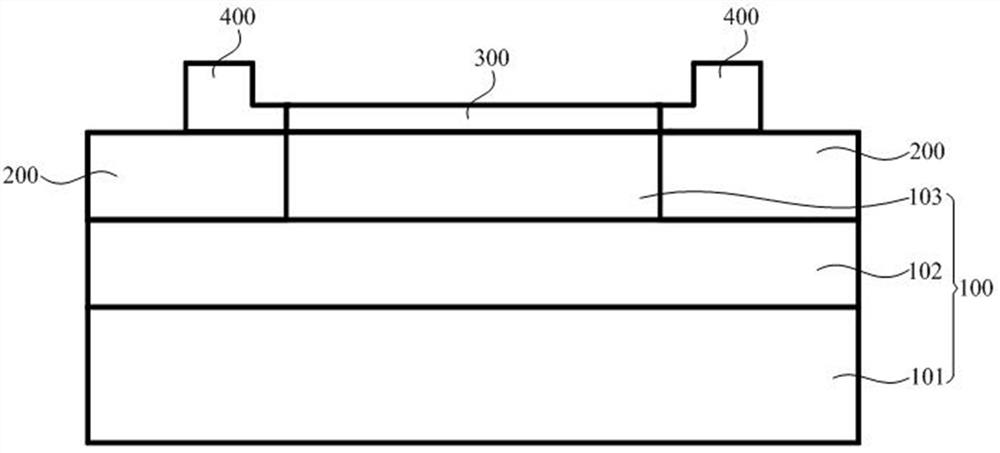

[0048] The gate oxide layer 300 is formed on the upper surface of the top layer silicon 103.

[0049] Specifically, the gate oxide layer 300 is a silicon oxide layer or a hafnium oxide layer. In this embodiment, the gate oxide layer 300 is made of oxygen

[0050] The isolation layer 400 is formed on a part of the upper surface of the silicide layer 200, and is formed on the ga...

Embodiment 2

[0074] This embodiment provides a P-type ESD protection structure, the difference between the structure and the first embodiment is that the top layer silicon

[0075] In the P-type ESD protection structure of this embodiment, when performing ESD protection, the drain 800 is connected to the negative electrode as a cathode

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More