Register architecture of RISC architecture processor, register block and RISC architecture processor

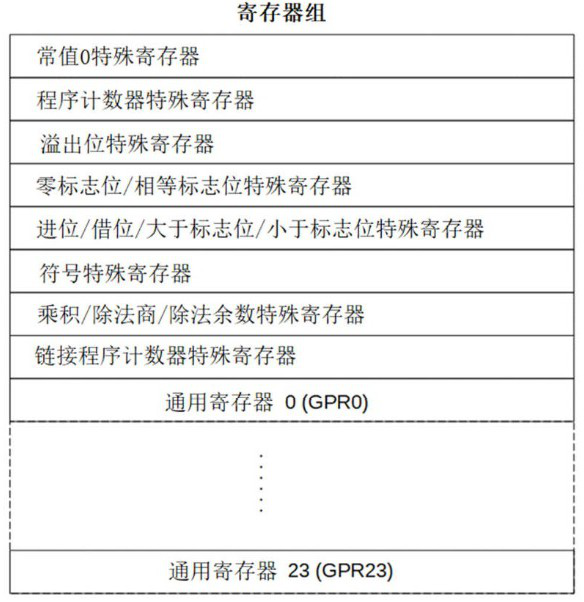

A technology of register groups and registers, which is applied in register devices, electrical digital data processing, and architectures with multiple processing units, etc., can solve the problems of processor performance degradation, increased hardware design circuit complexity, software writing complexity, etc., to achieve Reduce the type and number of instructions, reduce the difficulty and cost of implementation, and reduce the effect of types

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0123] In this embodiment, taking a program for implementing accumulation calculation as an example, the RISC architecture processor adopts a register group (REG) implementation method including the register architecture of the RISC architecture processor proposed by the present invention as a standard, and the RISC architecture processing method The device adopts the method A and method B mentioned in the above-mentioned prior art for further comparison and description.

[0124] In this embodiment, the value of the unsigned number A0+A1+A2 needs to be obtained.

[0125] In Embodiment 1, the RISC architecture processor adopts the implementation method of the register group including the register architecture of the RISC architecture processor proposed by the present invention as a standard construction, and the programming solution method is as follows:

[0126] (It should be noted that in the following embodiments, the registers are uniformly marked as Rn, n=0, 1, 2... in the...

Embodiment 2

[0151] In this embodiment, taking a program for implementing multiply-add calculation as an example, the RISC architecture processor adopts the implementation method of the register group constructed by including the register architecture of the RISC architecture processor proposed by the present invention as a standard, and the RISC architecture processor adopts The implementation method C and method D mentioned in the above-mentioned prior art are further explained in comparison.

[0152] In this embodiment, it is necessary to obtain the value of the unsigned number A*B+W.

[0153] In Embodiment 2, the RISC architecture processor adopts a register group that includes the register architecture of the RISC architecture processor proposed by the present invention as a standard construction method, and the programming solution method is as follows:

[0154] 1. Set A, B, and W to be stored in R6, R8, and R9 respectively; calculate A(R6)*B(R8) to obtain P, the lower half of P PL i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More