Method and equipment for creating time delay table of FPGA (Field Programmable Gate Array) circuit and obtaining time delay

A technology of path delay and delay, which is applied in the direction of electrical digital data processing, computer-aided design, special data processing applications, etc., can solve the problems of increased connection line delay and FPGA circuit difficulty in meeting timing constraints, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to make the above objects, features and beneficial effects of the embodiments of the present invention more clearly understood, the specific embodiments of the present invention will be described in detail below with reference to the accompanying drawings.

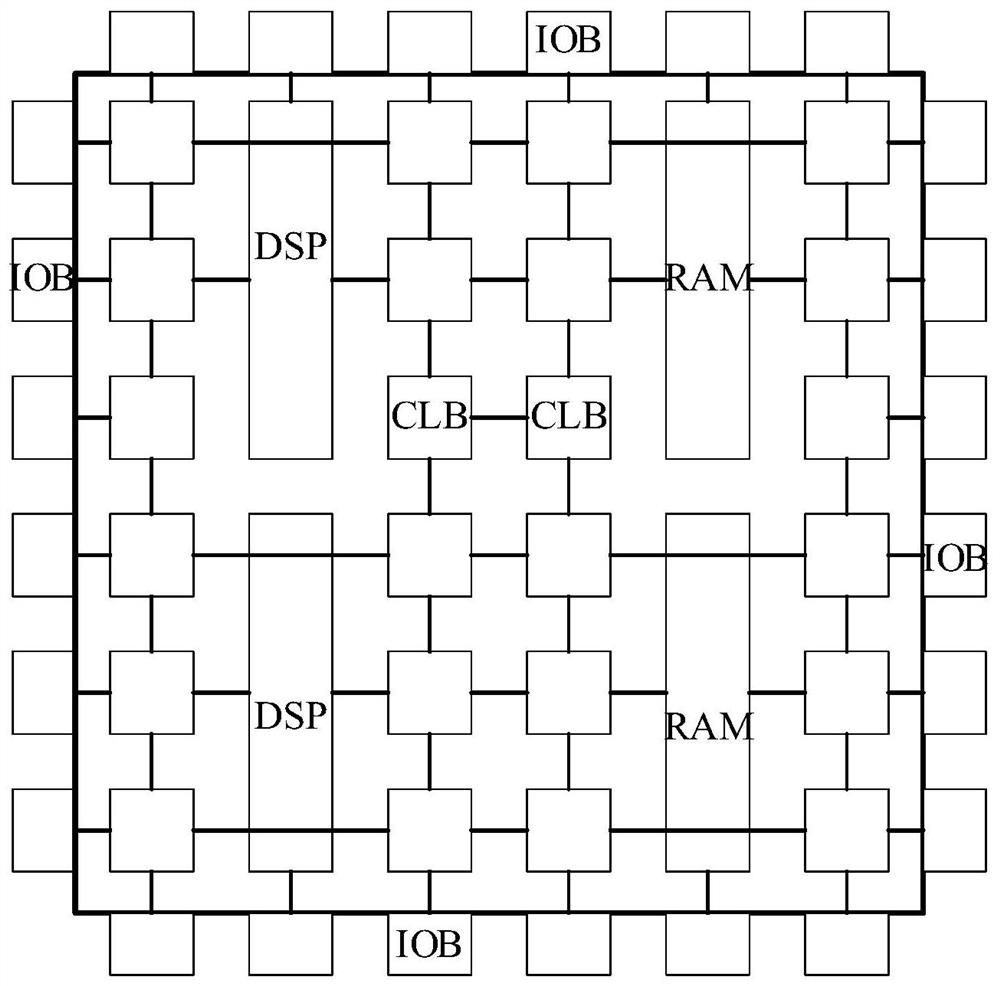

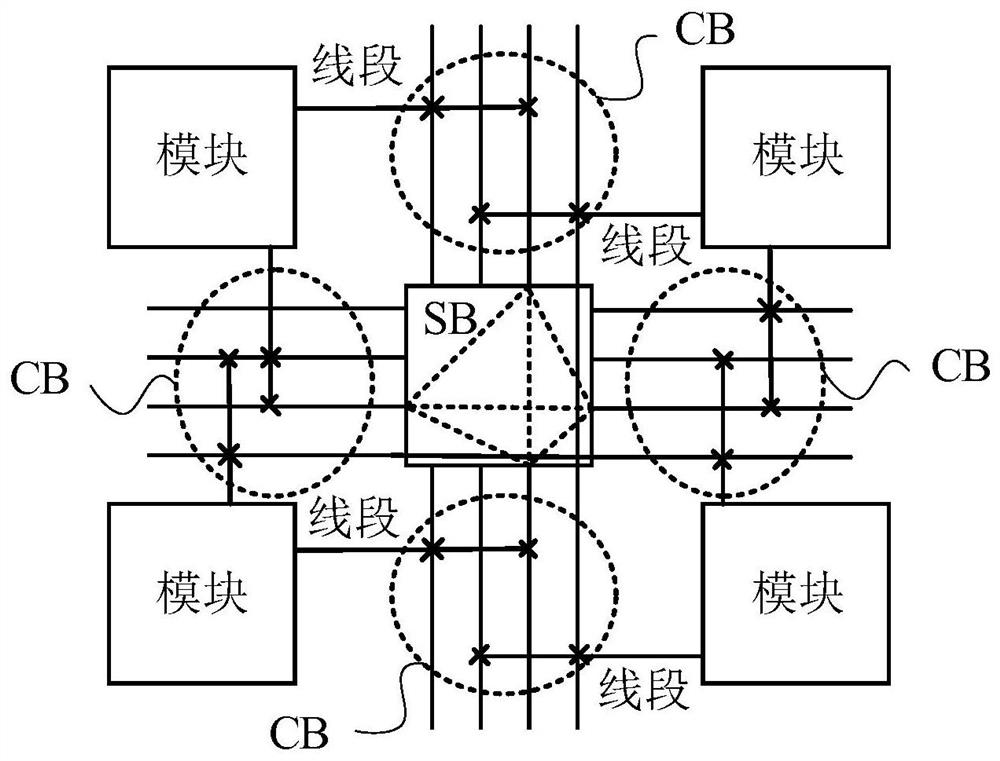

[0042] like figure 1 As shown, the FPGA chip adopts a regular array structure; the center of the array can be taken as the origin, the horizontal right and left directions are the positive and negative directions of the X axis ("X direction"), and the vertical upward and downward directions are respectively The positive and negative directions of the Y-axis ("Y-direction").

[0043] The points in the array may be modules, and the modules include CLB, random access memory (Random Access Memory, RAM), programmable input output block (IOB), digital signal processing module (Digital Signal Processor, DSP) and the like.

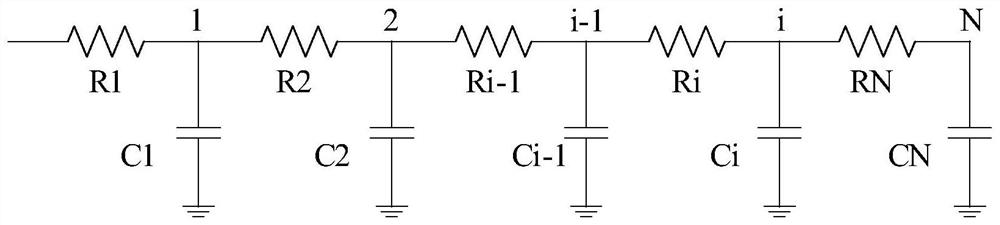

[0044] Inside the FPGA chip, the largest number is CLB, which is the most basic module; on...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More