Parameter extraction modeling method suitable for discrete device after scribing

A modeling method and discrete device technology, applied in instruments, special data processing applications, calculations, etc., can solve problems such as immature large signal models, failure analysis of new materials, and unclear defect structures, so as to improve the efficiency of circuit design, The effect of avoiding unevenness between sheets and saving research and development costs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0052] The preferred embodiments of the present invention are described below in detail with reference to the accompanying drawings, wherein the accompanying drawings constitute a part of the present application, and together with the embodiments of the present invention, serve to explain the principles of the present invention.

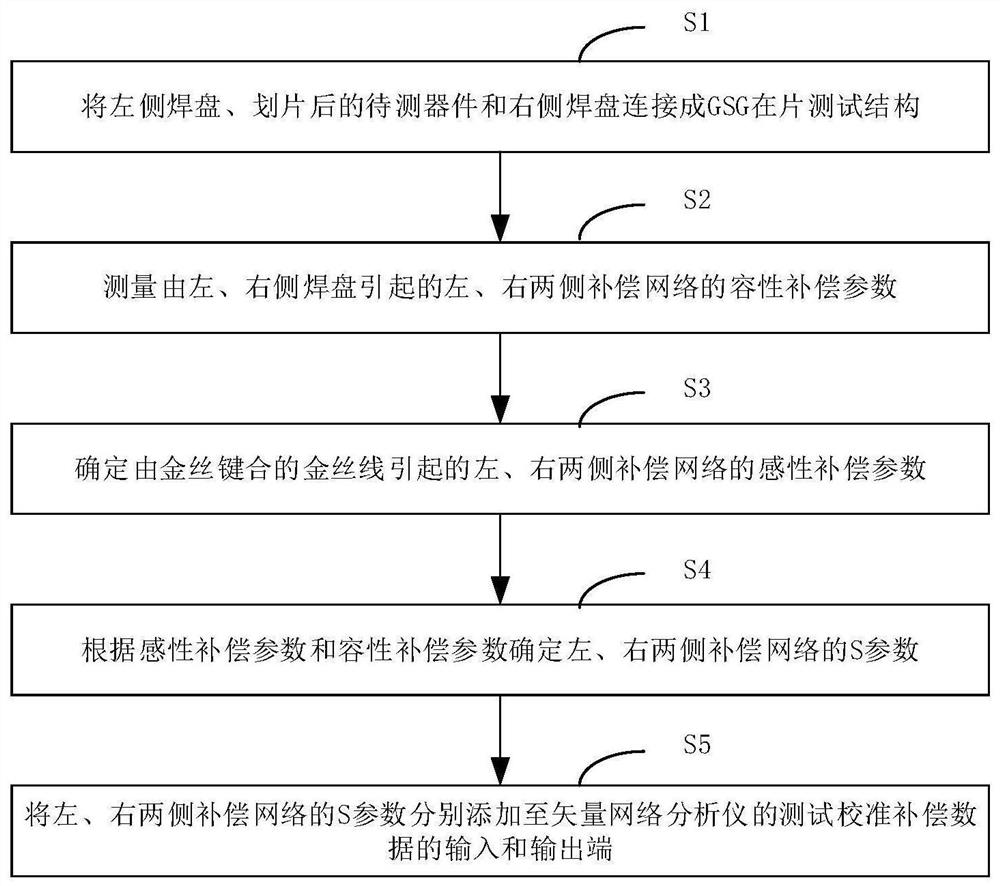

[0053] This embodiment discloses a parameter extraction modeling method suitable for discrete devices after dicing, such as figure 1 shown, including the following steps:

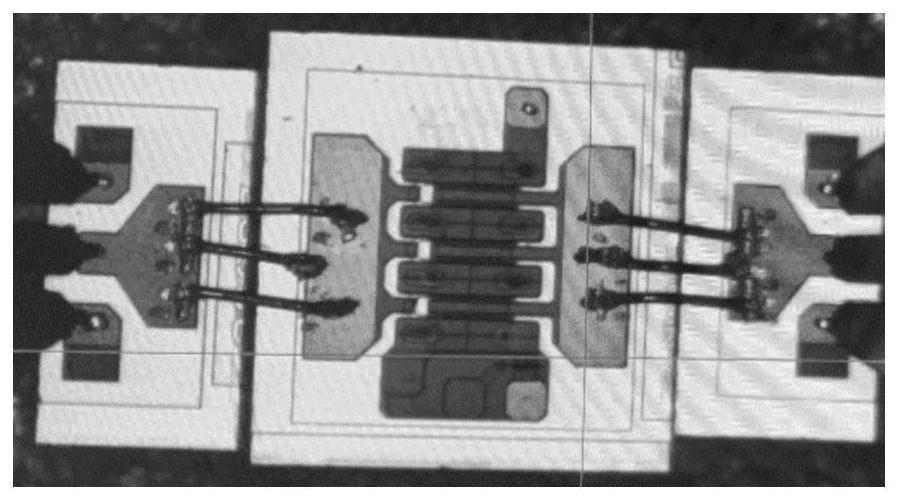

[0054]Step S1, connecting the left pad, the device under test after dicing, and the right pad by gold wire bonding to form a GSG on-chip test structure;

[0055] The device under test after dicing is a discrete device;

[0056] Specifically, the assembly sequence of the GSG (ground-signal-ground) on-chip test structure includes:

[0057] Solder the left and right pads and the device under test that connect the GSG on-chip test on the metal heat sink through solder;

[0058] Acc...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More