Semiconductor device chip scale surface assembling and packaging, and mfg. method therefor

A technology for device packaging and manufacturing methods, applied in the fields of semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of expensive, fragile wire bonding, time-consuming, etc. The effect of on-resistance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

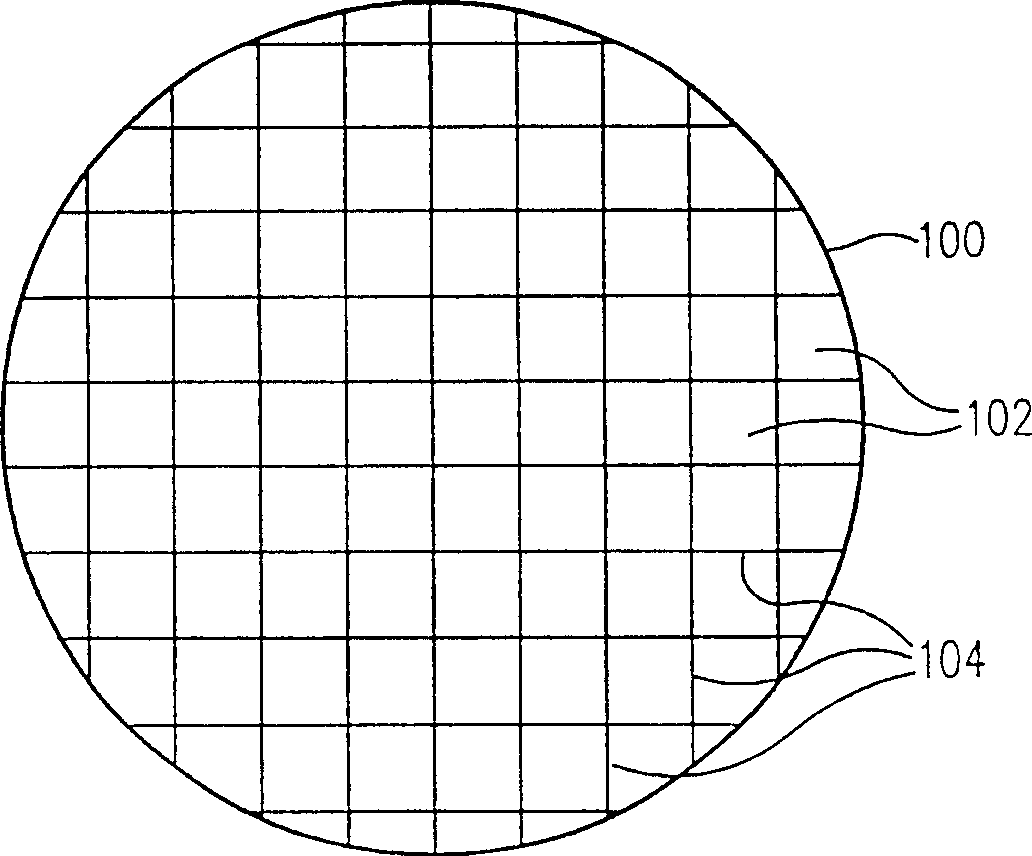

[0032] Processing of the semiconductor wafer forms a rectangular array of dies. exist figure 1 A top view of wafer 100 and die 102 is shown in . The dies are separated by an orthogonal network of scribe lines 104 , typically sawing to separate the dies 102 .

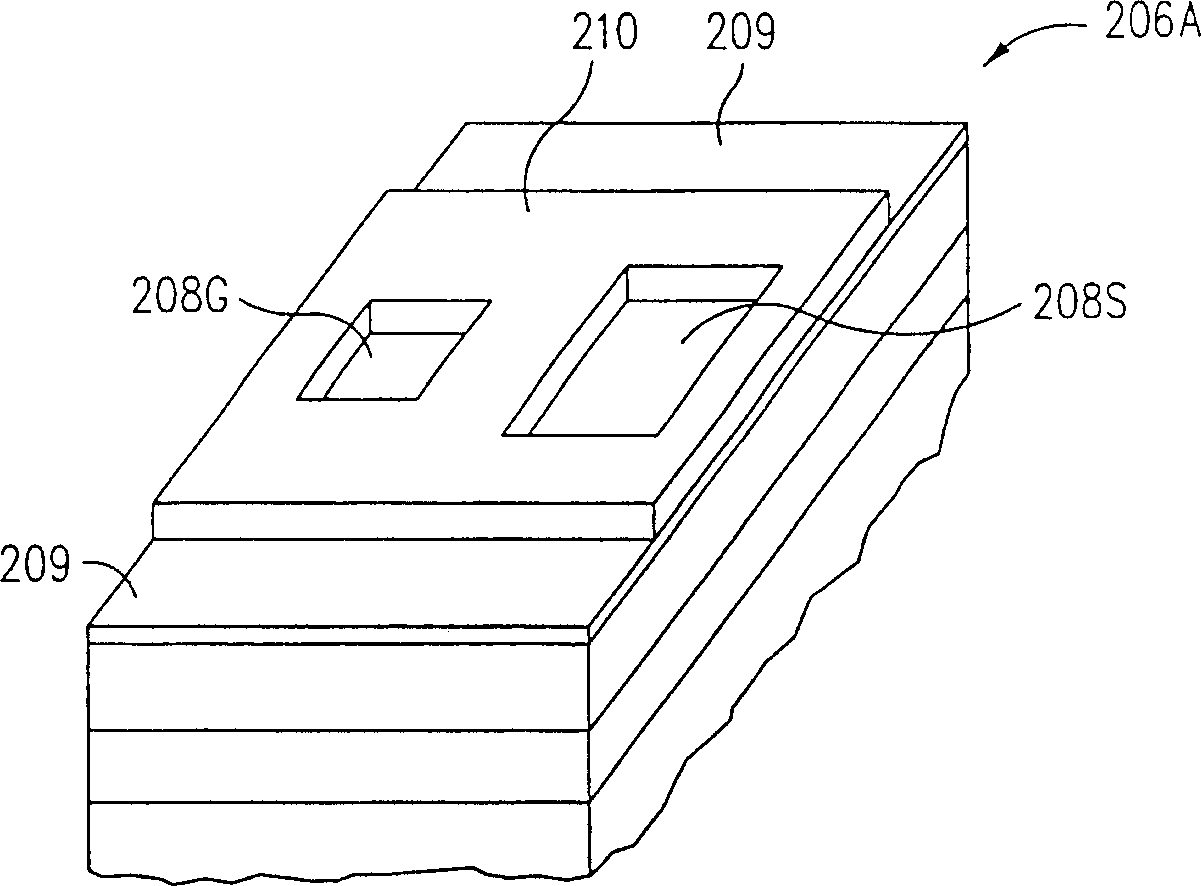

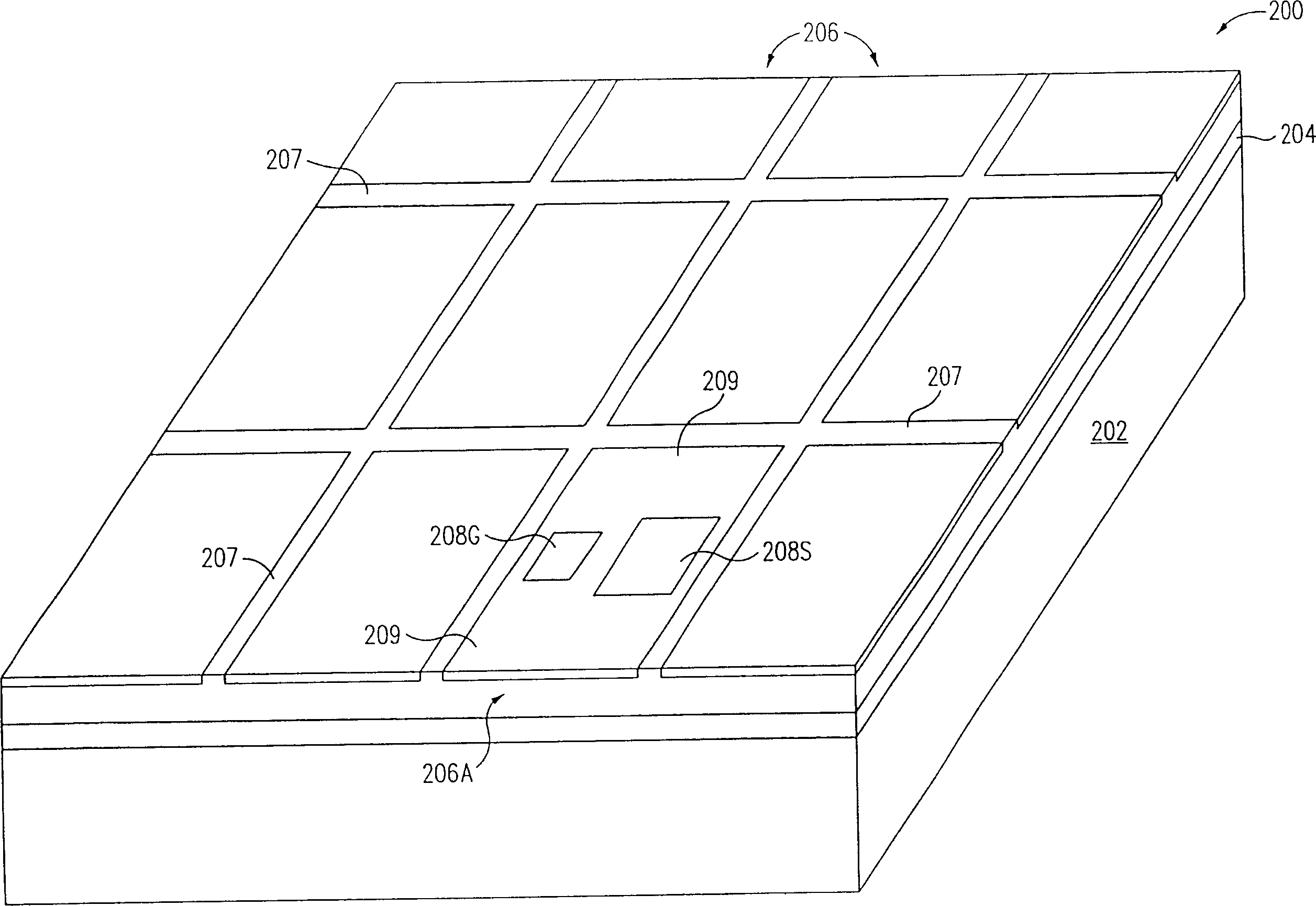

[0033] The invention is described below with reference to the packaging of a vertical power MOSFET, which typically has source and gate terminals on the front side and a drain terminal on its back side. However, it should be understood that the basic principles of the present invention can be used to manufacture packages for any type of semiconductor die with terminals on the front and back, including diodes, bipolar transistors, junction field effect transistors (JFETs), and integrated circuits of various types. (IC). As used herein, "front" of a die refers to the side of the die that contains the electrical components and / or most of the connection pads; "back" refers to the quilt side of the die.

[0034] A semicon...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More