Method of forming light doped drain electrode using side wall polymer grid structure

A lightly doped drain and gate structure technology, applied in electrical components, semiconductor/solid-state device manufacturing, circuits, etc., can solve problems such as difficulty in manufacturing, lower component yield and electrical quality, and affect component stability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

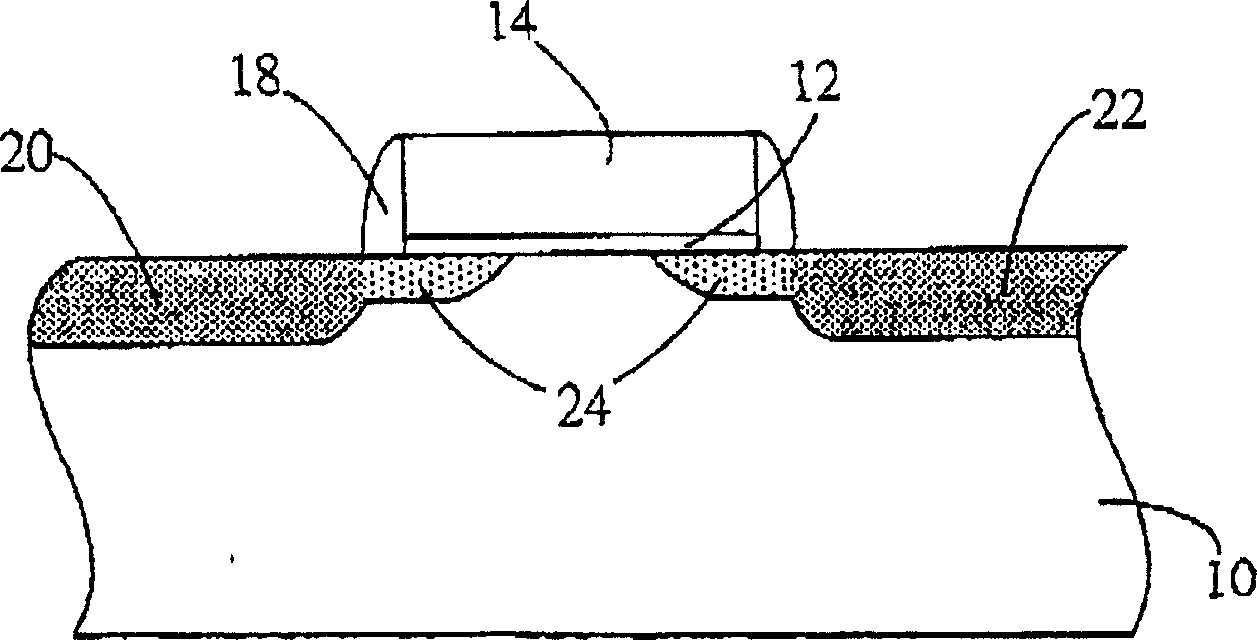

[0013] The present invention is a sidewall polymer (sidewall) pre-formed on the substrate, so that after the shallow ion doping area is formed, the shallow ion doping area only diffuses laterally to the substrate under the sidewall polymer during thermal processing When forming the LDD structure, the length of the channel can be accurately controlled, effectively solving the common short channel effect in the semiconductor process.

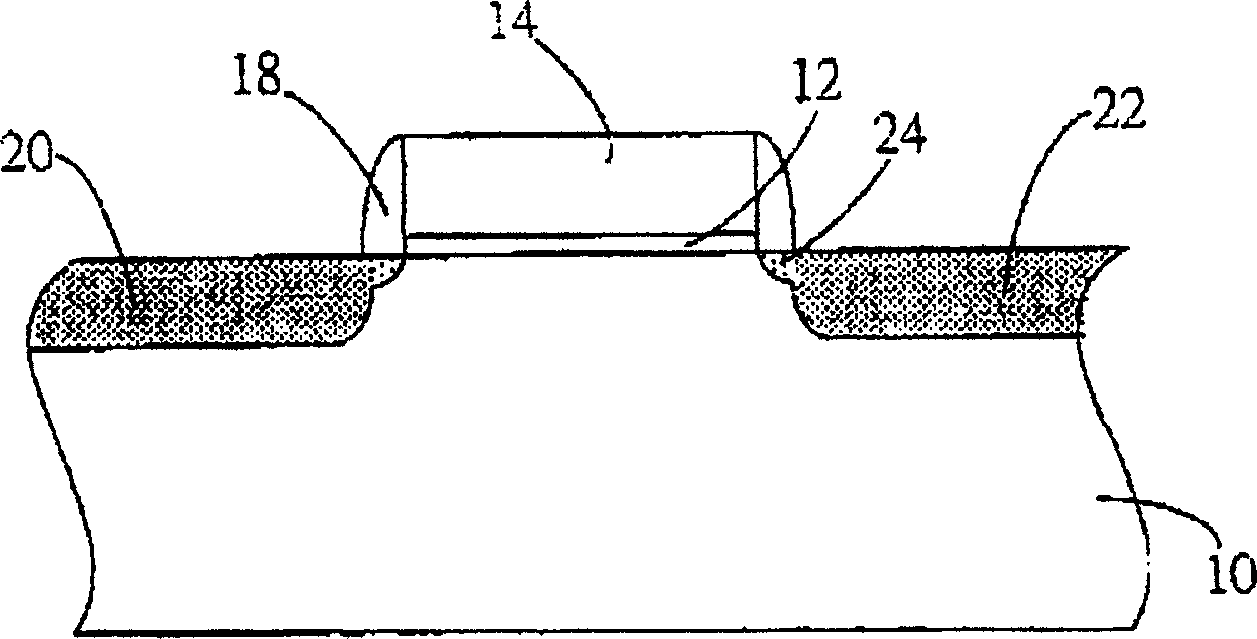

[0014] Figure 2A to Figure 2F These are schematic cross-sectional schematic diagrams of each step of manufacturing LDD in a preferred embodiment of the present invention; as shown in the figure, the manufacturing method of the present invention includes the following steps:

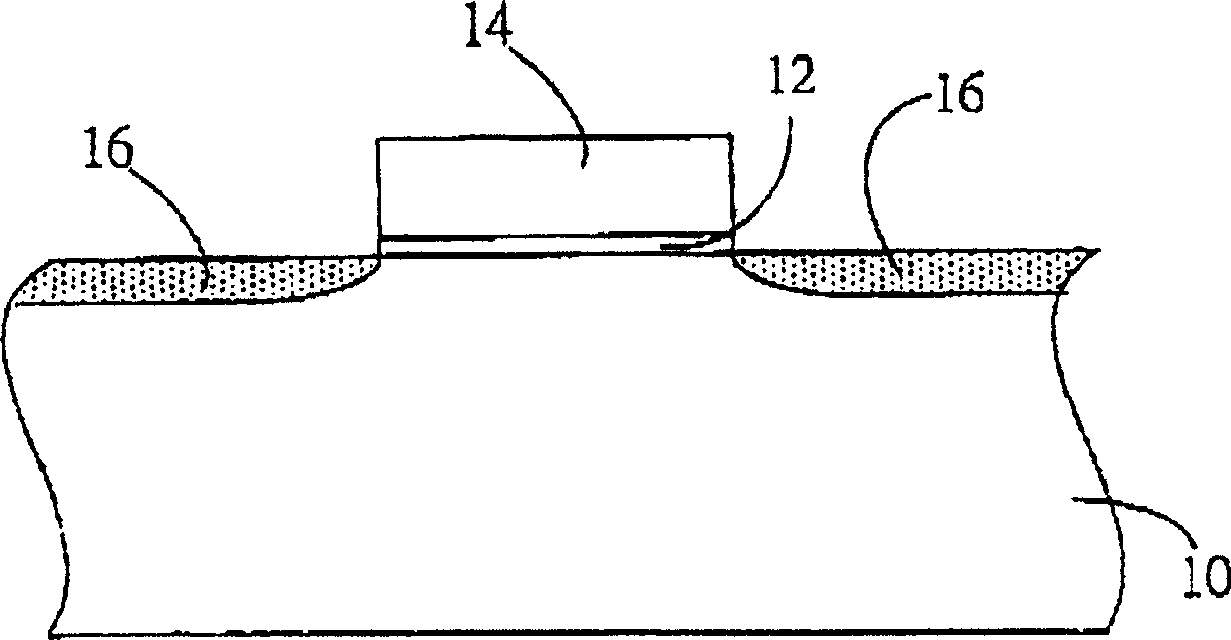

[0015] First, see Figure 2A As shown, a gate oxide layer 22 is formed by thermal oxidation on a substrate 20; then, a polysilicon layer 24 is deposited on the gate oxide layer 22 by chemical vapor deposition (CVD), and the polysilicon is etched away using a photolithography te...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More