Method for producing embedded DRAM unit array with selected transistor

A technology for selecting transistors and cell arrays, applied in information storage, static memory, digital memory information, etc., can solve the problems of conflicting process requirements, difficulty in reliability, and difficulty in producing high-performance memory devices, so as to improve performance, The effect of reducing the size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Before describing the present invention, the existing semiconductor memory device is firstly introduced, which is helpful for understanding the present invention.

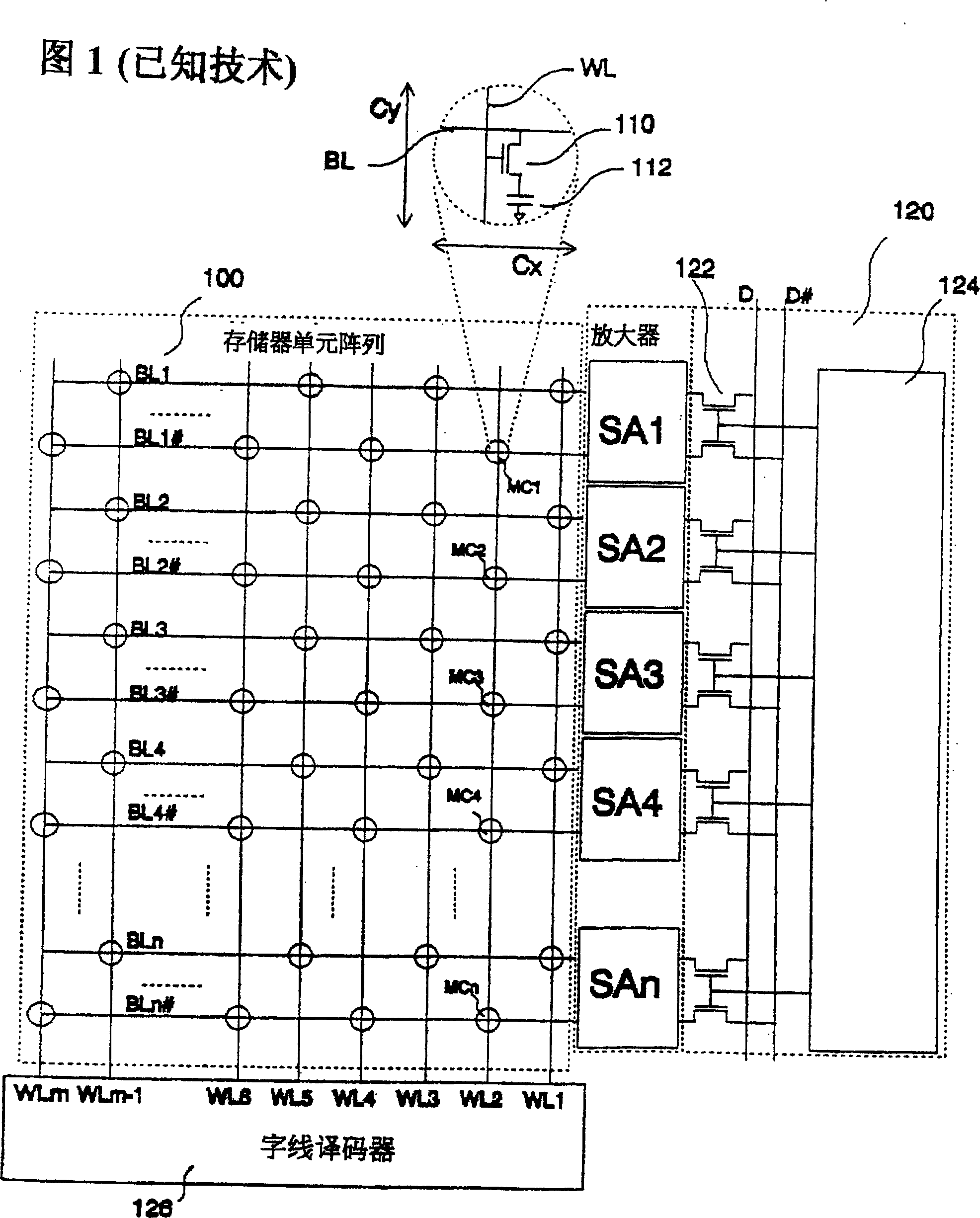

[0057] Fig. 1 shows the structure of the memory cell array of the existing DRAM in two ways of electronic circuit and topological diagram. The memory cell array 100 includes several pairs of bit lines BL1, BL1#, BL2, BL2#, BL3, BL3#, . . . , BLn, BLn# (n is an integer) parallel to each other, and several pairs of The word lines WL1 , WL2 . . . WLm (m is an integer) cross vertically. At these intersections, memory cells MC1, MC2, . . . , MCn are respectively arranged. The memory cells are represented by individual circles in the memory cell array 100 shown in FIG. 1 . Each memory cell includes a field effect switching transistor 110 and a memory cell capacitor 112 . The bit line BL is connected to the drain of the transistor 110 . The gate electrode of the transistor 110 is connected to the word line WL. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More