Method for forming self alignment contact window

A self-aligned contact and contact area technology, applied in the direction of electrical components, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve problems such as short circuits

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

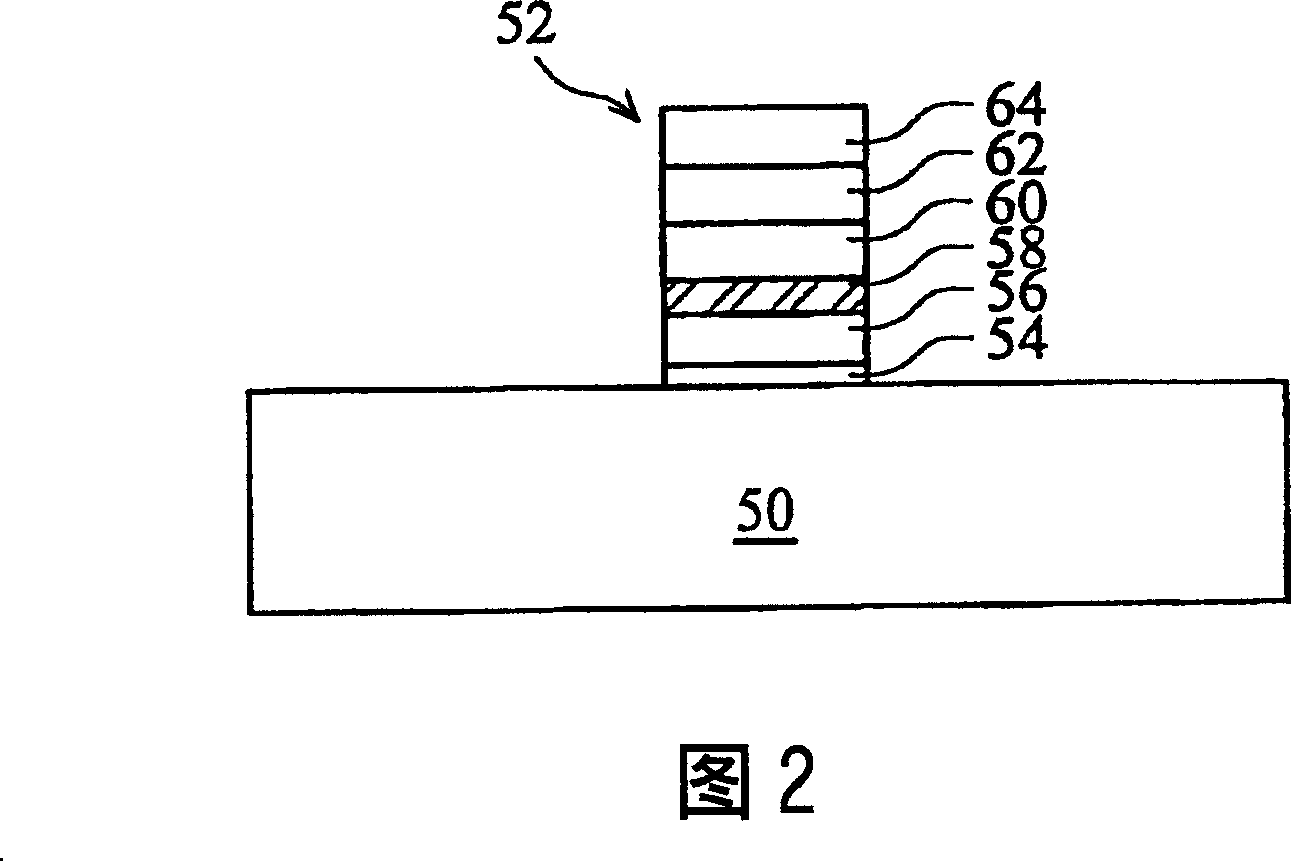

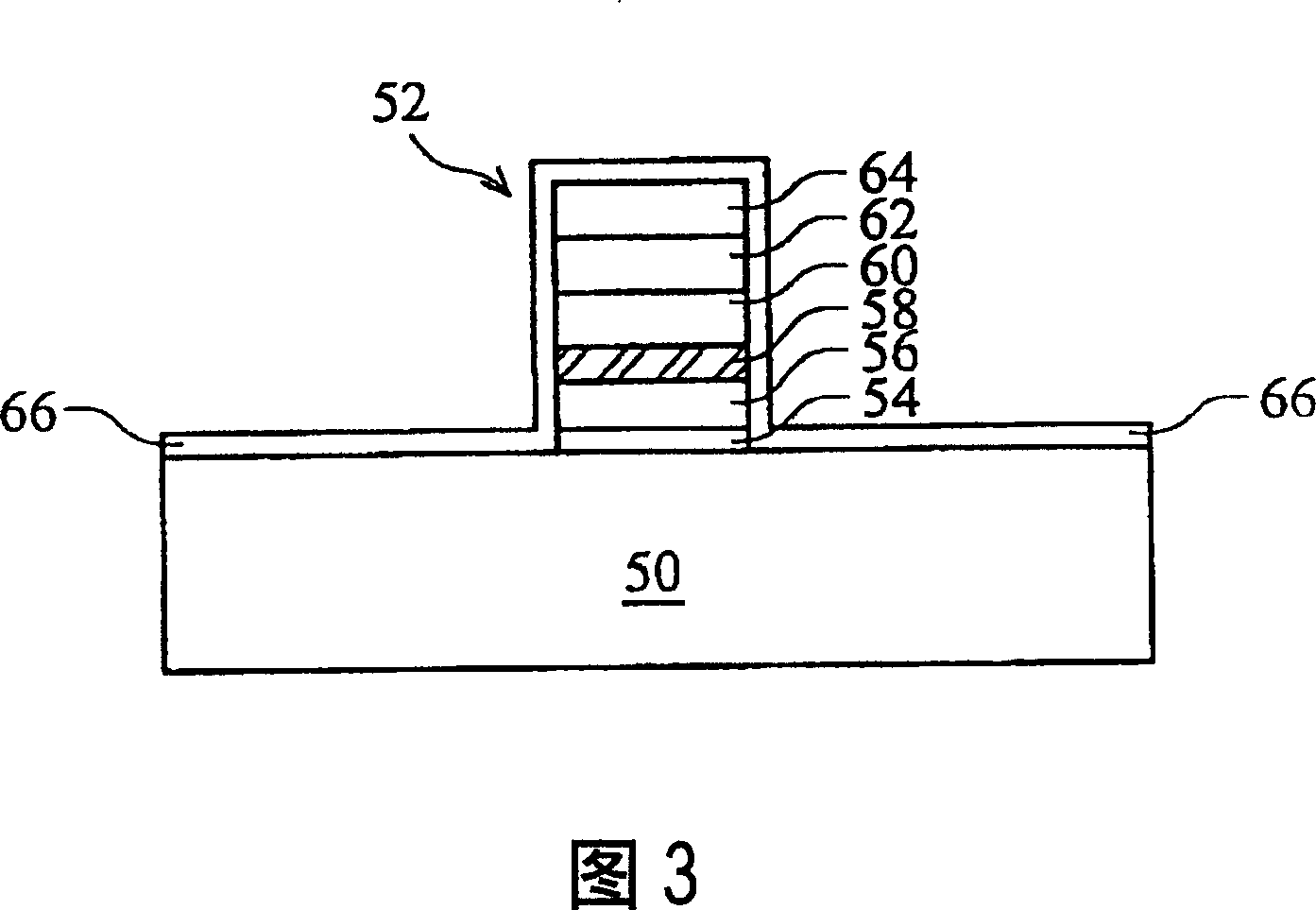

[0044] 2-8 show an embodiment of the self-aligned contact forming method of the present invention. Referring to FIG. 2 , a semiconductor substrate 50 is provided, and a gate stack structure 52 is formed on the semiconductor substrate 50 , and a source / gate pair and a channel can be formed in the semiconductor substrate at this stage as required. The stacked gate structure 52 includes a gate insulating layer 54 , a second metal layer 60 and an interlayer dielectric layer 58 formed between the first metal layer 56 and the second metal layer 60 to provide electrical insulation between the two metal layers. In one embodiment, the gate insulating layer 54 is made of silicon oxide, the first metal layer 56 includes polysilicon, and the second metal layer 60 includes a refractory metal layer. In another embodiment, the third metal layer 62 formed on the second metal layer 60 including polysilicon includes tungsten suicide. The third metal layer 62 may enhance the conductivity of the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More