Semiconductor device, manufacturing method thereof, and electronic device

A manufacturing method and semiconductor technology, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electric solid-state devices, etc., can solve the problems of gate and source/drain breakdown voltage reduction, so as to avoid breakdown voltage reduction, performance and good The effect of rate improvement, performance improvement and yield rate improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

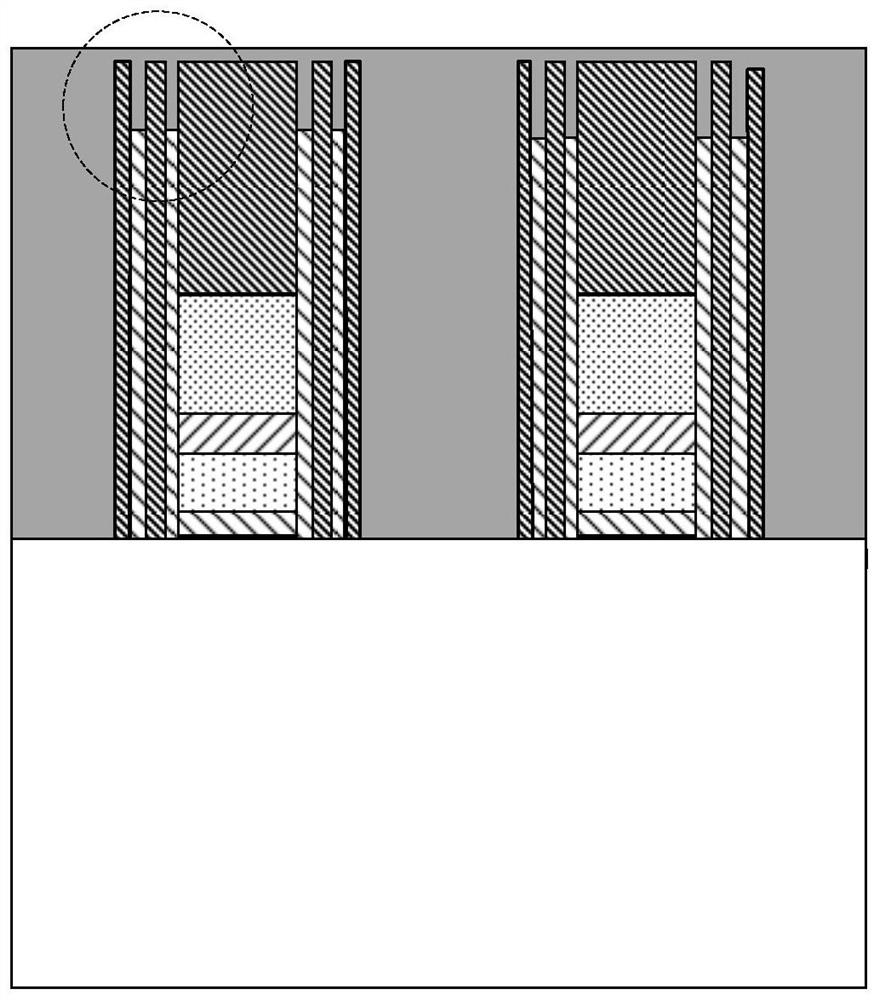

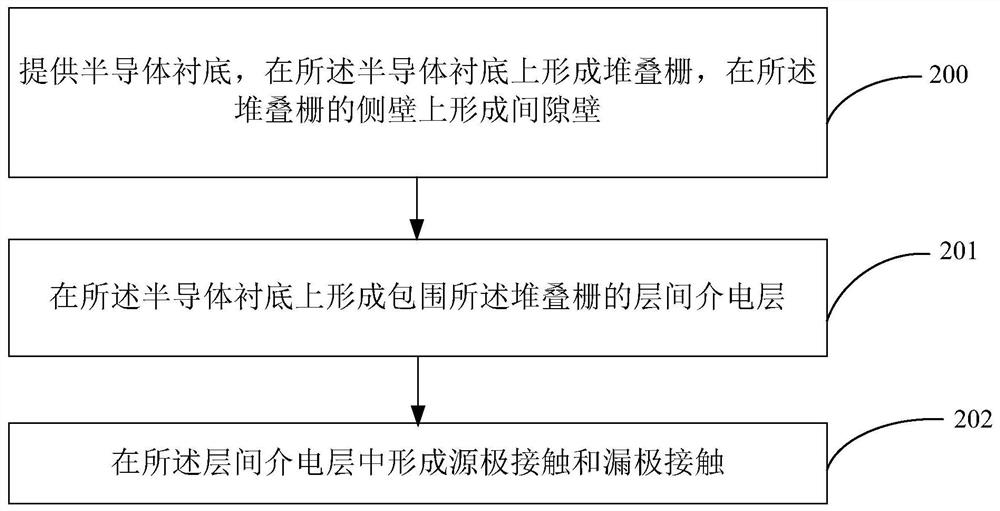

[0054] The following will refer to 3A to 17A as well as 3B to 17B A method for fabricating a semiconductor device according to an embodiment of the present invention is described in detail, wherein 3A to 17A A cross-sectional view along the direction of the active region of the semiconductor device obtained by sequentially implementing the steps of the method for fabricating a semiconductor device according to an embodiment of the present invention; 3B to 17B A cross-sectional view of the semiconductor device along the direction of the isolation structure obtained by sequentially performing various steps in the method for fabricating a semiconductor device according to an embodiment of the present invention is shown.

[0055] In this embodiment, the fabrication method of the semiconductor device proposed by the present invention is described in detail by taking the fabrication of the source-drain contacts of the NOR memory as an example. Please refer to the above drawing...

Embodiment 2

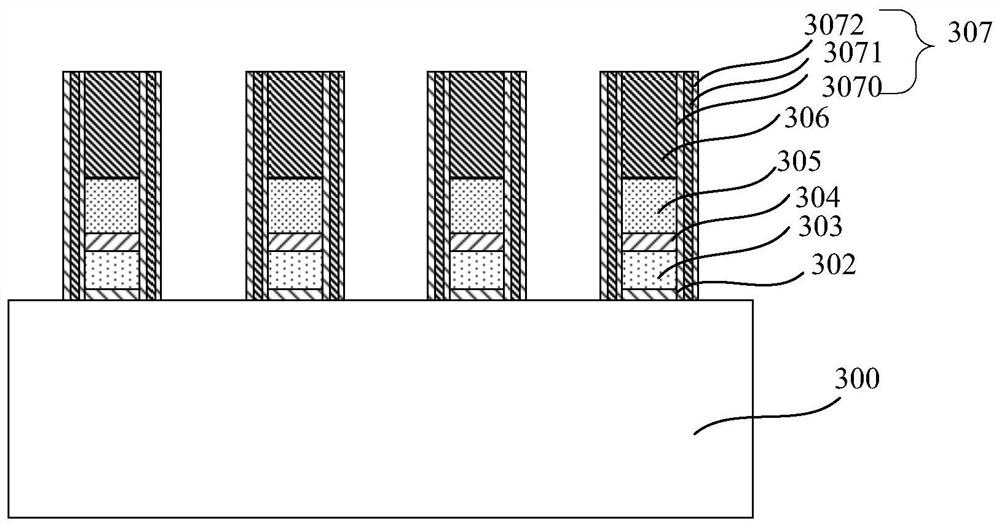

[0101] The present invention also provides a semiconductor device fabricated by the above method, such as Figure 17A and Figure 17B As shown, the semiconductor device includes: a semiconductor substrate 300, on which a stacked gate is formed, and a spacer 307A is formed on the sidewall of the stacked gate 300; on the semiconductor substrate 300 An interlayer dielectric layer surrounding the stacked gate is formed; a source contact 315A and a drain contact 315B are formed in the interlayer dielectric layer; wherein, the top region of the spacer 307A is entirely connected to the interlayer The dielectric layer is composed of materials with etch selectivity.

[0102] The isolation structure 301 in the semiconductor substrate 300 may be a shallow trench isolation (STI) structure or a localized silicon oxide (LOCOS) isolation structure, which may be formed by methods commonly used in the art to define and separate active regions. As an example, a shallow trench isolation (STI) ...

Embodiment 3

[0108] Yet another embodiment of the present invention provides an electronic device including a semiconductor device and an electronic component connected to the semiconductor device. Wherein, the semiconductor device includes: a semiconductor substrate, a stacked gate is formed on the semiconductor substrate, and a spacer is formed on a sidewall of the stacked gate; and a space surrounding the stack is formed on the semiconductor substrate an interlayer dielectric layer of the gate; a source contact and a drain contact are formed in the interlayer dielectric layer; wherein, the top region of the spacer is entirely composed of etch selectivity with the interlayer dielectric layer material composition.

[0109] Wherein, the semiconductor substrate can be at least one of the following materials: Si, Ge, SiGe, SiC, SiGeC, InAs, GaAs, InP or other III / V compound semiconductors, and also includes multilayers composed of these semiconductors The structure or the like may be silico...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More