Method for forming integrated circuit with MONOS element and mixed signal circuit

A mixed-signal, integrated circuit technology, applied in the manufacturing of circuits, electrical components, semiconductor/solid-state devices, etc., can solve the complex and difficult problems of single-chip systems, reduce manufacturing process steps, reduce leakage current, and avoid reliability. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

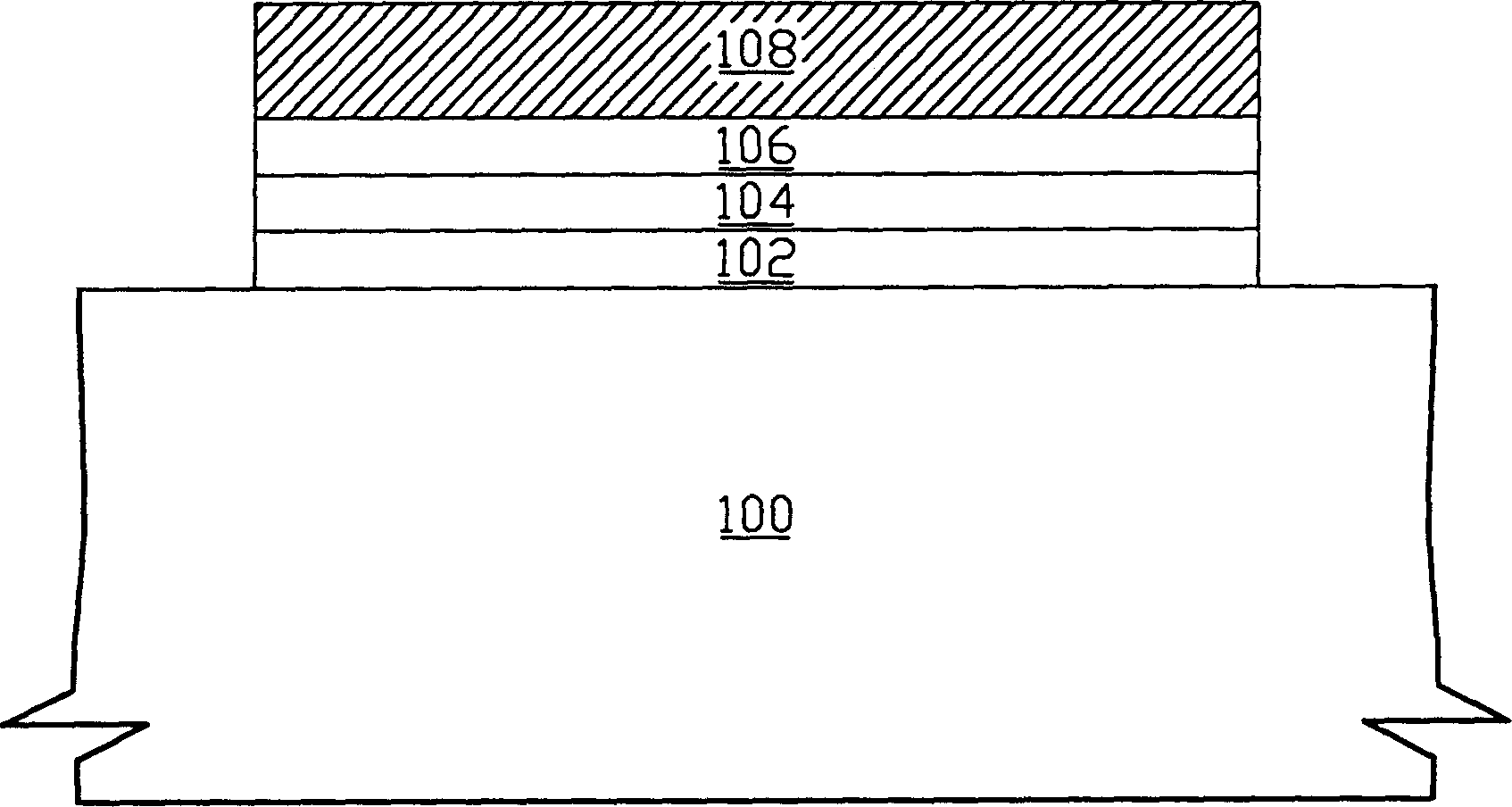

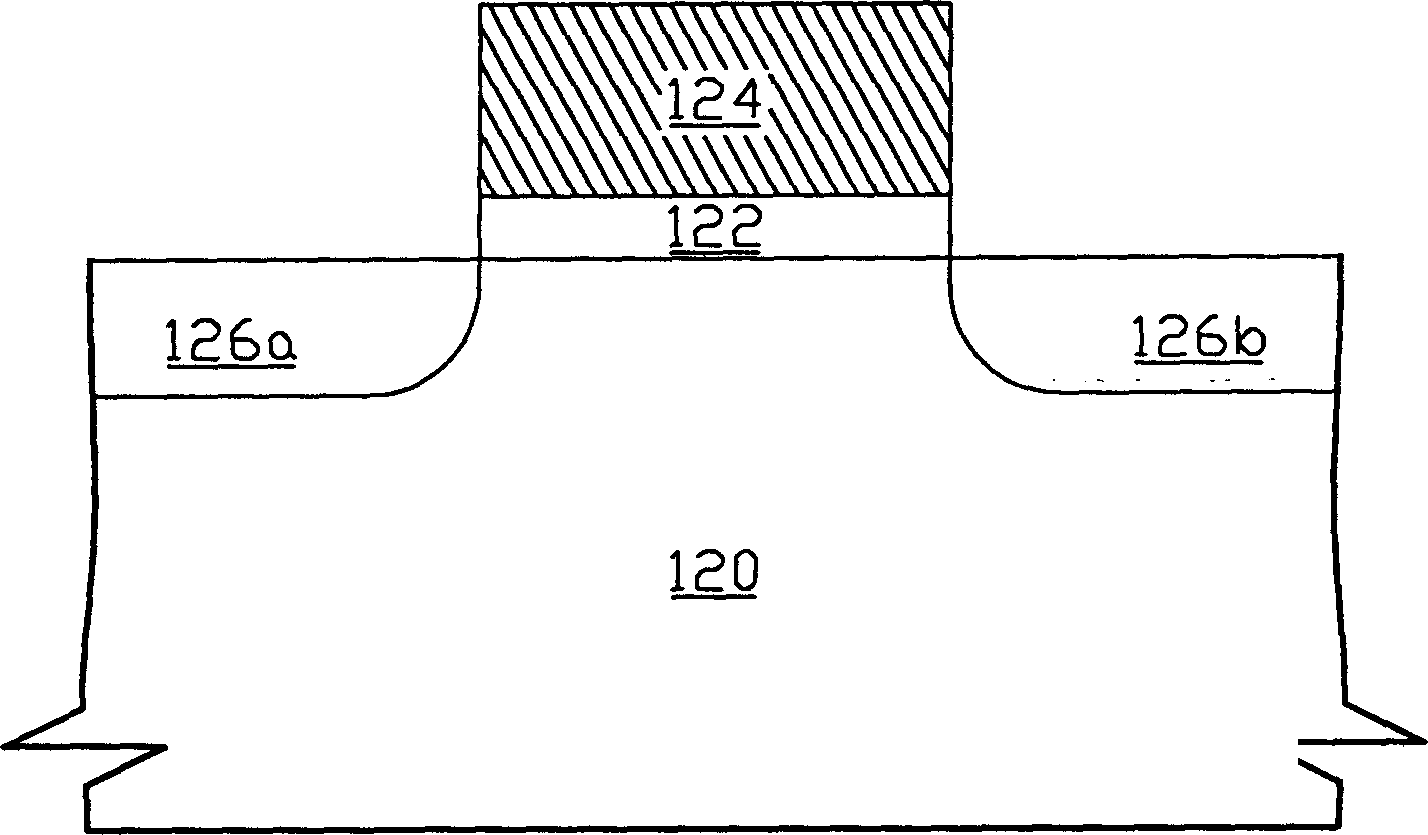

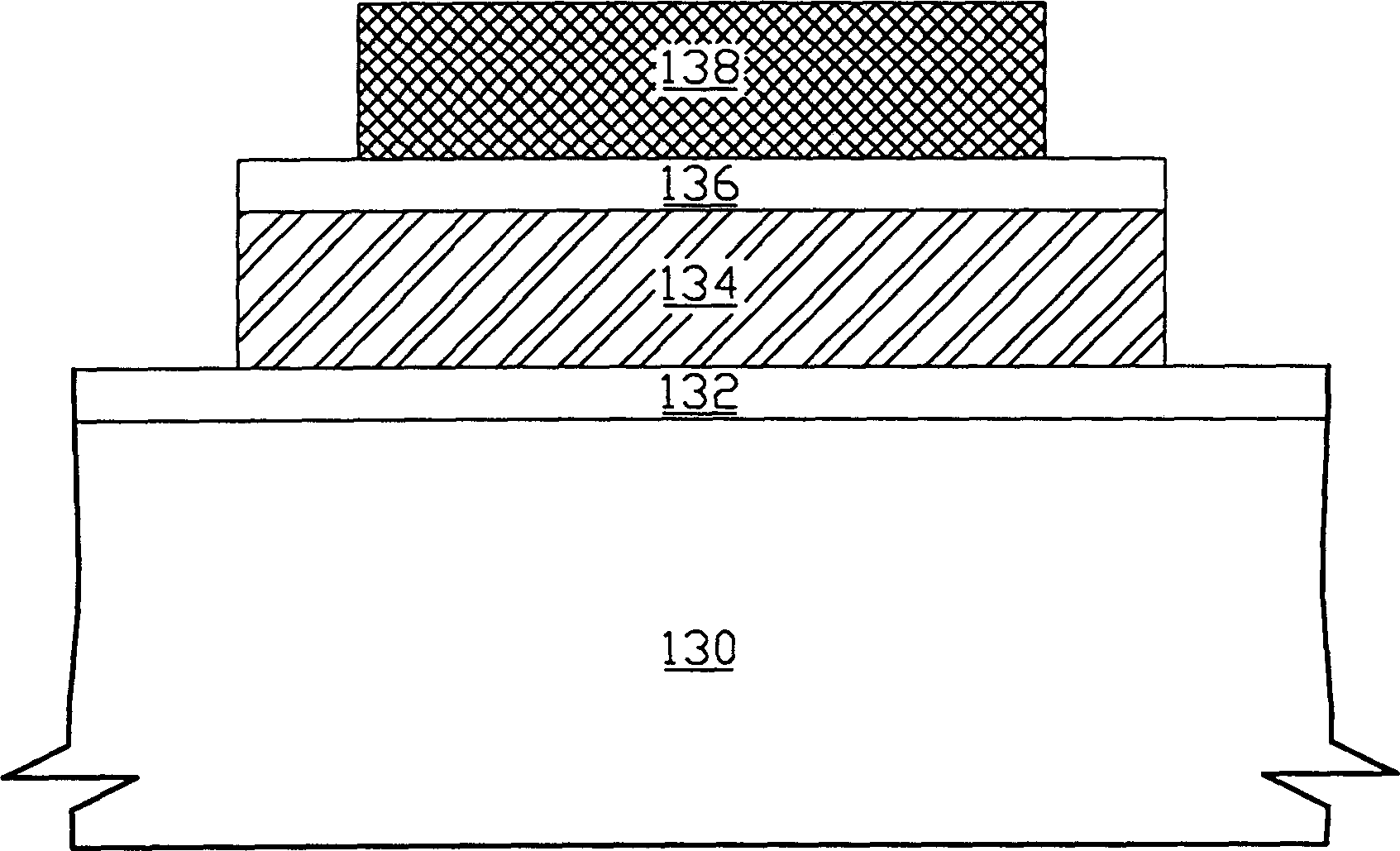

[0021] It should be noted here that the manufacturing process steps and structures described below do not include a complete manufacturing process. The present invention can be implemented by various integrated circuit fabrication process technologies, only those fabrication process technologies required for an understanding of the present invention are mentioned here. The following will be described in detail based on the accompanying drawings of the present invention. Please note that the illustrations are in simple form and not drawn to scale, and the dimensions are exaggerated to facilitate understanding of the present invention.

[0022] refer to Figure 2A As shown, a substrate 200 is shown, and the substrate 200 includes at least one memory cell region (Array Region) for forming MONOS storage and a peripheral region (Periphery Region) for forming logic elements. The substrate 200 at least includes a silicon substrate with a lattice orientation, but is not limited to a...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More