Semiconductor storage, semiconductor device and semiconductor device control method

A semiconductor and memory technology, which is applied in the field of semiconductor memory and can solve the problems of the memory cell being unable to be located, having large noise, and being unable to provide

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

[0086] Specific embodiments of the semiconductor memory element, semiconductor memory, and control method of the present invention are described in detail below with reference to the accompanying drawings. In order to simplify the description, the part of the semiconductor memory will be explained, but in actual operation, these functions are also obtained for the memory combined with contacts and peripheral circuits.

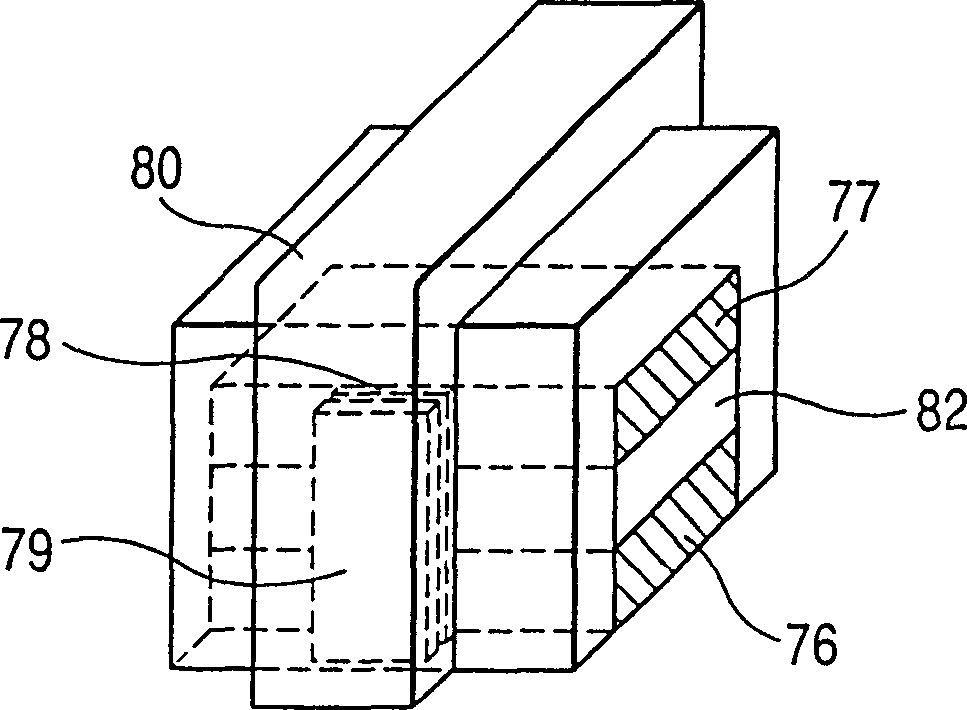

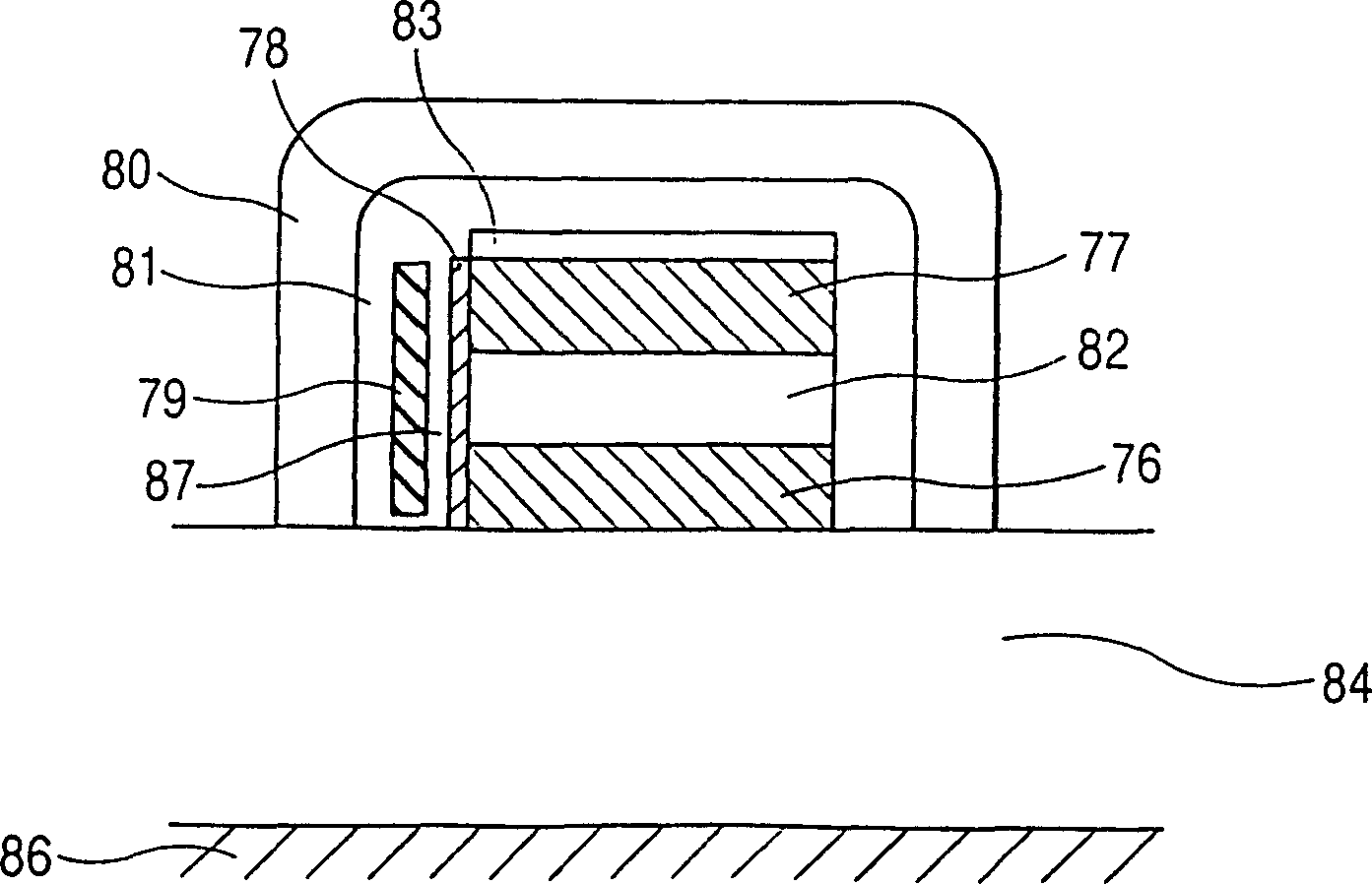

[0087] Figure 1(a) and 1(b) is a structural diagram of the semiconductor memory element of the first embodiment of the present invention. Figure 1(a) is a top slope view. Fig. 1(b) is a cross-sectional view. The source 76 and the drain 77 are regions made of N-type polysilicon with a high impurity concentration. Between the source region 76 and the drain region 77 SiO 2 insulating film 82 . In this SiO 2 On the side surface of the insulating film 82, a channel 78 composed of P-type polysilicon with a thickness of 20 nm and a width of 150 nm is formed. T...

no. 2 example

[0093] Figure 15(a) and 15(b) is a structural diagram of a memory cell according to another embodiment of the present invention. Source 1 and drain 2 are regions made of N-type polysilicon with a high impurity concentration. SiO was fabricated between the source region 1 and the drain region 2 2 insulating film 7. In SiO 2 On the side surface of the insulating film 7 is formed a channel 3 composed of non-doped polysilicon with a width of 20 nm and a thickness of 10 nm. The charge trap region 4 is made of a plurality of polysilicon grains with an average size of 6 nm, and is isolated by an insulating film. Channel 3 and charge trap region 4 via SiO 2 The insulating film 6 is connected to the gate electrode 4 . The distance between the gate electrode and the charge trap region 4 was set at 30 nm. This component is housed in SiO 2 Insulation film 8. Unless there is a special limitation, in the following embodiments, the placement points of the components on the insulat...

no. 3 example

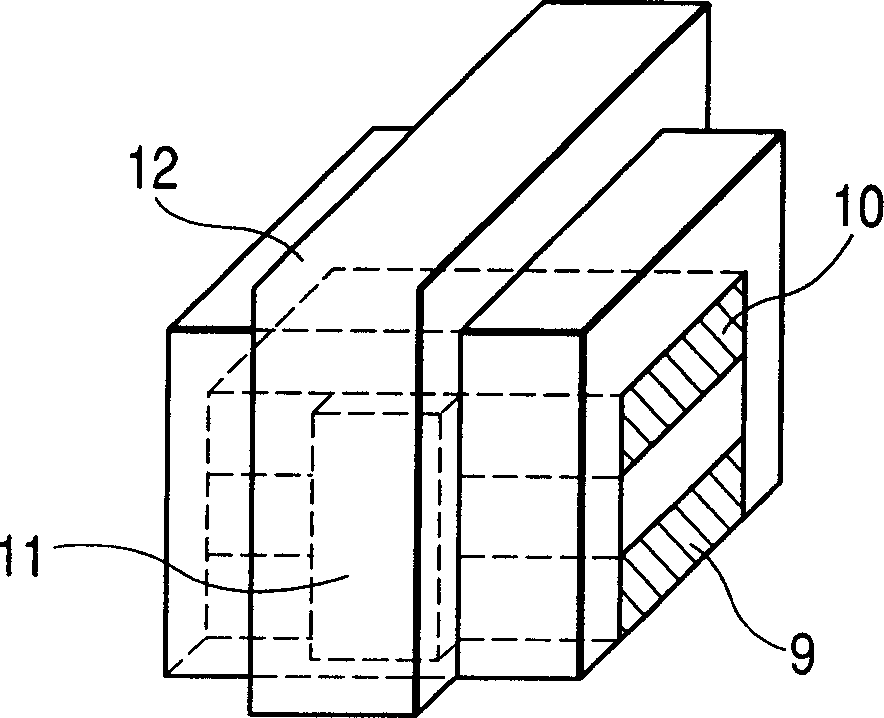

[0096] Figure 2(a) and 2(b)A third embodiment of the invention is shown. This embodiment differs from the second embodiment only in that the channel and the charge trap region 11 are integrated in one unit, and the channel 11 is formed on both sides of the source 9 and the drain 10 . The material of the channel and the charge trap region 11 is a thin non-doped polysilicon layer with an average thickness of about 3nm. In this embodiment, in order to provide a small structure suitable for room temperature work that can be manufactured with a simple process, the potential fluctuations in the polysilicon thin layer with an average thickness of less than 5 nm are used, and the channels and charge trap regions are used in the thin film ( 11) in the natural formation. The crystal grain size in this embodiment is about 3nm, so that the size can be kept within about 10nm even in the lateral direction, and the size of each charge trap region is about the same (10nm).

[0097] One f...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More