Clock synchronizing semiconductor memory equipment

A storage device, semiconductor technology, applied in information storage, static memory, digital memory information, etc., can solve problems such as inability to achieve delay, impossibility of stable operation, and allowable reduction in efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

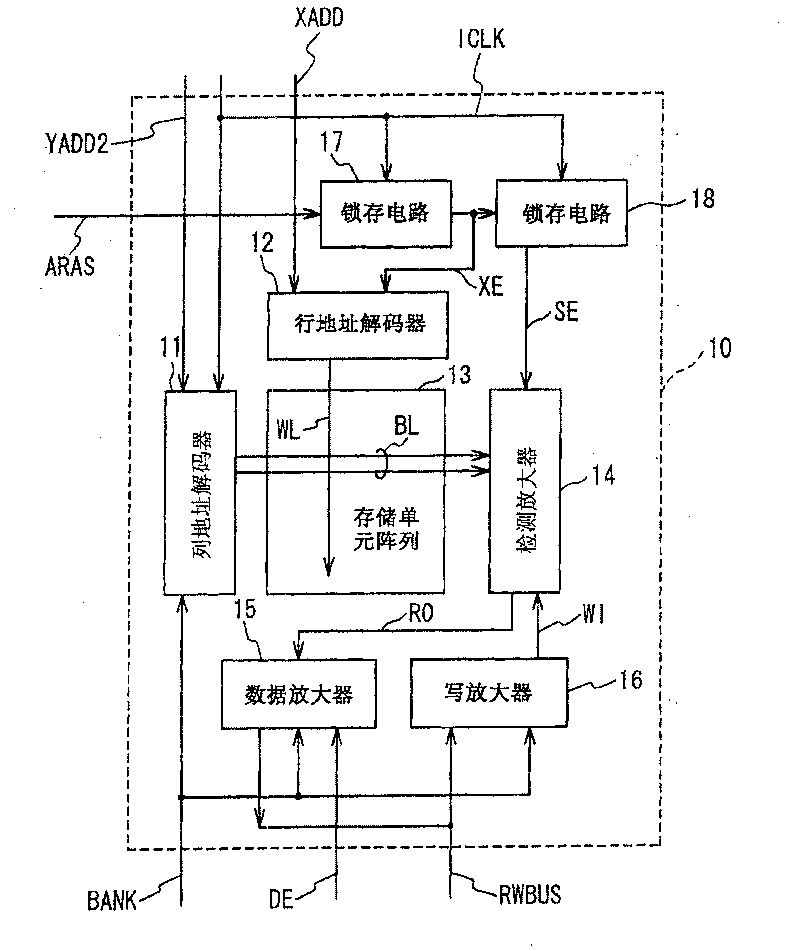

[0051] A clock synchronization type semiconductor memory device of the present invention is described below.

[0052] Figure 6 Denotes a bank circuit and a clock data storage section 31 provided as a common circuit section in the clock synchronization type semiconductor memory device according to the embodiment of the present invention. A clock synchronization type semiconductor memory device generally includes a plurality of banks, and a circuit for controlling the plurality of banks is commonly provided for the banks. Such examples are well known to those skilled in the art and will not be shown here. Although the clock data storage section 31 is provided for the common circuit section, it is assumed in this embodiment because the clock data storage circuit 31 is provided for each bank.

[0053] The clock data storage section 31 includes registers to store clock data representing the frequency of an external clock signal. In this example, clock data such as code 1 or cod...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com