Simulation apparatus and method of designing semiconductor integrated circuit

An analog device and integrated circuit technology, applied in the layout/wiring steps, low-power design field, can solve the problems that integrated circuits cannot ignore the analog speed, increase analog-return processing, etc., and achieve power consumption design and low power consumption design Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

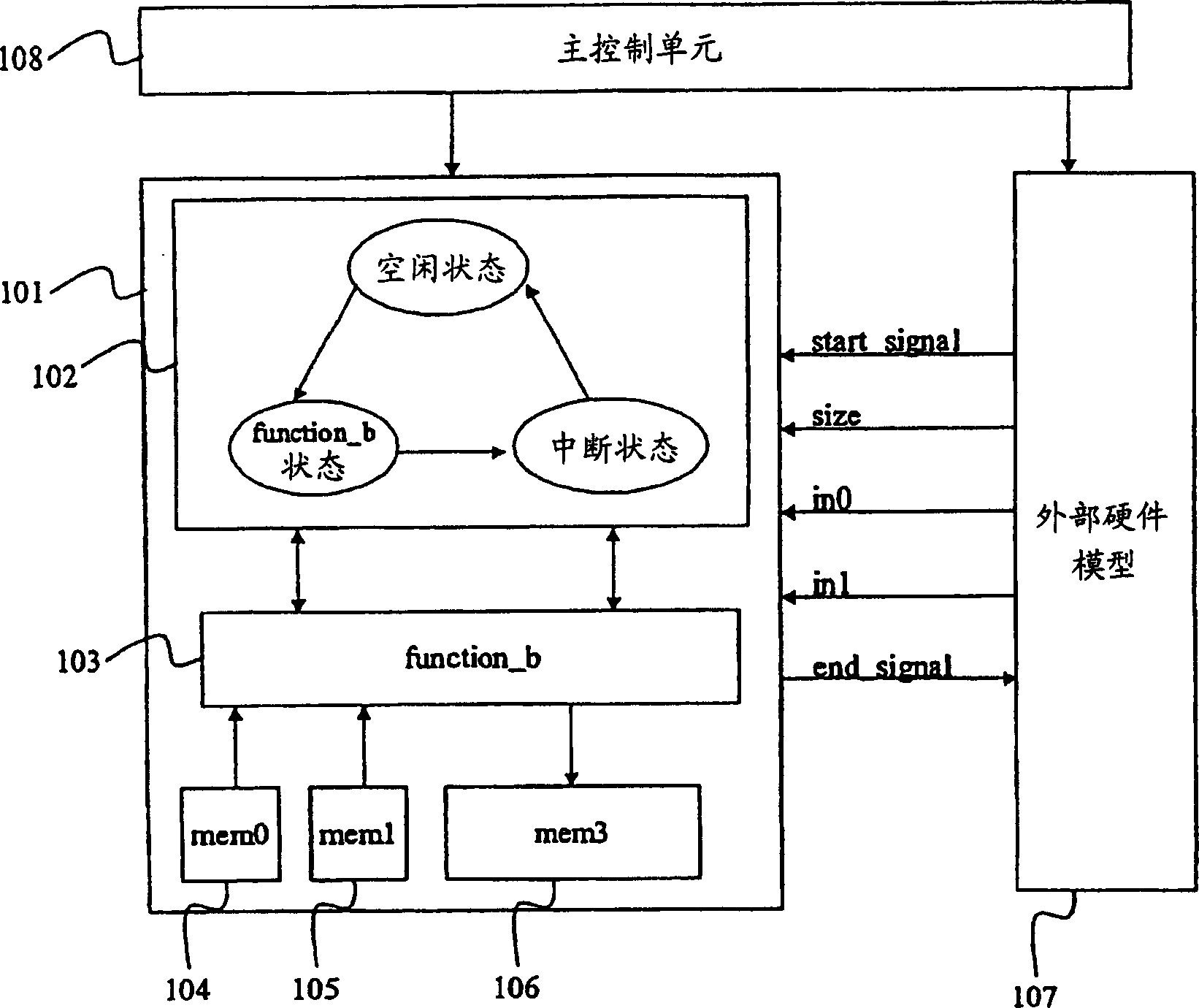

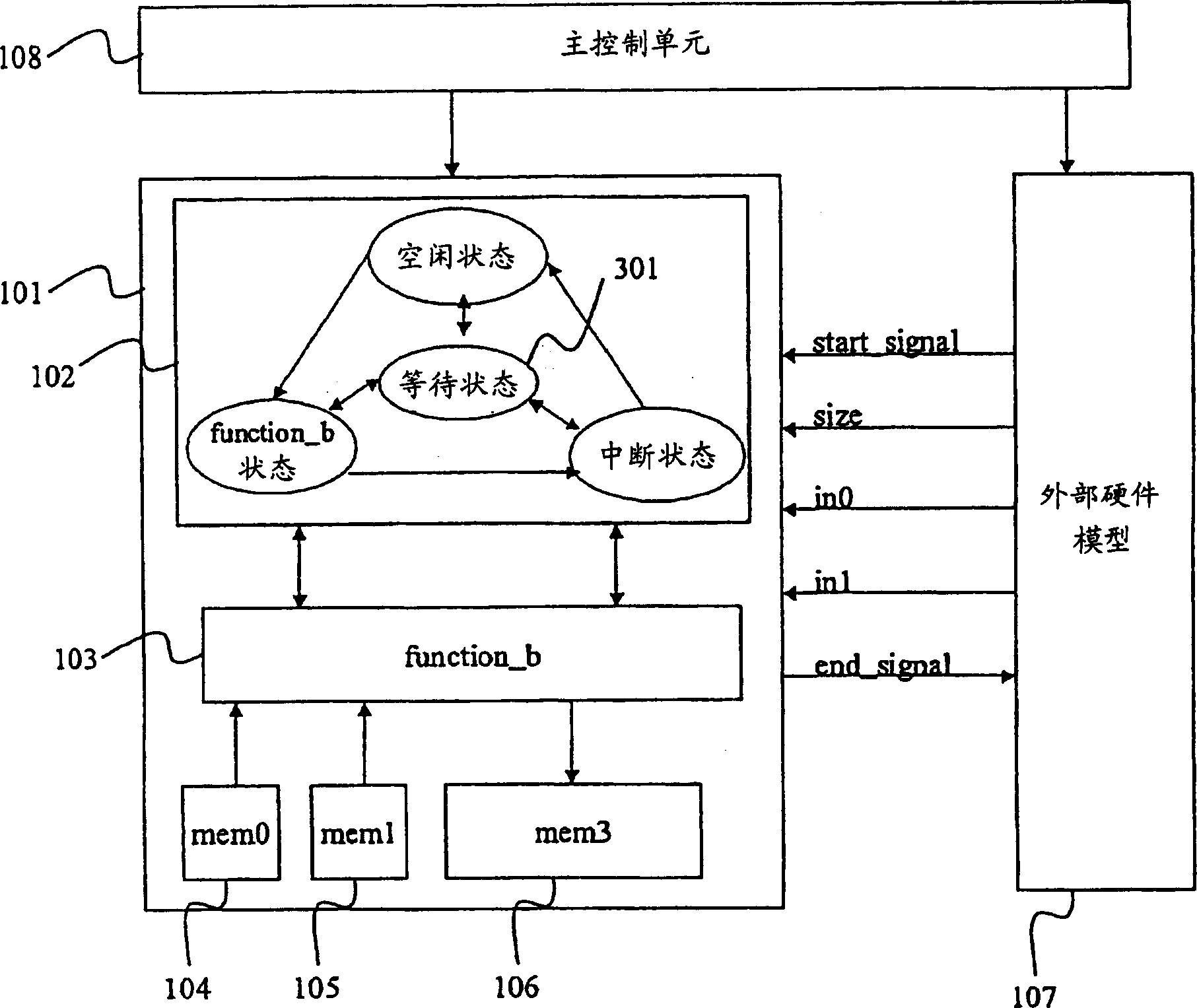

[0049] (Example Mode 1)

[0050] The best embodiment modes of the present invention will now be described in detail with reference to the accompanying drawings. First, a simulation model design method having a high degree of abstraction and capable of high-speed cycle basic simulation is described, which corresponds to the first object of the present invention.

[0051] To this end, "function_b" is represented as an instance of an algorithm model that uses C language to describe hardware as follows:

[0052] void function_b(size_a, in0, in1) {int i, tmp; for(i=0; i

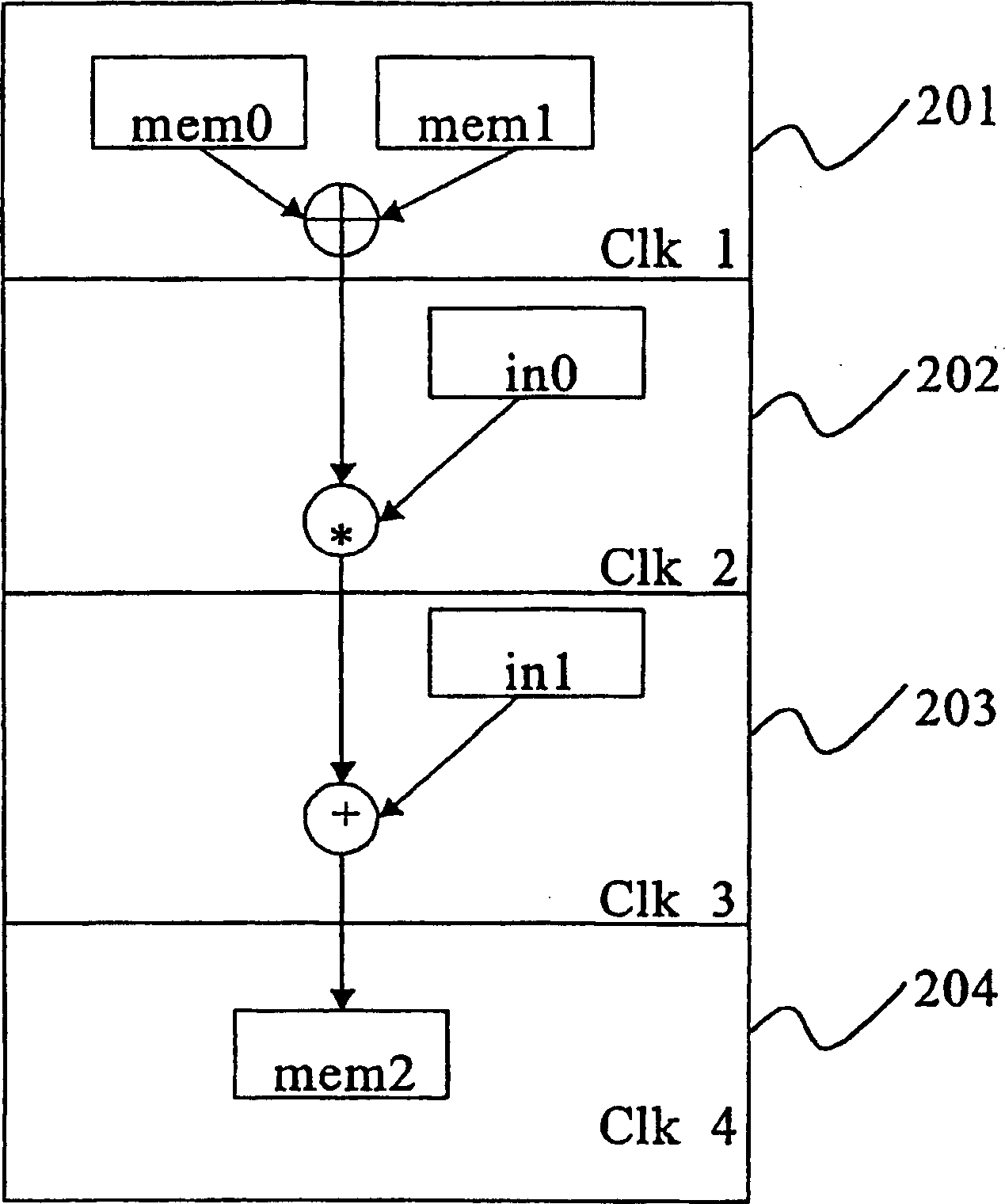

[0053] figure 1 is a schematic diagram showing a simulation device equipped with a high-speed cycle base model according to the present invention, which corresponds to such an algorithm model. The model 101 to be designed is arranged by a state control module model 102 , a calculation module model 103 and a storage model 104 , 105 , 106 . Also, there are a “start_signal” signal notifying the start of calcula...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More