Resistive cell structure for reducing soft error rate and inverter and forming method

A storage unit and soft error technology, applied in static memory, digital memory information, electrical components, etc., can solve problems such as data integrity loss, and achieve the effect of prolonging the delay time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make the above-mentioned and other objects, features and advantages of the present invention more comprehensible, the preferred embodiments are listed below, together with the accompanying drawings, and are described in detail as follows:

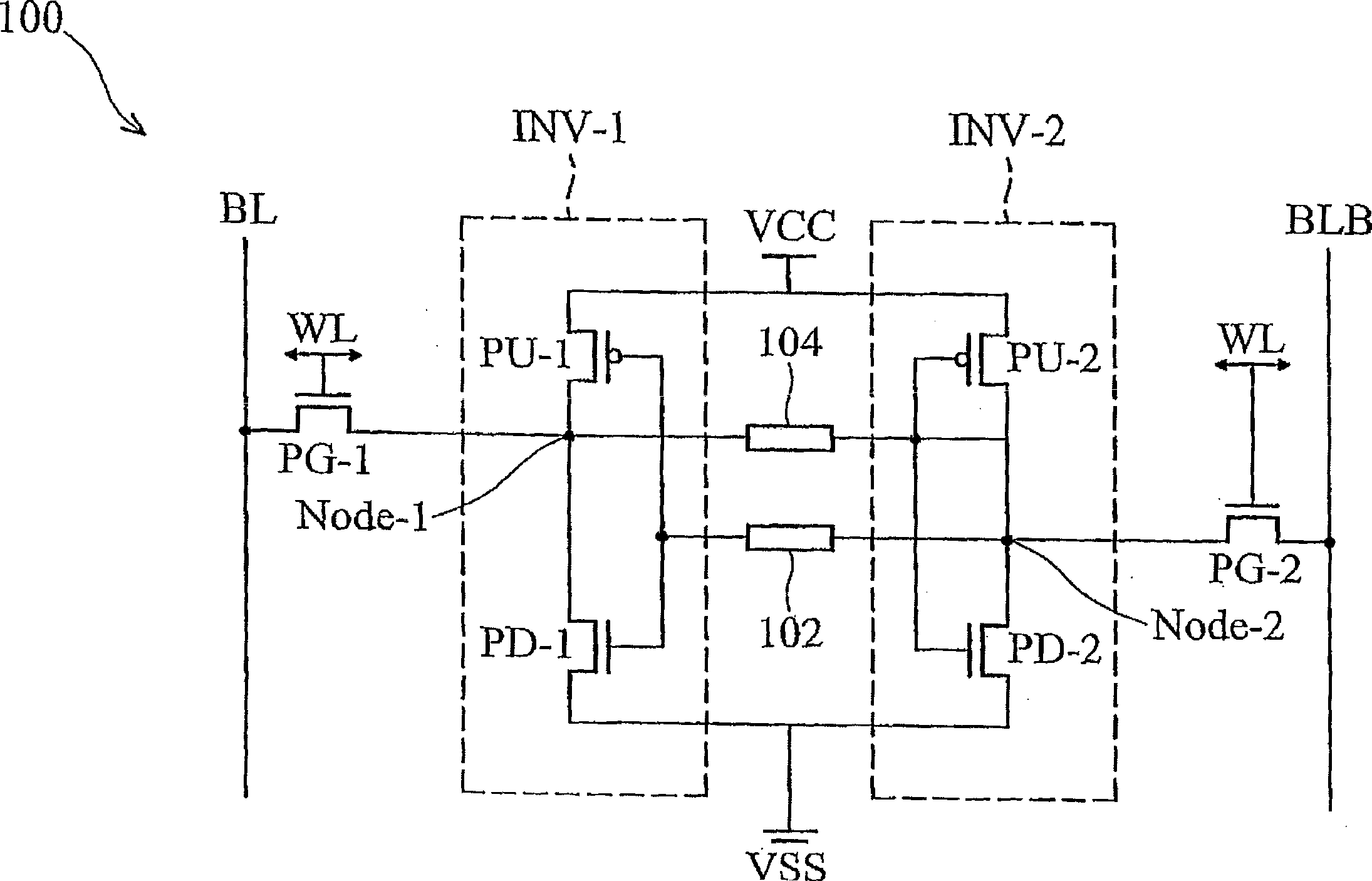

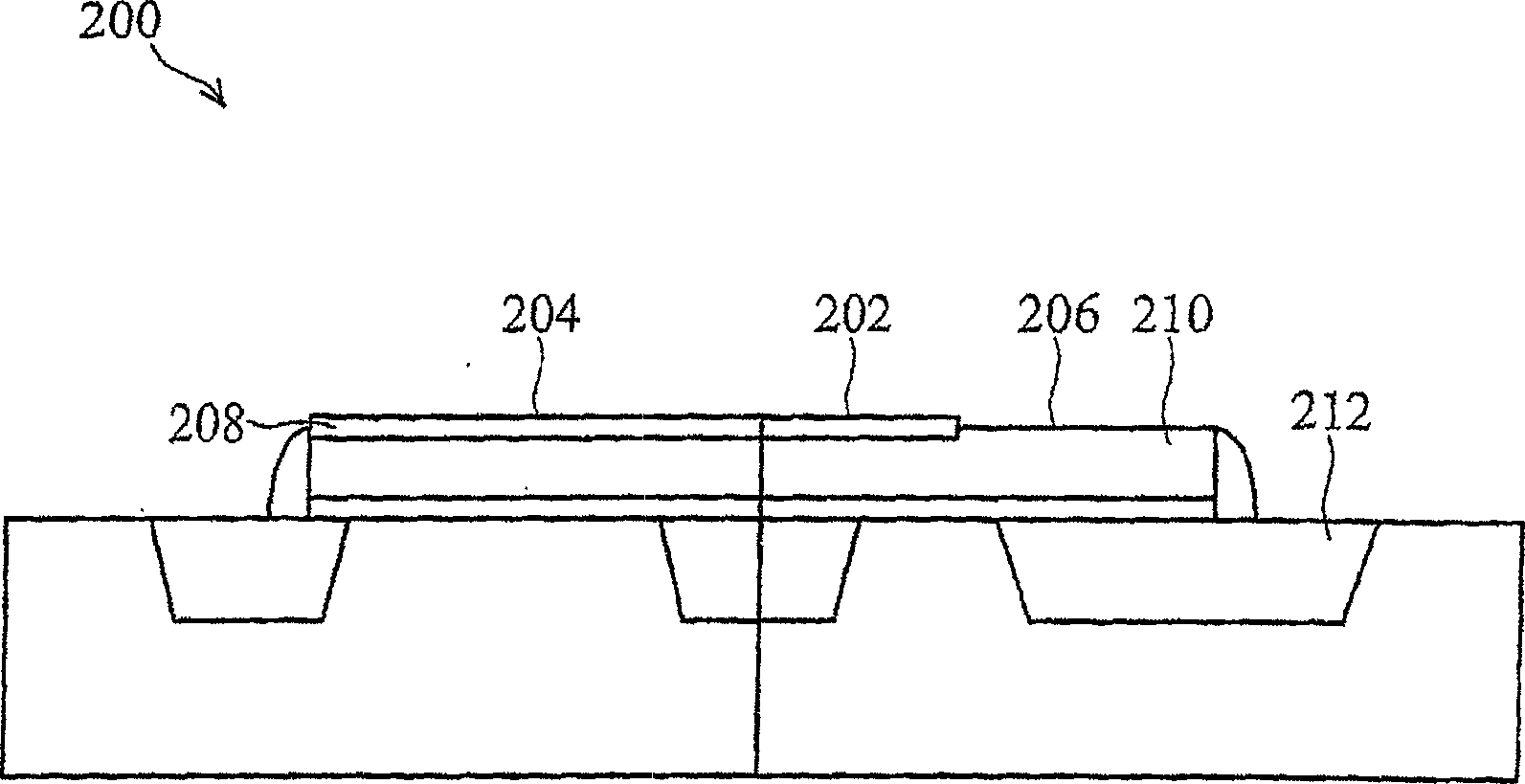

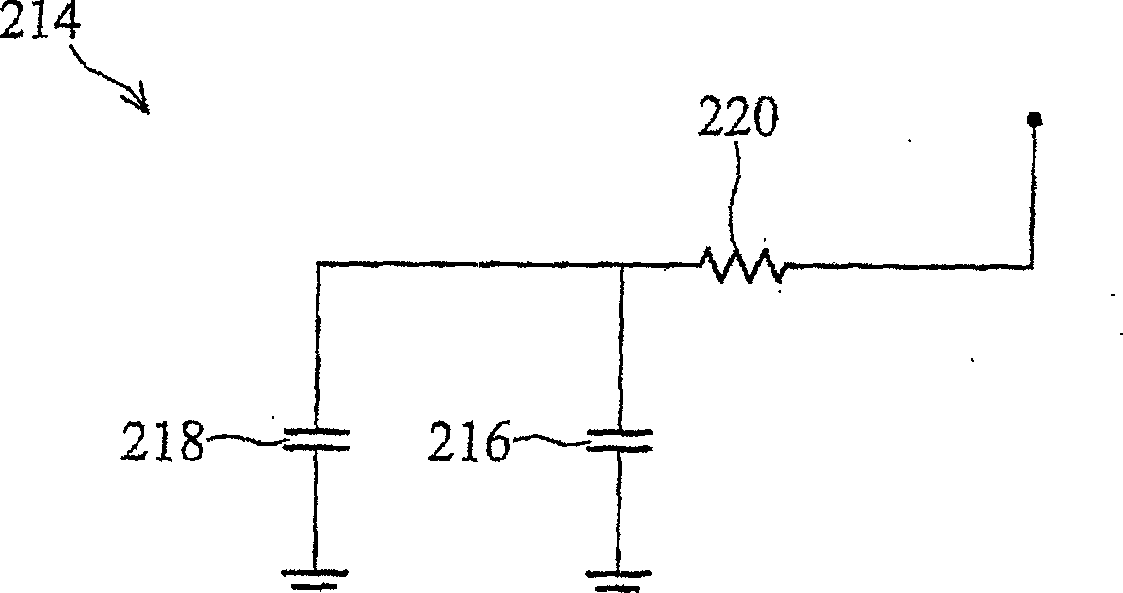

[0038] The present invention provides a design of a static random access memory unit with two resistors to reduce the soft error rate, thereby improving noise tolerance and data integrity. In several embodiments shown below, a standard static random access memory cell is modified by adding two resistors. Adding resistors increases the resistance / capacitance delay time (RC delay) required to change the stored data. Due to the standard static The two inverters of the random access memory unit are interactively coupled, and the impact of the return will also be delayed. The delay time can make the affected inverter self-compensate and maintain the original data, so it can reduce the noise caused by alpha particles The freque...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com