High-speed master-slave type D trigger in low power consumption

A flip-flop, low-power technology, applied in electrical pulse generator circuits, pulse generation, electrical components, etc., can solve the problems of high circuit power consumption, affecting circuit stability, power loss, etc., to achieve power consumption and delay. The effect of small time, small number, and power saving

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

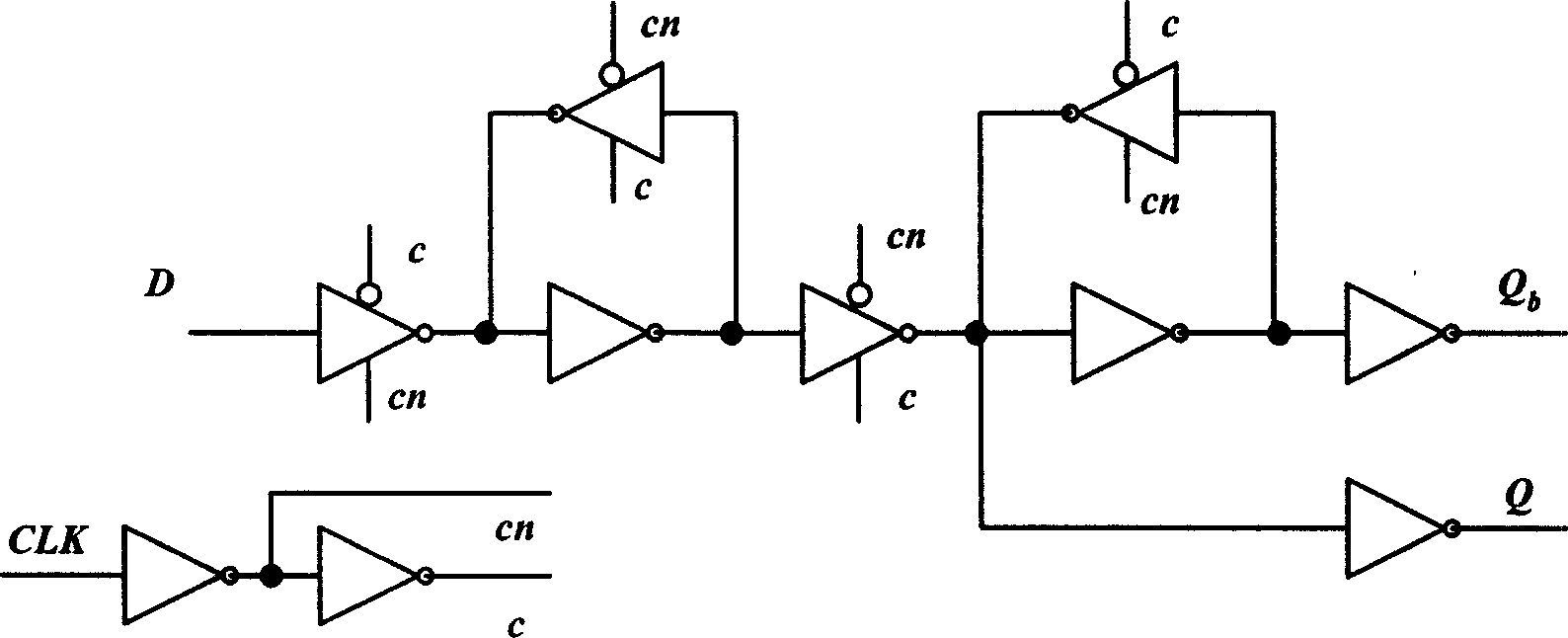

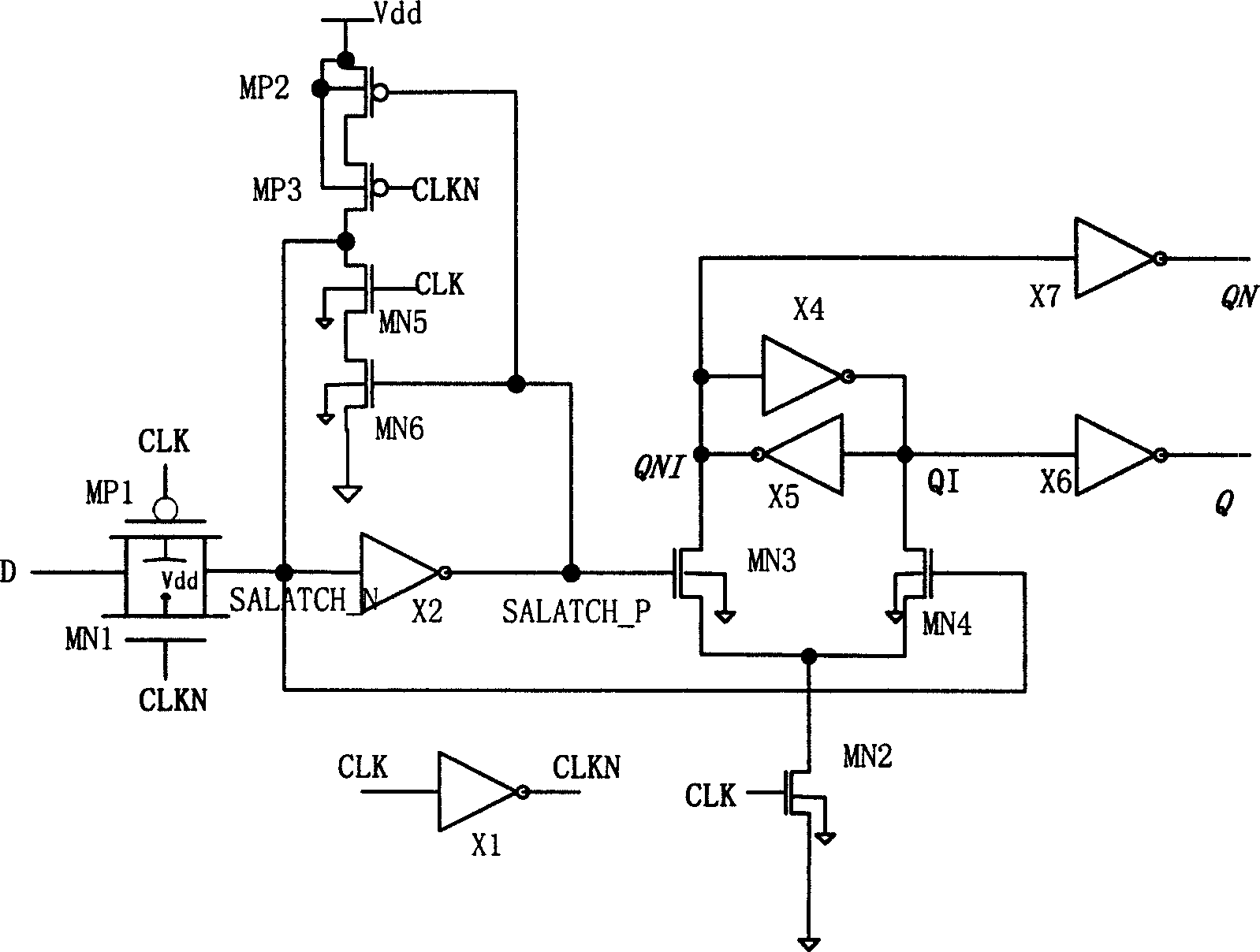

[0048] The technical scheme of the present invention to solve its technical problems is: the high-speed and low-power master-slave D flip-flop FFDHD1X_FLMS proposed by the present invention, such as Figure 3 Show. The FFDHD1X_FLMS flip-flop has the characteristics of low power consumption and low delay at the same time. Compared with the FFDHD1X flip-flop circuit, this structure uses fewer tubes, which can reduce the area of the circuit, the number of transistors controlled by the clock is also less, the internal node capacitance is smaller, and it has lower power consumption and smaller delay. At the same time, the second stage adopts a differential structure, which has better anti-noise performance and is more suitable for the design of low-power integrated circuits.

[0049] The working principle of the circuit is as follows: When CLK is low, the transmission gate composed of MN1 and MP1 is turned on, and the clocked inverter composed of MP2, MP3, MN5 and MN6 is turned off, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More