Access device for direct memory access and method for implementing single channel bidirectional data interaction

A memory and channel technology, applied in memory systems, electrical digital data processing, instruments, etc., can solve problems such as inability to realize effective utilization of memory resources, limit DMA peripheral resources, increase chip cost, etc., and achieve simple design and memory saving Space, the effect of improving the utilization rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

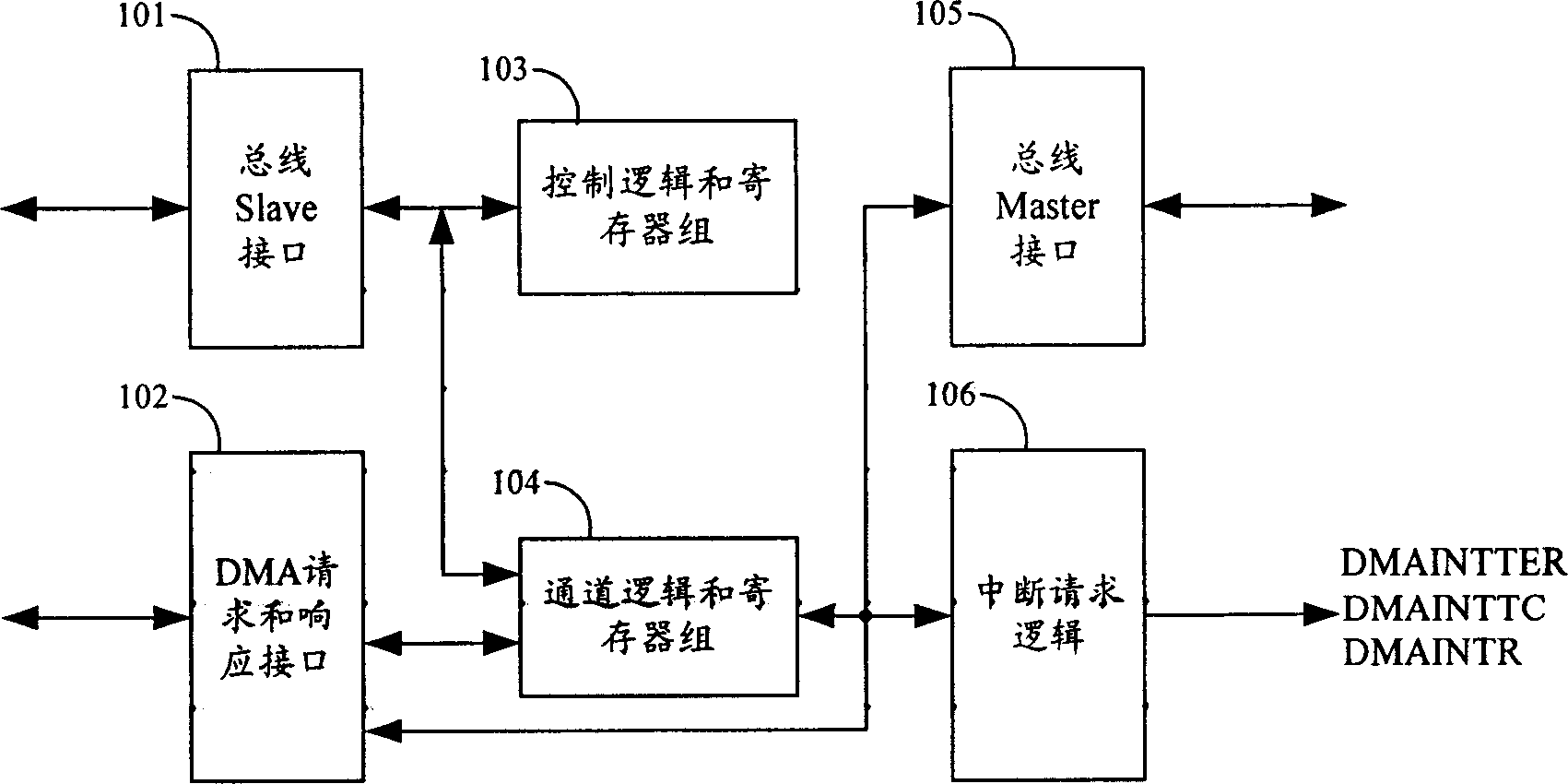

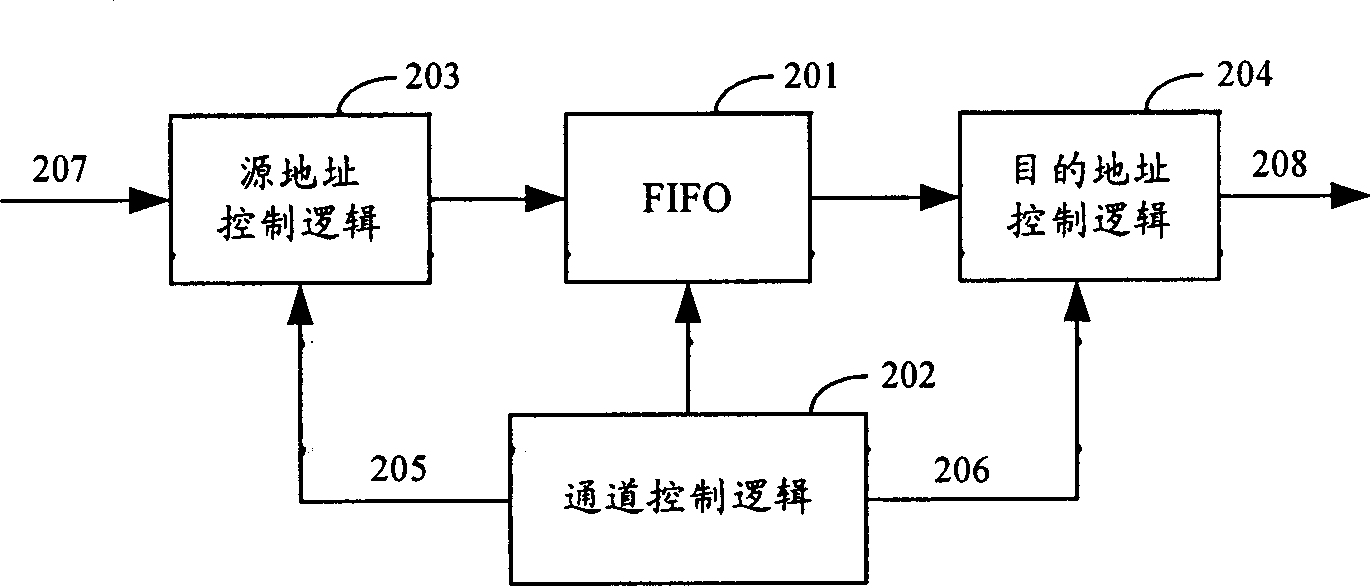

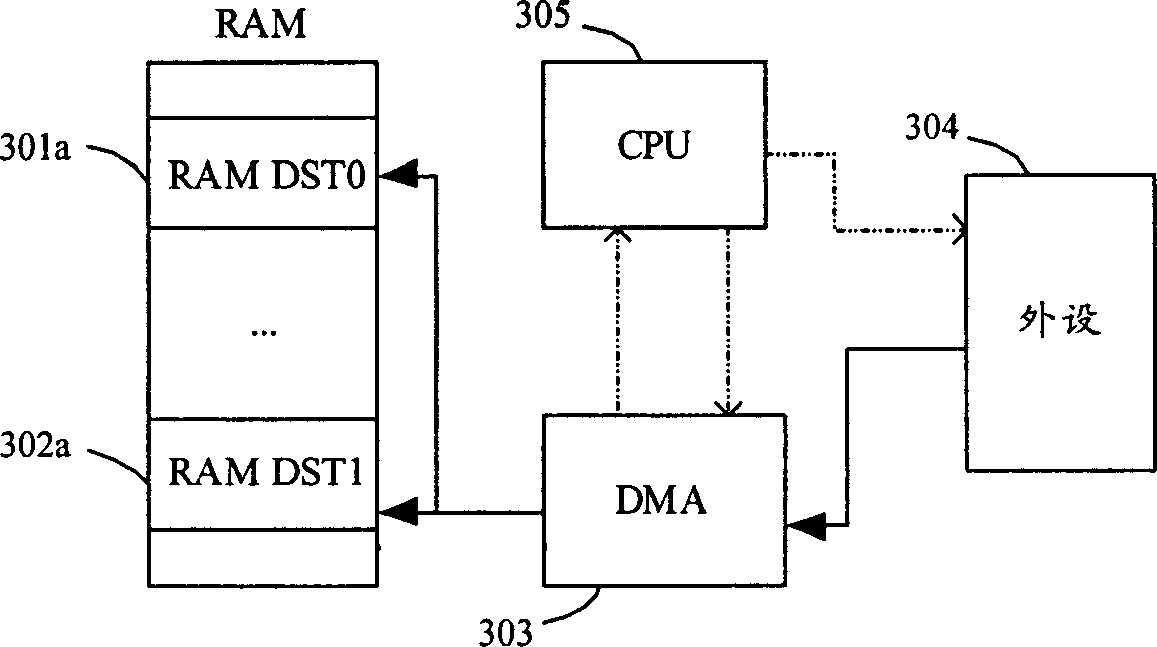

[0050] The core idea of this release is to improve the channel logic and the structure of each channel of the register group in the DMA, replace the FIFO control logic with the ping-pong operation structure, and realize the operation of different flow data through ping-pong switching, so that each channel of the DMA is independent It can simultaneously complete data reading and writing between peripherals and memory, forming a double DMA (DDMA, Duplicated DMA) structure.

[0051] In order to support the realization of the DDMA function, the DMA of the present invention has made two improvements to the existing DMA: first, a set of control registers is added corresponding to each channel; second, the implementation structure of the control logic of each DMA channel is changed and modified accordingly The structure of the channel control logic. Specifically: First, add four control registers for each channel to store the source address, destination address, control parameters and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More