Chip architecture with multiple functions

A multi-functional, chip technology, applied in the direction of electrical components, electrical solid devices, circuits, etc., can solve the problems of product elastic cost reduction, product inelasticity, unfavorable effective cost, etc., and achieve the goal of avoiding volume, reducing volume, and reducing cost Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In order to have a further cognition and understanding of the features, purposes and functions of the present invention, the detailed description is as follows in conjunction with the accompanying drawings:

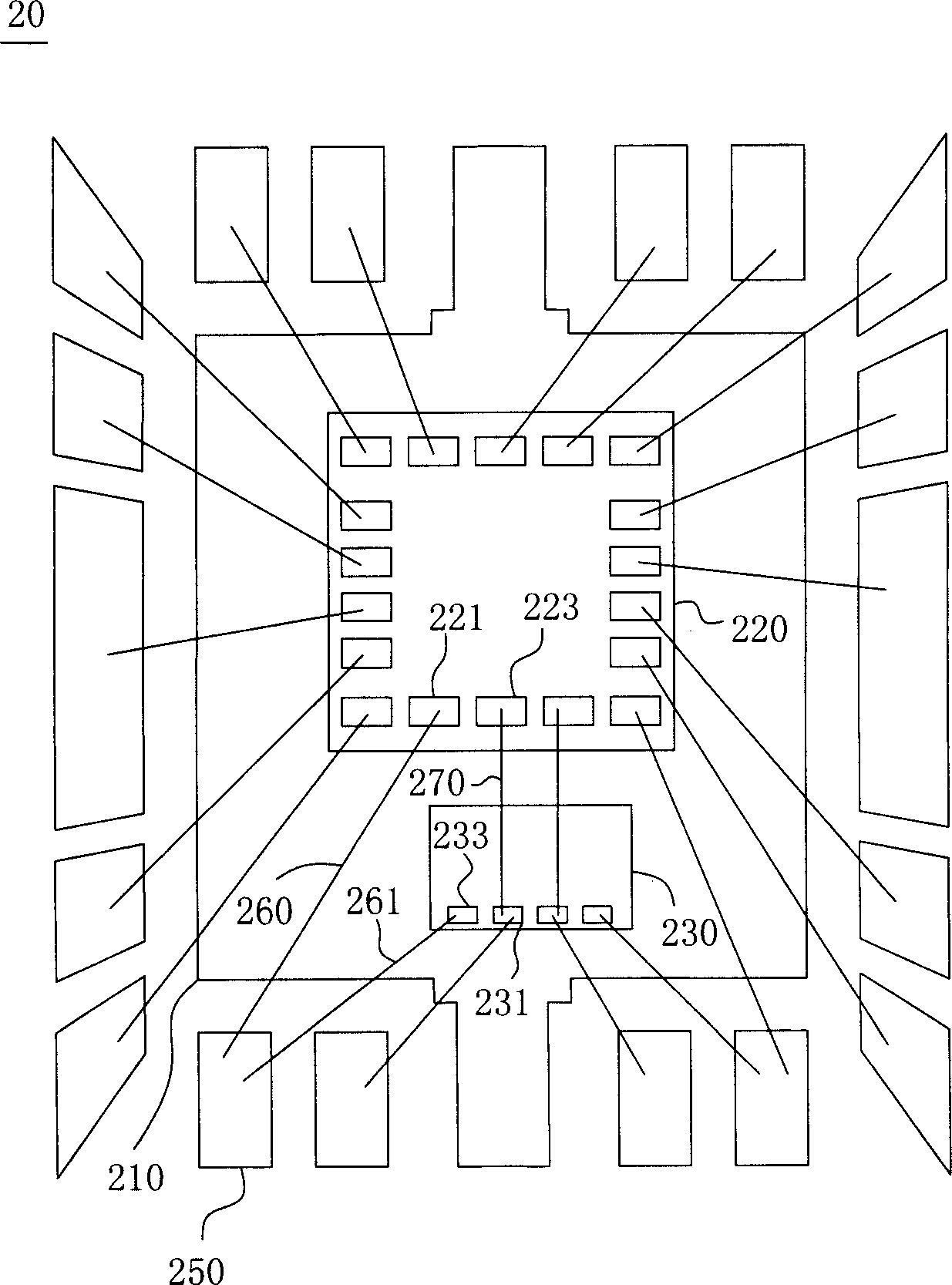

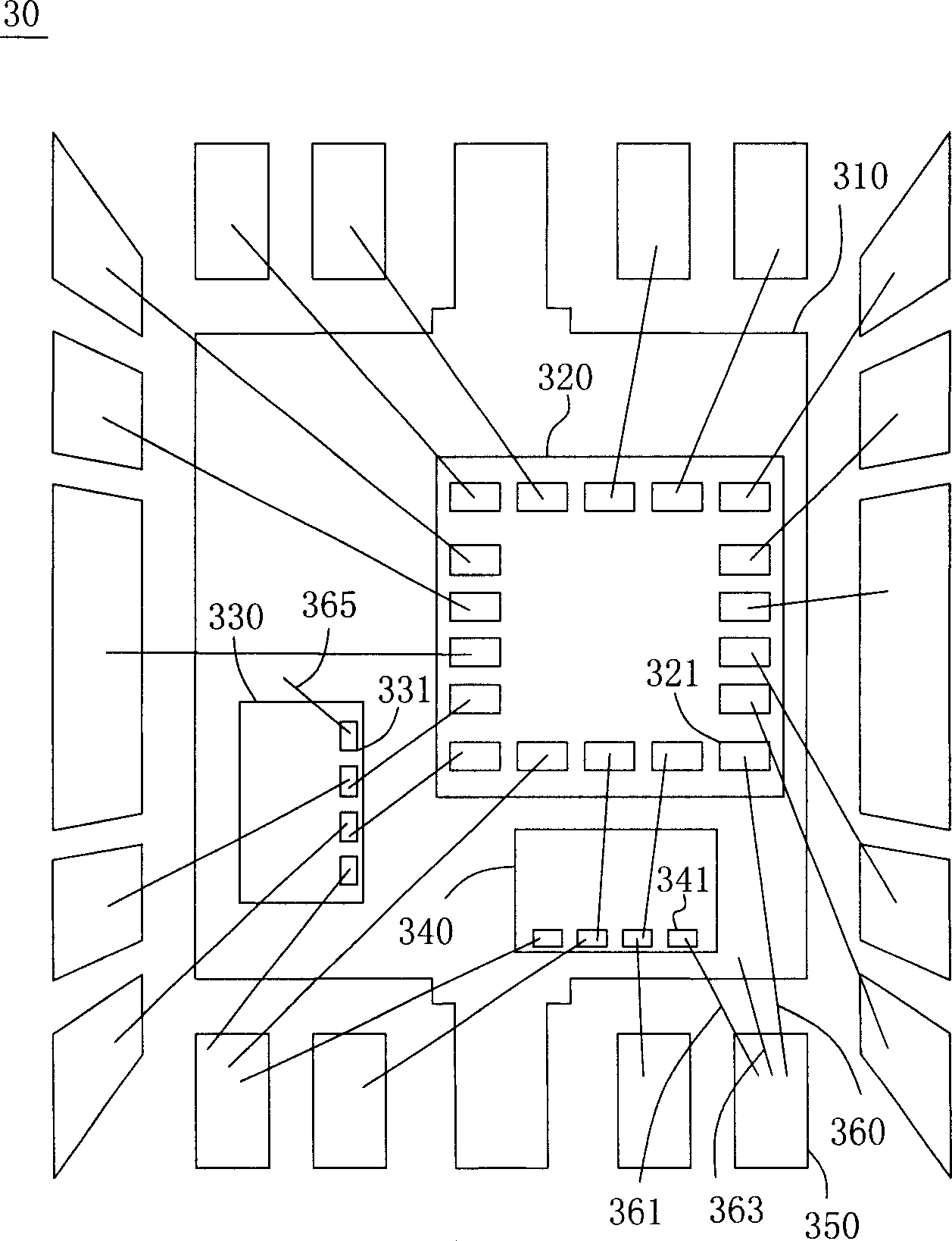

[0040] Please refer to figure 1 , figure 1 It is a schematic diagram of the multifunctional chip architecture of the present invention. The outside of the chip structure 10 is covered by a package (not shown), and the inside of the package mainly includes a chip holder 110 , a microcontroller 120 and a non-volatile memory 130 on the chip holder. In particular, the microcontroller 120 and the non-volatile memory 130 can choose to adopt different processes.

[0041] The advantage of using different processes for the microcontroller 120 and the non-volatile memory 130 is that when the chip architecture 10 is actually operating, the degree of current or voltage that the microcontroller 120 and the non-volatile memory 130 bear is not proportional to the scale. The sa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com