Method for decreasing data access delay in stream processor

A technology of stream processor and data access, which is applied in various digital computer combinations and general-purpose stored program computers, etc. It can solve the problems of increasing data access delay, high overhead of data transmission process, low efficiency of stream processor data access method, etc. , to achieve the effect of reducing data access delay and reducing the number of memory accesses

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

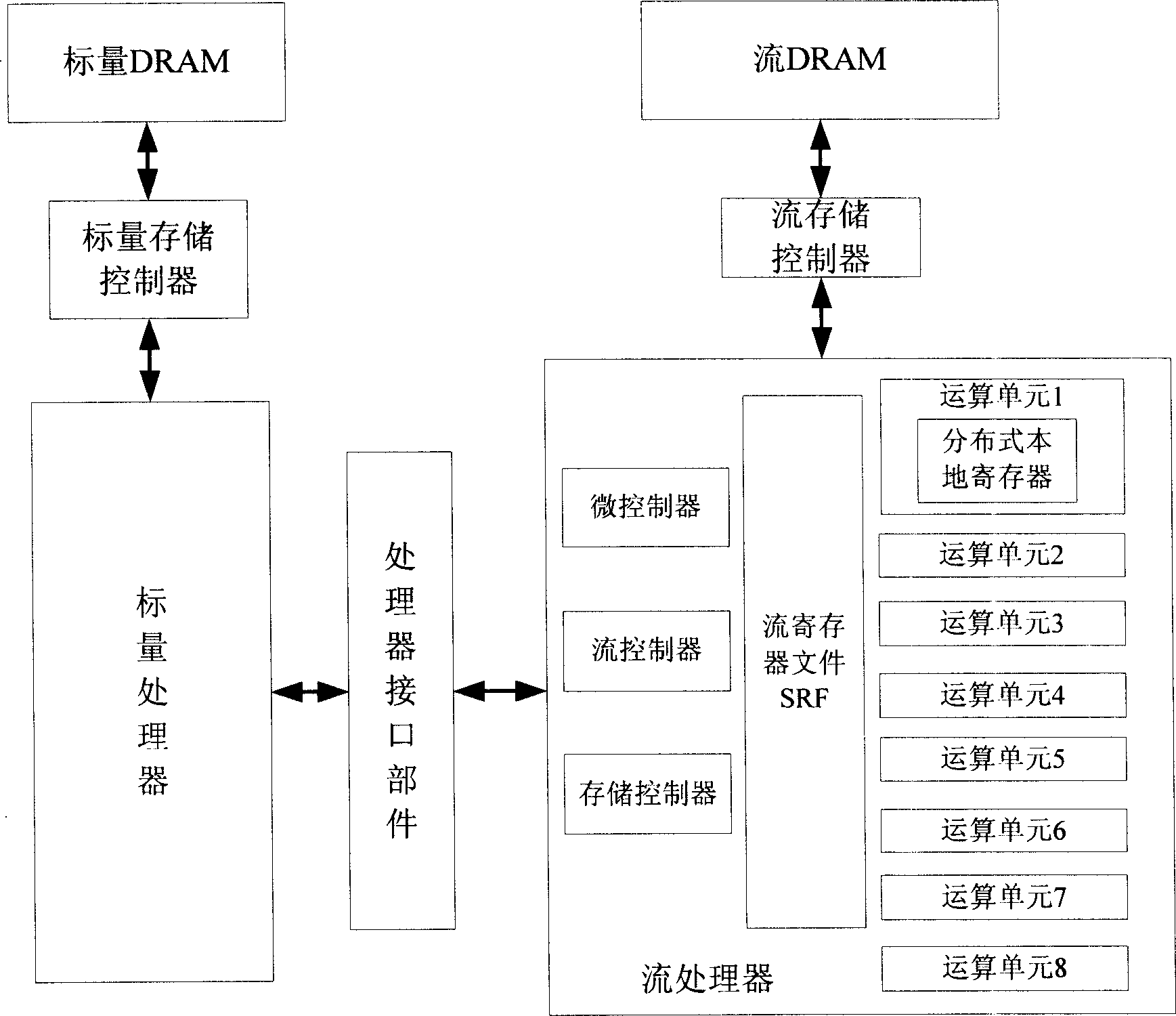

[0052] figure 1 It is a structural diagram of a stream processor published by the Stanford University Imagine Processor Research Group on the http: / / cva.stanford.edu / imagine website. In the design of stream architecture, the storage space of scalar processor and stream processor is separated logically, and two independent off-chip DRAM memories are also used physically, namely scalar DRAM memory and stream DRAM memory. There is no data path and control path between memories. The scalar processor and stream processor also use their own storage controllers, data paths of off-chip DRAM, control paths and corresponding chip pins, and the clock system is also independent. The storage system belonging to the scalar processor is only connected to the scalar processor, and the storage system belonging to the stream processor is only connected to the stream processor. As the coprocessor of the scalar processor, the stream processor is interconnected with the scalar processor by using...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More