Method of manufacturing a semiconductor structure and a corresponding semiconductor structure

A semiconductor and body region technology, applied in the fields of semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., can solve problems such as functional damage and impact, and achieve the effect of minimizing the risk of damage

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

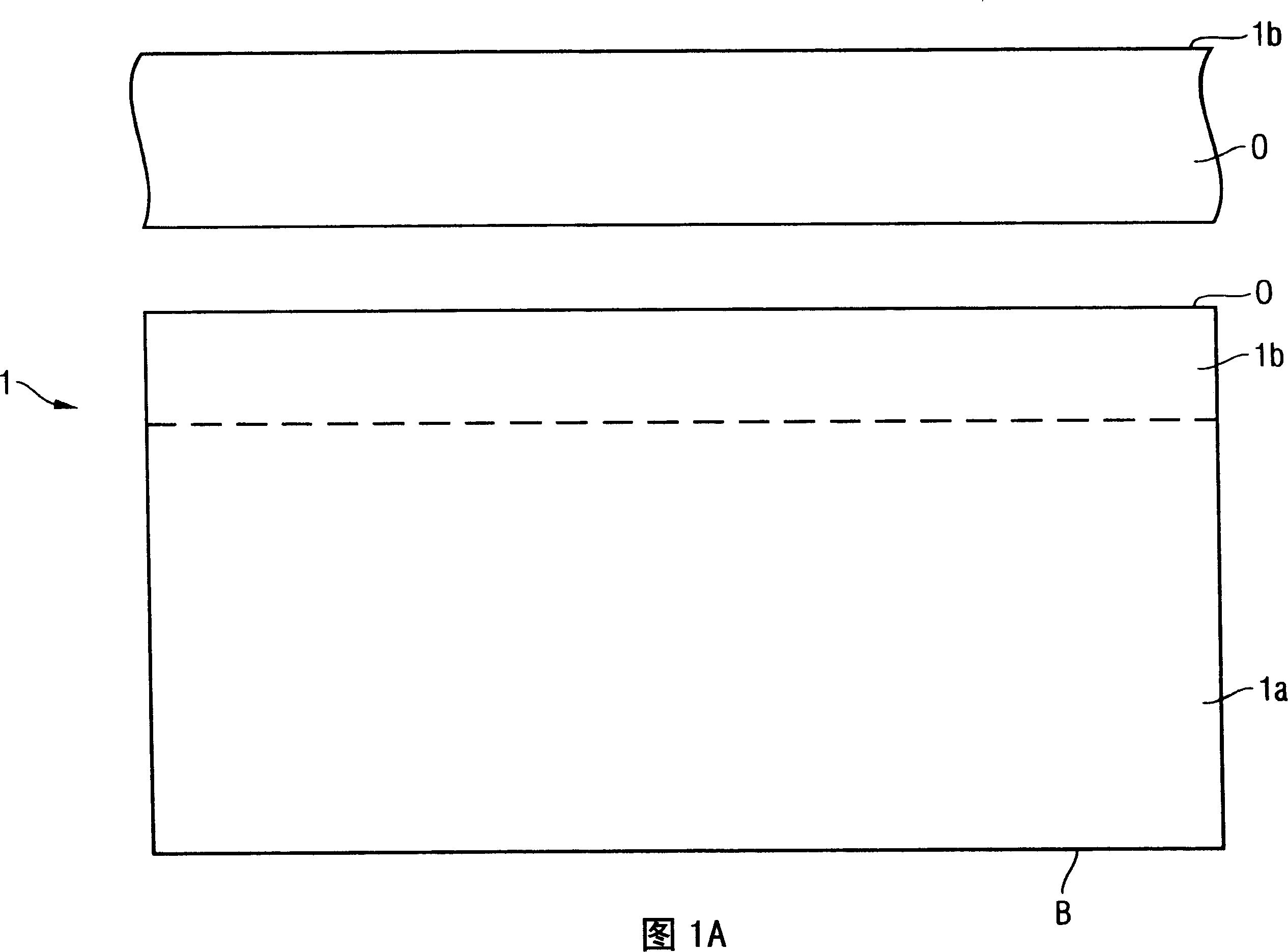

[0023] In FIG. 1A, reference numeral 1 denotes a silicon semiconductor wafer. A typical thickness of the silicon semiconductor wafer 1 is between 100 and 760 μm. A silicon semiconductor wafer 1 comprises a body region 1a on the wafer backside B and an active region 1b on the wafer front side 0, where integrated circuit elements (eg memory cells and peripheral devices) are to be formed. In the upper part of Fig. 1A, a partial view of the upper surface 0 of the active region 1b is shown.

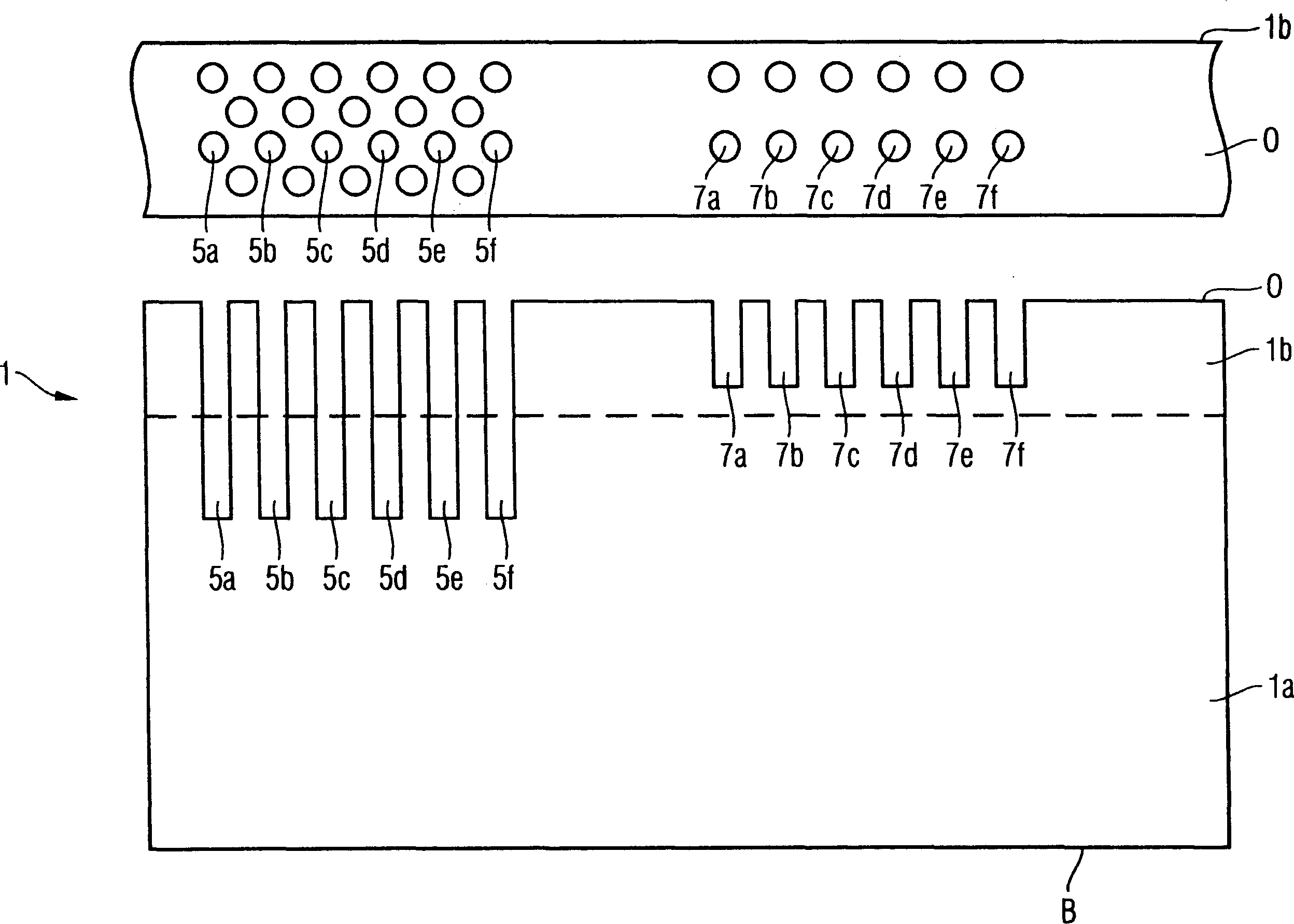

[0024] exist Figure 1B In the next process step shown in , storage capacitor trenches 7a-7f are formed in the active region 1b, and a plurality of contact trenches 5a-5f are formed in the active region 1b, wherein the contact trenches 5a-5f extend into Body region 1a. A typical depth of the storage capacitor trenches 7a-7f is 5 to 10 μm and a typical depth of the contact trenches 5a-5f is 15 to 30 m. The trenches 5a-5f may be formed in two successive process steps using the well-known anis...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com