Production of flash memory

A manufacturing method and memory technology, which is applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as improving the integration of components, and achieve the effects of reduced contact resistance, small size, and large process space

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

no. 1 example

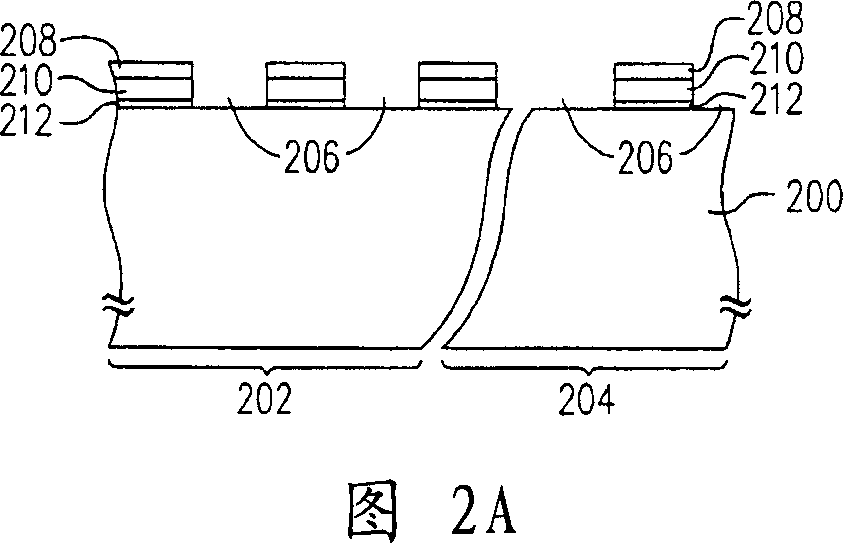

[0100] FIG. 2A to FIG. 2F illustrate a manufacturing flow chart of a flash memory according to a preferred embodiment of the present invention. Wherein, FIG. 2E and FIG. 2F belong to the same manufacturing process step, and FIG. 2E is a cross-sectional view along the section line I-I' and section line II-II' of FIG. 2D. FIG. 2F is a subsequent manufacturing flow chart of FIG. 2E .

[0101] Referring to FIG. 2A , firstly, a substrate 200 is provided. The substrate 200 can be divided into a memory cell area 202 and a peripheral circuit area 204 . Next, a dielectric material layer (not shown), a conductive material layer (not shown), and a mask layer (not shown) are sequentially formed on the substrate 200 . The material of the dielectric material layer is, for example, silicon oxide, and its formation method is, for example, thermal oxidation. The material of the conductor material layer is, for example, doped polysilicon, and its formation method is, for example, chemical va...

no. 2 example

[0114] FIG. 3A to FIG. 3E illustrate a manufacturing flow chart of a flash memory according to a preferred embodiment of the present invention. Wherein, FIG. 3C and FIG. 3D belong to the same manufacturing process step, and FIG. 3D is a cross-sectional view drawn along the section line I-I' and section line II-II' of FIG. 3C. FIG. 3E is a subsequent manufacturing flow chart of FIG. 3D .

[0115] Referring to FIG. 3A , firstly, a substrate 300 is provided. The substrate 300 can be divided into a memory cell area 302 and a peripheral circuit area 304 . A plurality of device isolation structures 306 have been formed in the substrate 300 . A dielectric layer 308 and a conductive layer 310 disposed on the dielectric layer 308 are formed between two adjacent device isolation structures 306 in the memory cell area 302 . A dielectric layer 312 is formed between two adjacent device isolation structures 306 in the peripheral circuit area 304 , and a conductive layer 314 is formed on ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More