A system to acquire and control data for radiation imaging

A data acquisition and radiation imaging technology, applied in the field of radiation detection, can solve the problems of inconvenient data acquisition and transmission, complex system structure, poor signal anti-interference ability, etc., to improve anti-interference ability, simplify circuits, and reduce electromagnetic interference. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The following examples are used to illustrate the present invention, but are not intended to limit the scope of the present invention.

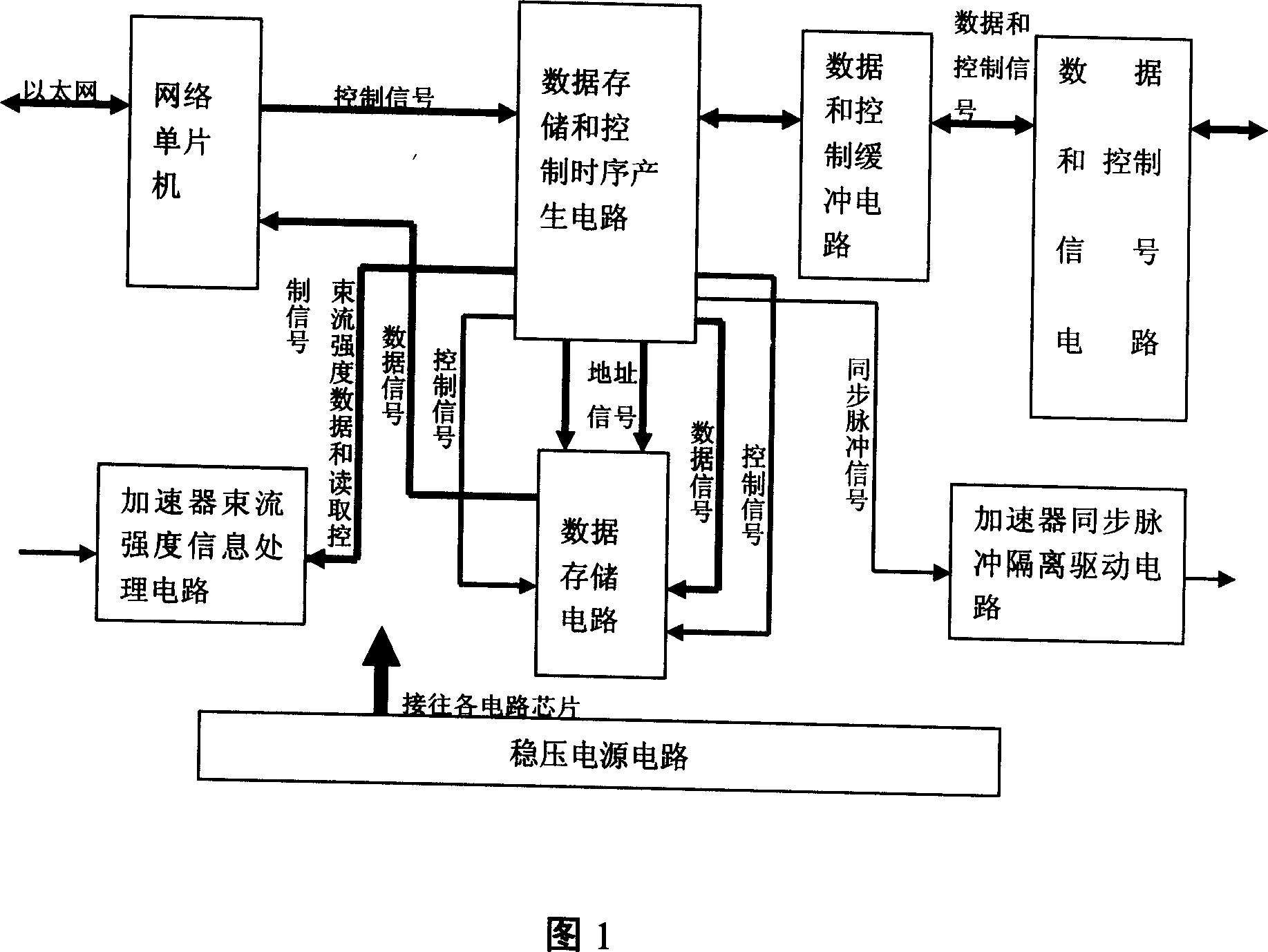

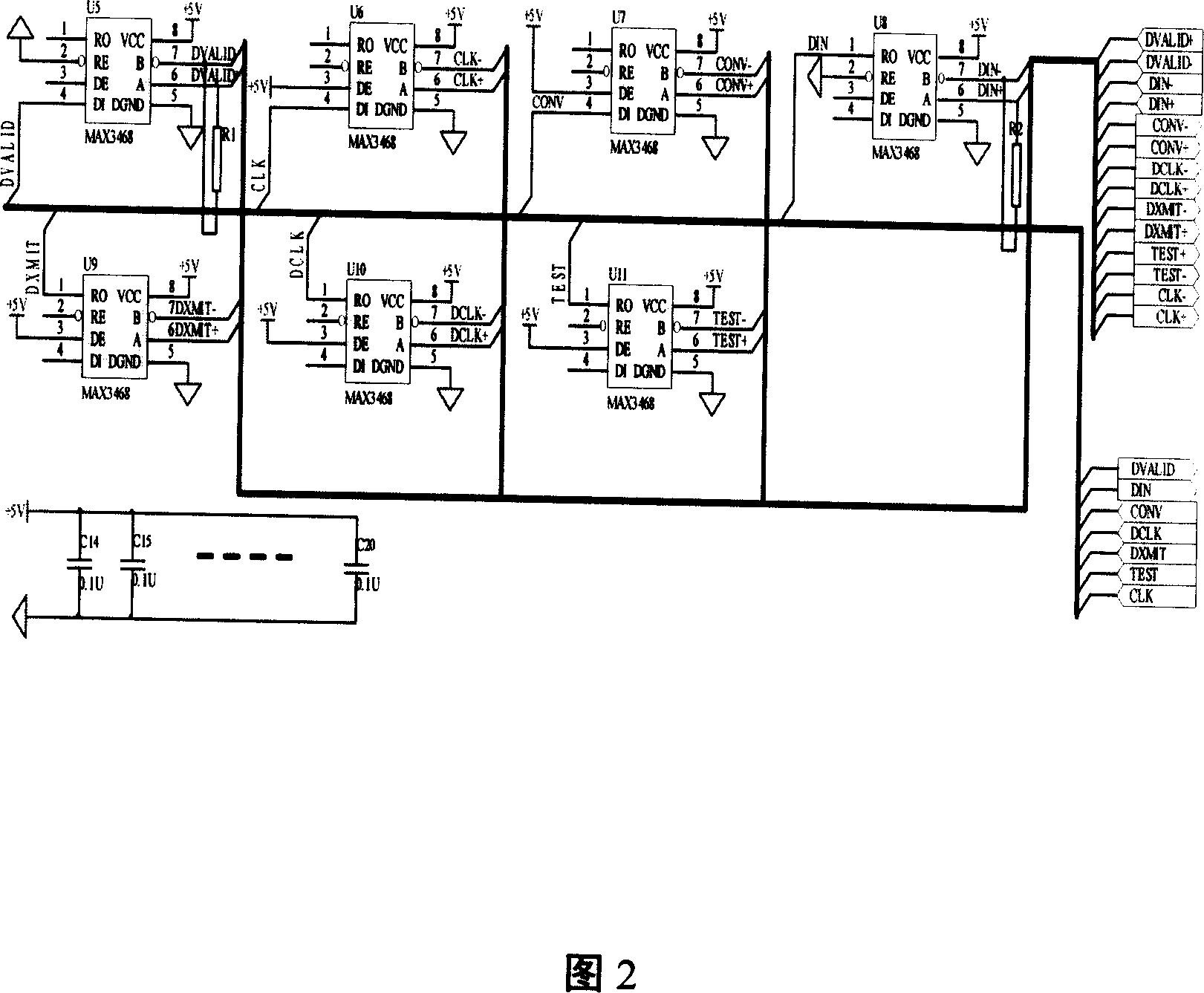

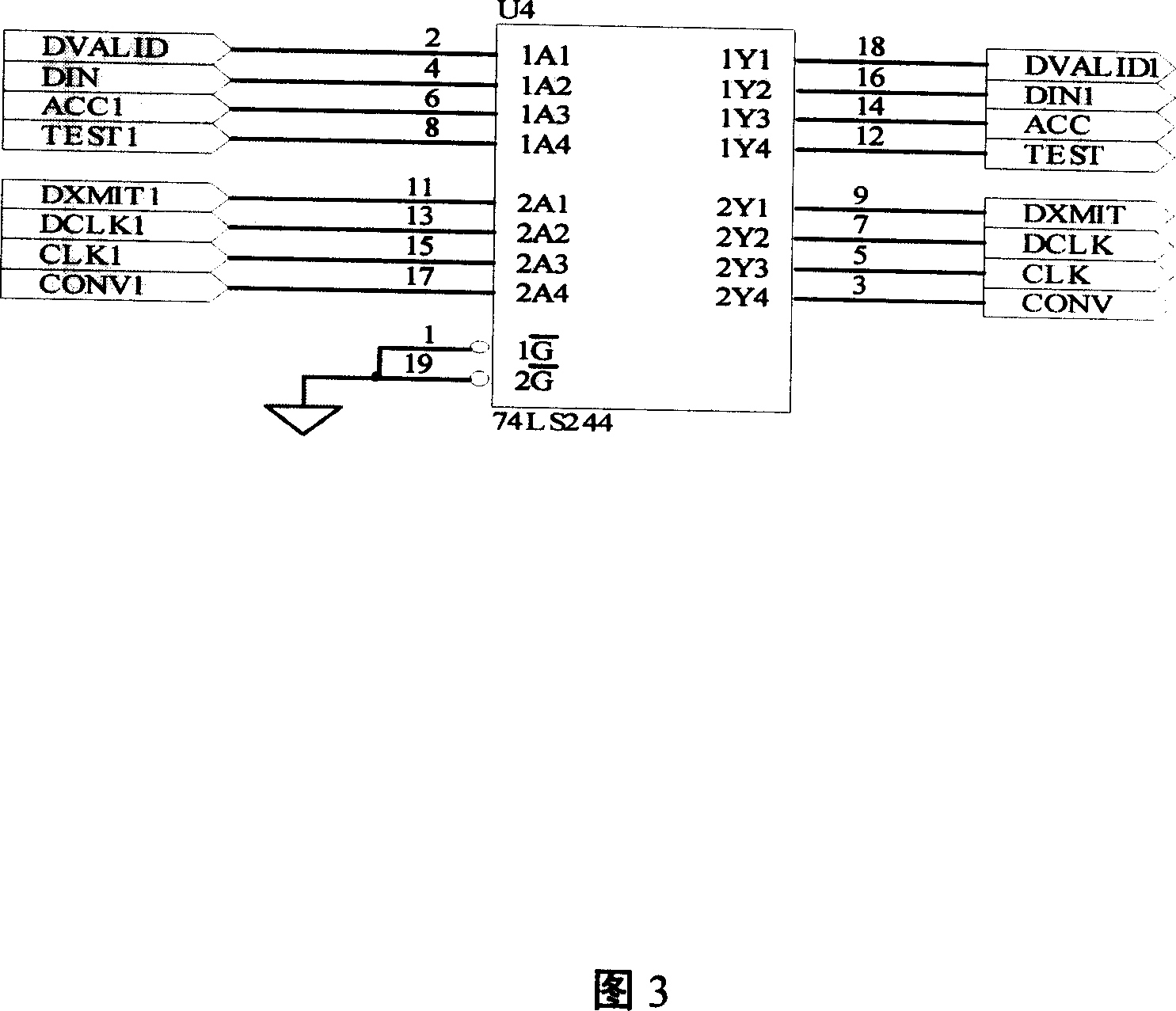

[0037] Referring to Fig. 1 and Fig. 10, the circuit realizing the present invention includes: receiving detector signal and receiving or sending RS485 data and control signal differential circuit 4, shaping and driving enhanced buffer circuit 3 for receiving or sending data and control signal The data and control signal timing generation circuit 2 that receives the command of the network microcontroller 1 and controls the rest of the circuits accelerates its beam intensity information processing circuit 5, and the accelerator synchronous pulse isolation drive circuit 7 receives data information and sends it through Ethernet To the next-level image inspection subsystem 10 and the network single-chip microcomputer 1 that receives the image inspection subsystem commands and sends them to the data and control signal timing generation circui...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com