A MOS FET tube and its manufacturing method

A field effect tube and process technology, applied in the field of semiconductor manufacturing process, can solve the problems of large parasitic capacitance and affecting the speed performance of digital circuits, etc., and achieve the effect of reducing overlapping area, improving speed performance and reducing gate-drain overlapping capacitance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

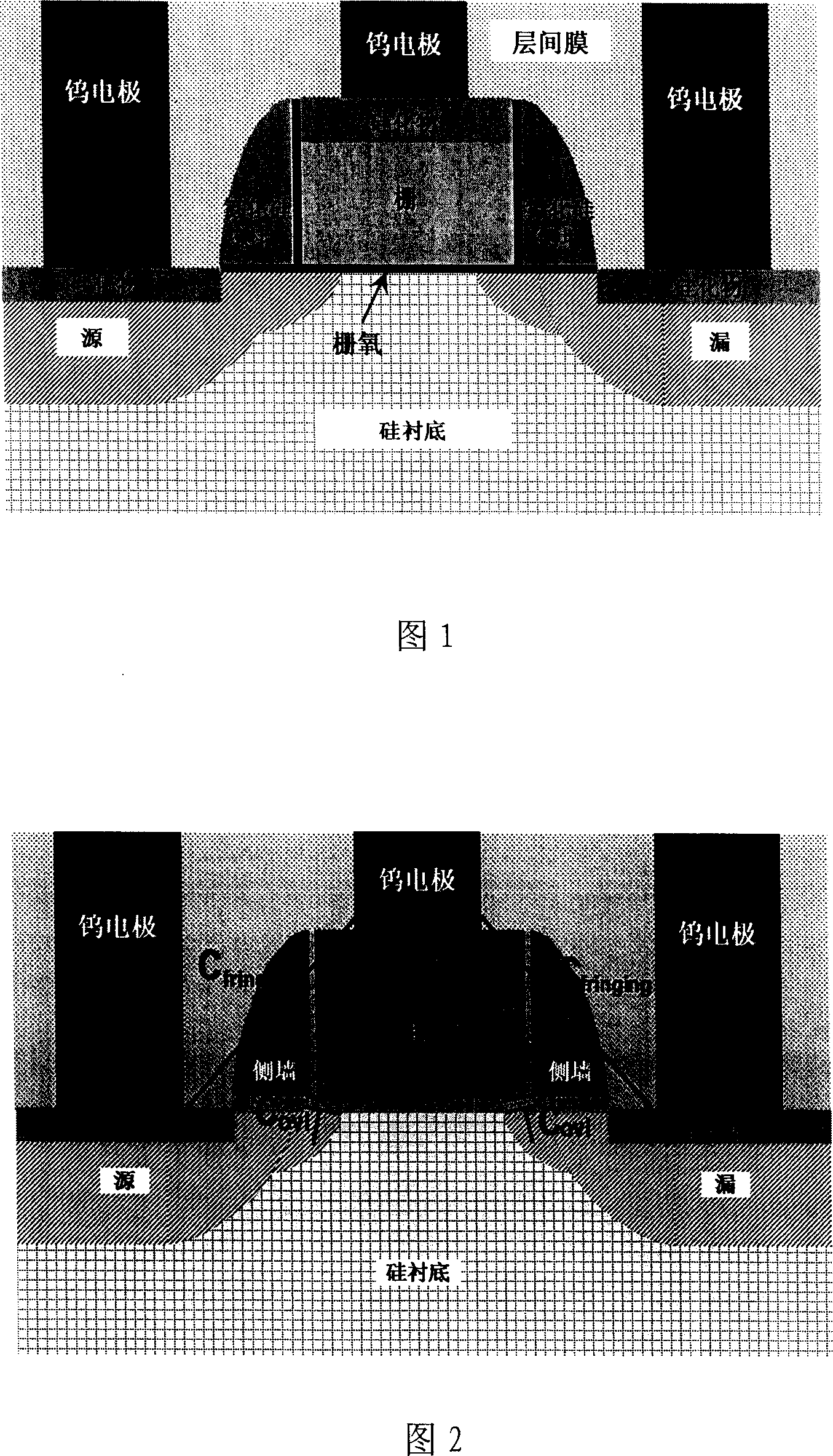

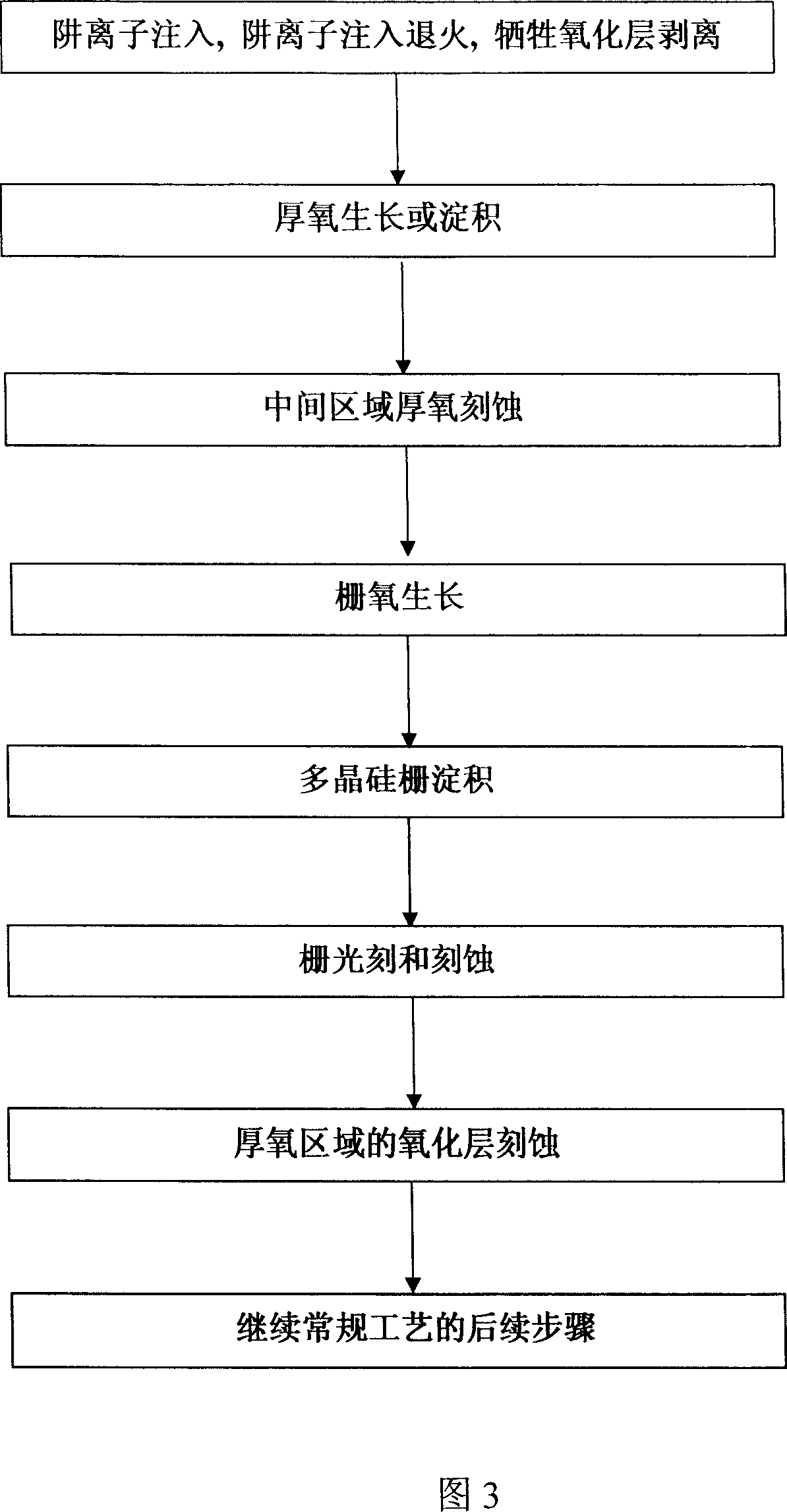

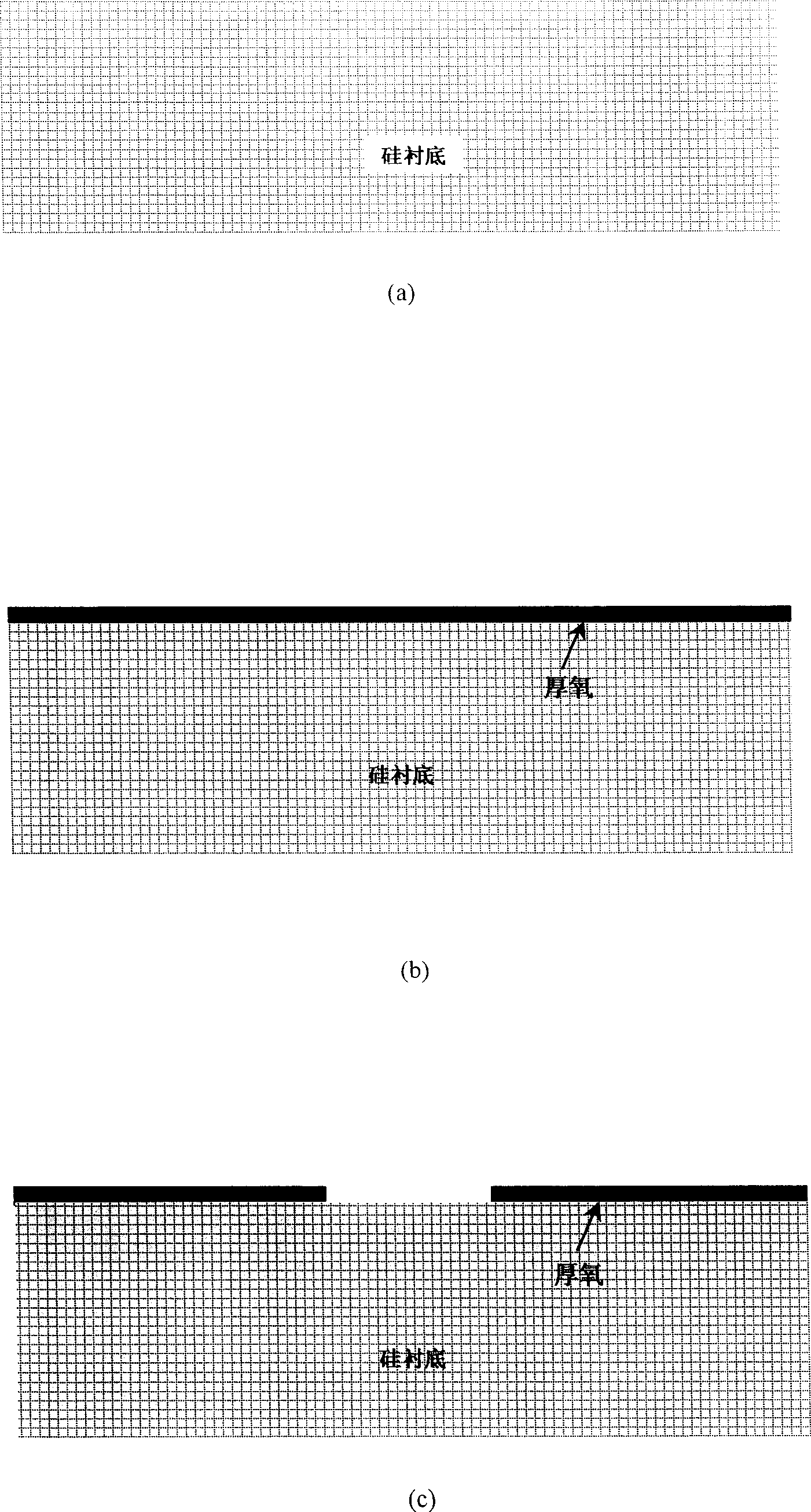

[0016] As shown in Figures 3 and 4, a method for manufacturing a MOS field effect transistor includes the following steps. First, after the trap ion implantation, the trap ion implantation annealing, and the stripping of the sacrificial oxide layer are completed in the conventional process flow, see Fig. 4 (a); Next, thermally grow or deposit a thick oxide layer, the thickness of which should be 2 to 5 times the thickness of the gate oxide grown in subsequent processes, see Figure 4(b). And within the above range, the specific thickness of the thick oxygen needs to be optimized and determined according to the electrical characteristics of the transistor and related process conditions. In the third step, the thick oxygen in the middle area is completely etched away, see Figure 4(c). The edge of the thick oxygen etching region needs to be between the source / drain substrate PN junction and the gate edge to be fabricated in subsequent processes, and the specific position of the ed...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More