Method for implementing on-chip command cache

An implementation method and instruction technology, applied in the field of hardware implementation of an on-chip instruction cache control system, can solve the problems of long instruction fetch time, poor reliability, and high power consumption, achieve low power consumption, avoid software judgment, and improve reliability Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

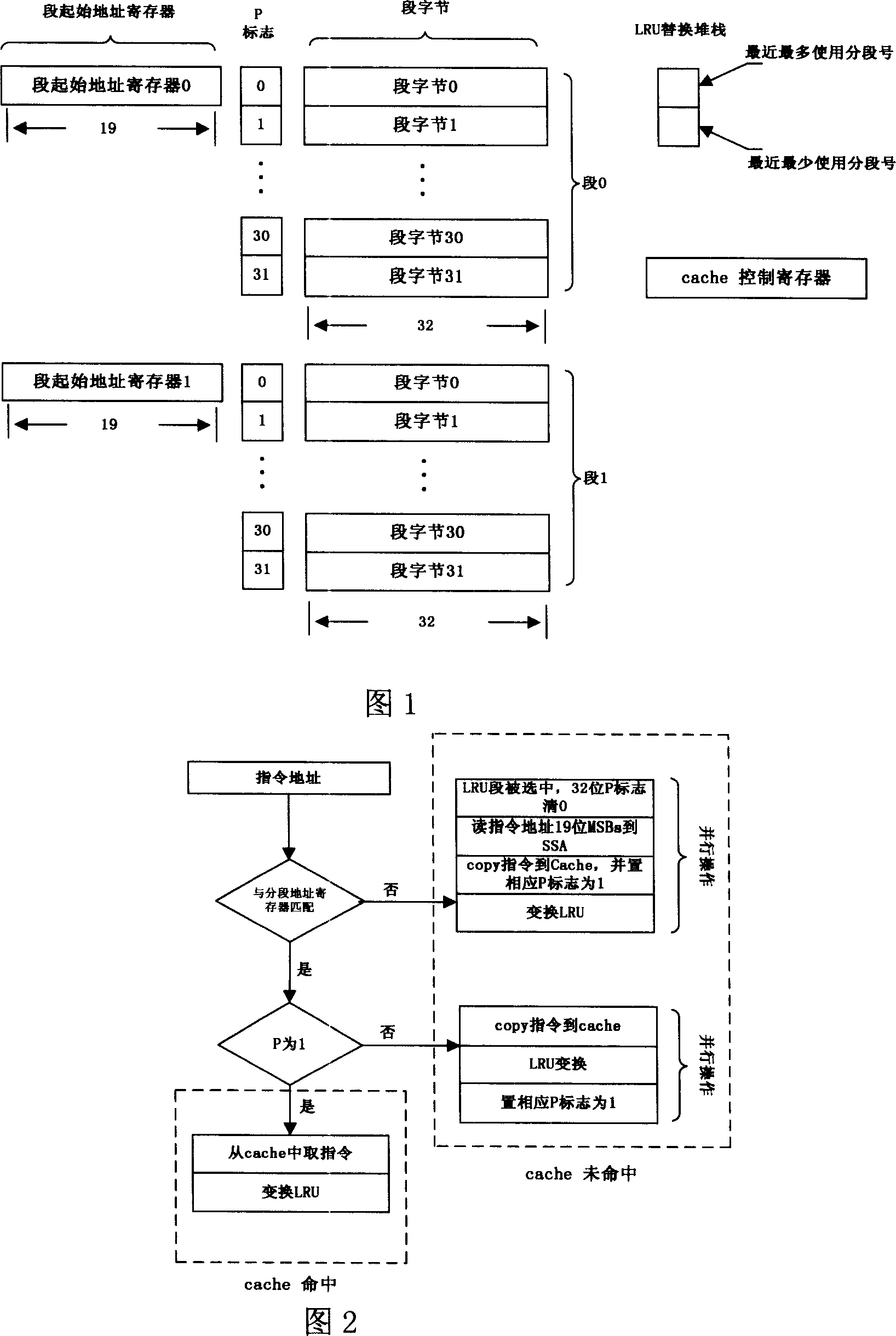

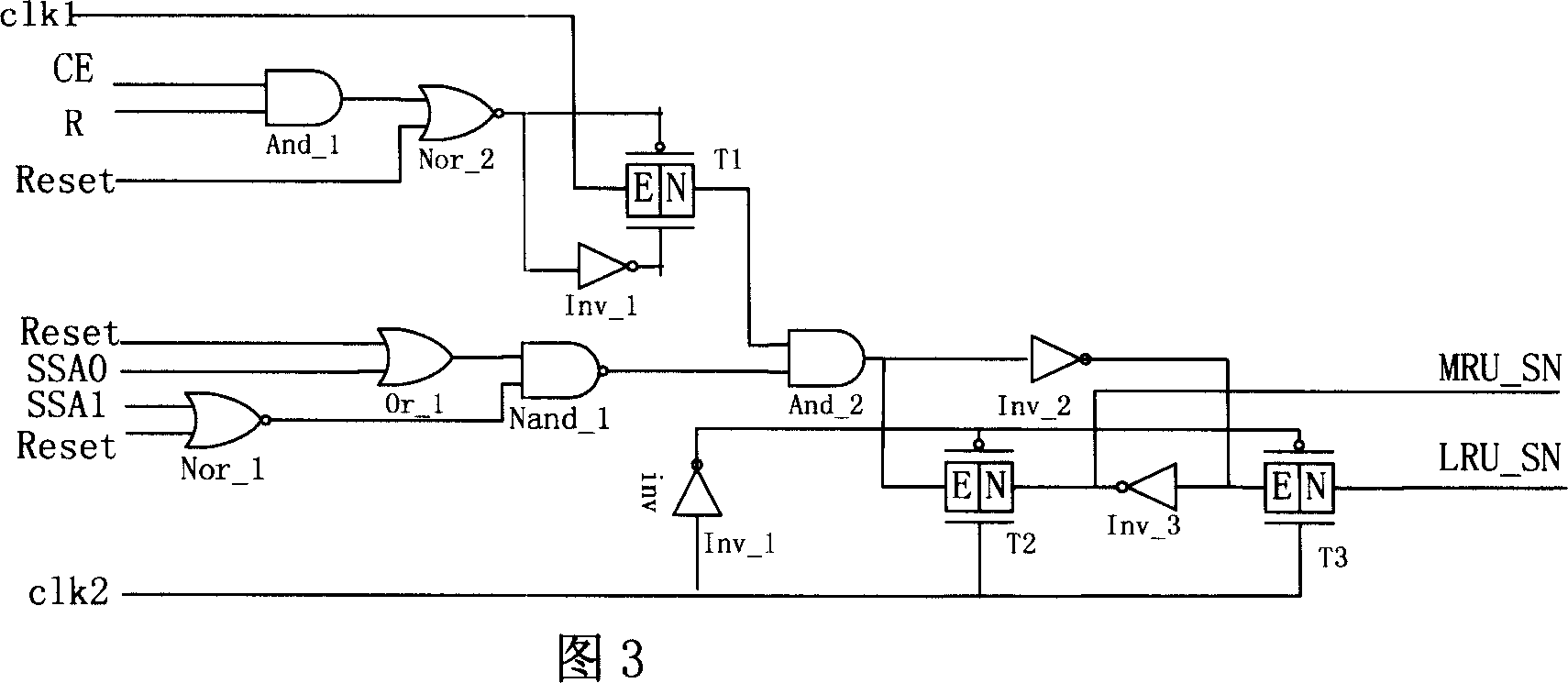

[0013] As shown in Figure 1, in the SMDSP signal processor, the instruction cache capacity is 64×32 words, which are divided into two 32 fields, and a 19-bit segment start address register is associated with each segment. Each word in the cache has a corresponding matching flag P bit, and P is 1, which means that the word in the cache is valid, otherwise it is invalid.

[0014] The structure of the instruction cache consists of a cache control register, cache segment start address register, match flag P bit, cache segment word memory, and LRU replacement stack. The cache control register is used to control or indicate the state of the cache. The cache segment start address register The segment address used to store the instruction address, the match flag P bit is used to identify whether a word in the segment has been aligned, the cache segment word memory is used to store instructions, and the LRU replacement stack is used to record the sequence of cache segment replacement. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com