Thin film transistor array panel, manufacturing method thereof, and mask therefor

a technology of thin film transistors and manufacturing methods, applied in the direction of identification means, semiconductor/solid-state device details, instruments, etc., can solve the problems of large contact resistance, frequent undercutting of blanket etching, and corrosion of al containing metals

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

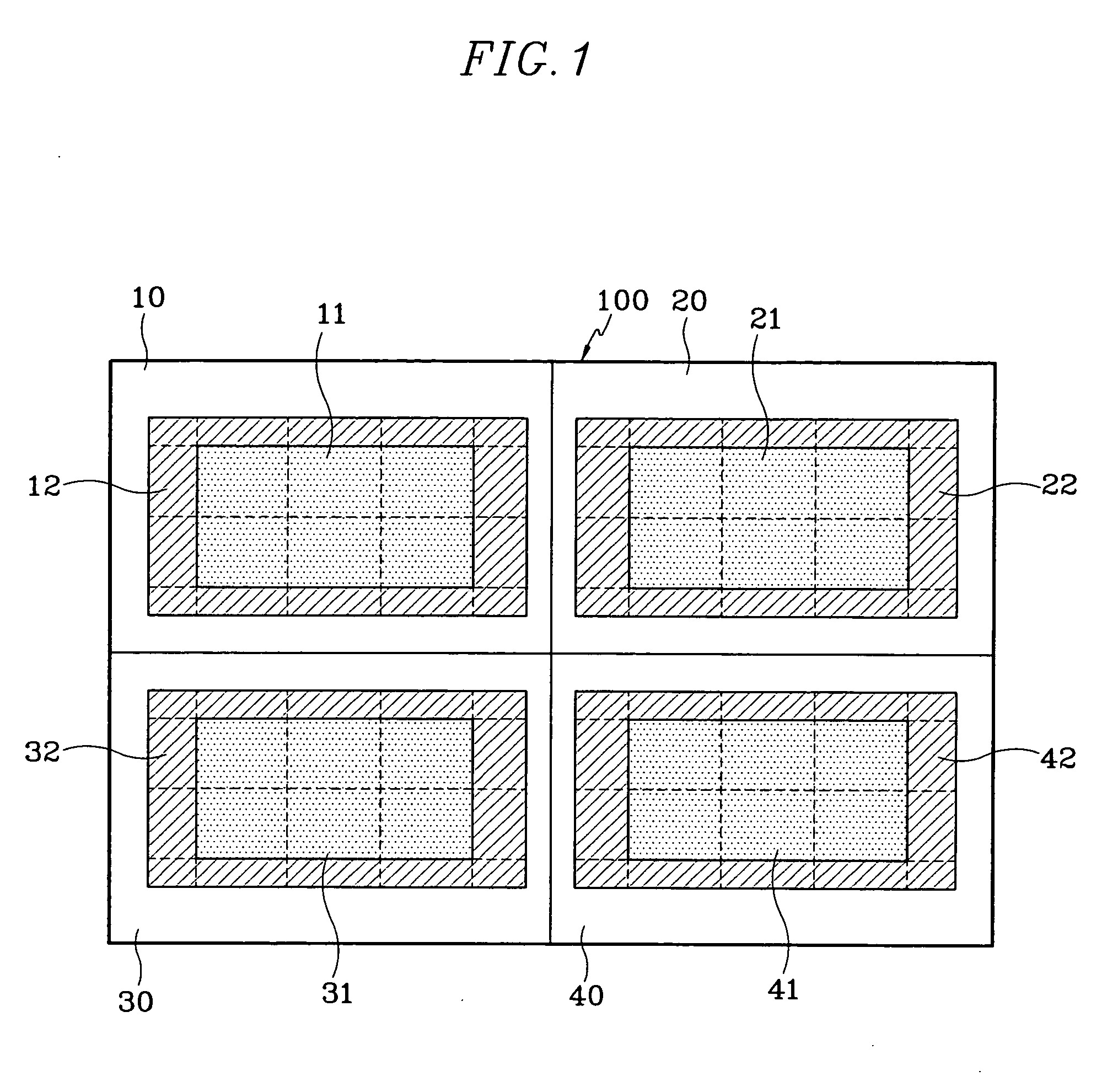

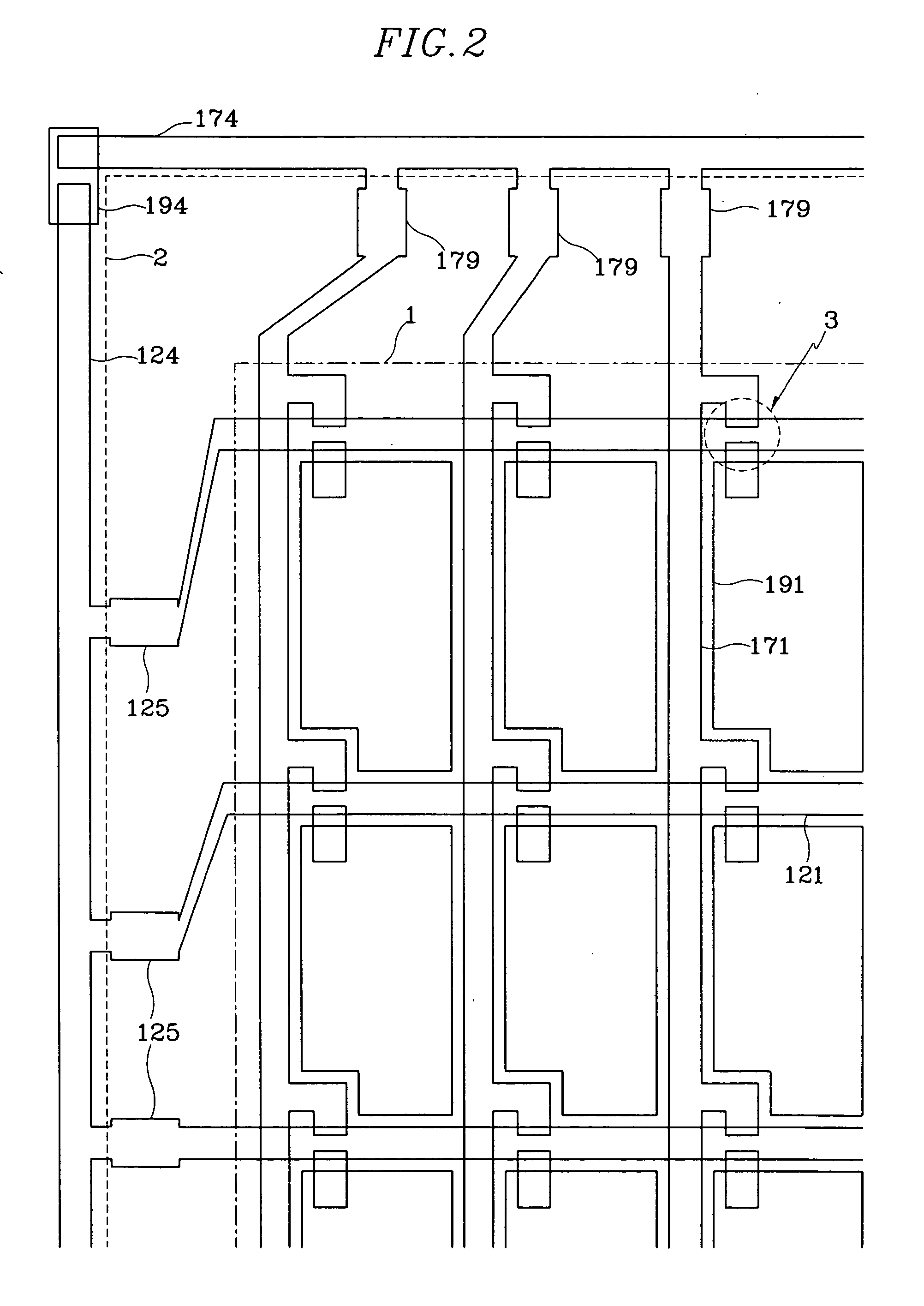

[0065] A TFT array panel for an LCD will be described in detail with reference to FIGS. 3 and 4 as well as FIGS. 1 and 2.

[0066] A TFT array panel for an LCD will be described in detail with reference to FIGS. 3 and 4 as well as FIGS. 1 and 2.

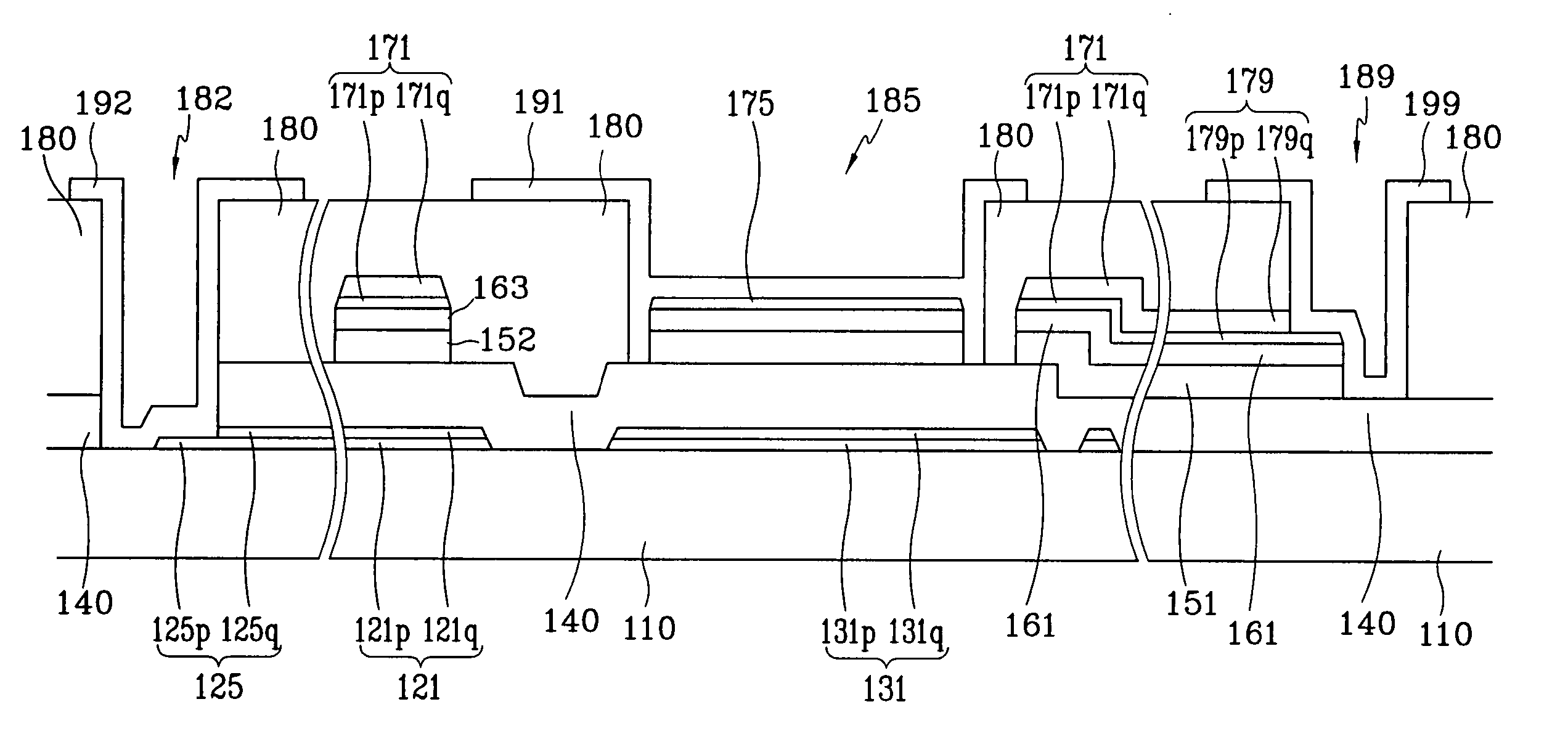

[0067] FIG. 3 is an exemplary layout view of TFTs, pixel electrodes, portions of signal lines located on the display area and expansions of the signal lines located on the peripheral area of the exemplary TFT array panel shown in FIG. 2 according to an embodiment of the present invention, and FIG. 4 is a sectional view of the TFT array panel shown in FIG. 3 taken along the line IV-IV'.

[0068] A plurality of gate lines 121 for transmitting gate signals and a gate shorting bar 124 extending substantially in a longitudinal direction are formed on an insulating substrate 110. Each gate line 121 extends substantially in a transverse direction and a plurality of portions of each gate line 121 form a plurality of gate electrodes 123. Each gate line 121 ...

1st embodiment

Method

[0094] A method of manufacturing the TFT array panel shown in FIGS. 1-4 according to an embodiment of the present invention will be now described in detail with reference to FIGS. 5A to 12 as well as FIGS. 1-4.

[0095] FIGS. 5A, 6A, 7A and 9A are layout views of the TFT array panel shown in FIGS. 1-4 in intermediate steps of a manufacturing method thereof according to an embodiment of the present invention, and FIGS. 5B, 6B, 7B and 9B are sectional views of the TFT array panel shown in FIGS. 5A, 6A, 7A and 9A taken along the lines VB-VB', VIB-VIB', VIIB-VIIB', and IXB-IXB', respectively. FIG. 8 is a sectional view of the TFT array panel shown in FIG. 7A taken along the line VIIB-VIIB' in the step of the manufacturing method following the step shown in FIG. 7B, and FIGS. 11 and 12 are sectional views of the TFT array panel shown in FIG. 9A in the steps of the manufacturing method following the step shown in FIG. 9B. FIG. 10 illustrates alignment between slits of a mask and a drai...

2nd embodiment

Method

[0121] Now, a method of manufacturing the TFT array panel shown in FIGS. 13-15 according to an embodiment of the present invention will be described in detail with reference to FIGS. 16A-25B as well as FIGS. 13-15.

[0122] FIG. 16A is a layout view of a TFT array panel shown in FIGS. 13-15 in the first step of a manufacturing method thereof according to an embodiment of the present invention; FIGS. 16B and 16C are sectional views of the TFT array panel shown in FIG. 16A taken along the lines XVIB-XVIB' and XVIC-XVIC', respectively; FIGS. 17A and 17B are sectional views of the TFT array panel shown in FIG. 16A taken along the lines XVIB-XVIB' and XVIC-XVIC', respectively, and illustrate the step following the step shown in FIGS. 16B and 16C; FIG. 18A is a layout view of the TFT array panel in the step following the step shown in FIGS. 17A and 17B; FIGS. 18B and 18C are sectional views of the TFT array panel shown in FIG. 18A taken along the lines XVIIIB-XVIIIB' and XVIIIC-XVIIIC'...

PUM

| Property | Measurement | Unit |

|---|---|---|

| distance | aaaaa | aaaaa |

| inclination angles | aaaaa | aaaaa |

| dielectric constant | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More