Crack stop for low k dielectrics

a dielectric material and crack stop technology, applied in the direction of electrical equipment, semiconductor devices, semiconductor/solid-state device details, etc., can solve the problem that the addition of edge seals has the disadvantage of taking up more area on the ic chip, and achieve the effect of preventing the propagation of cracks

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

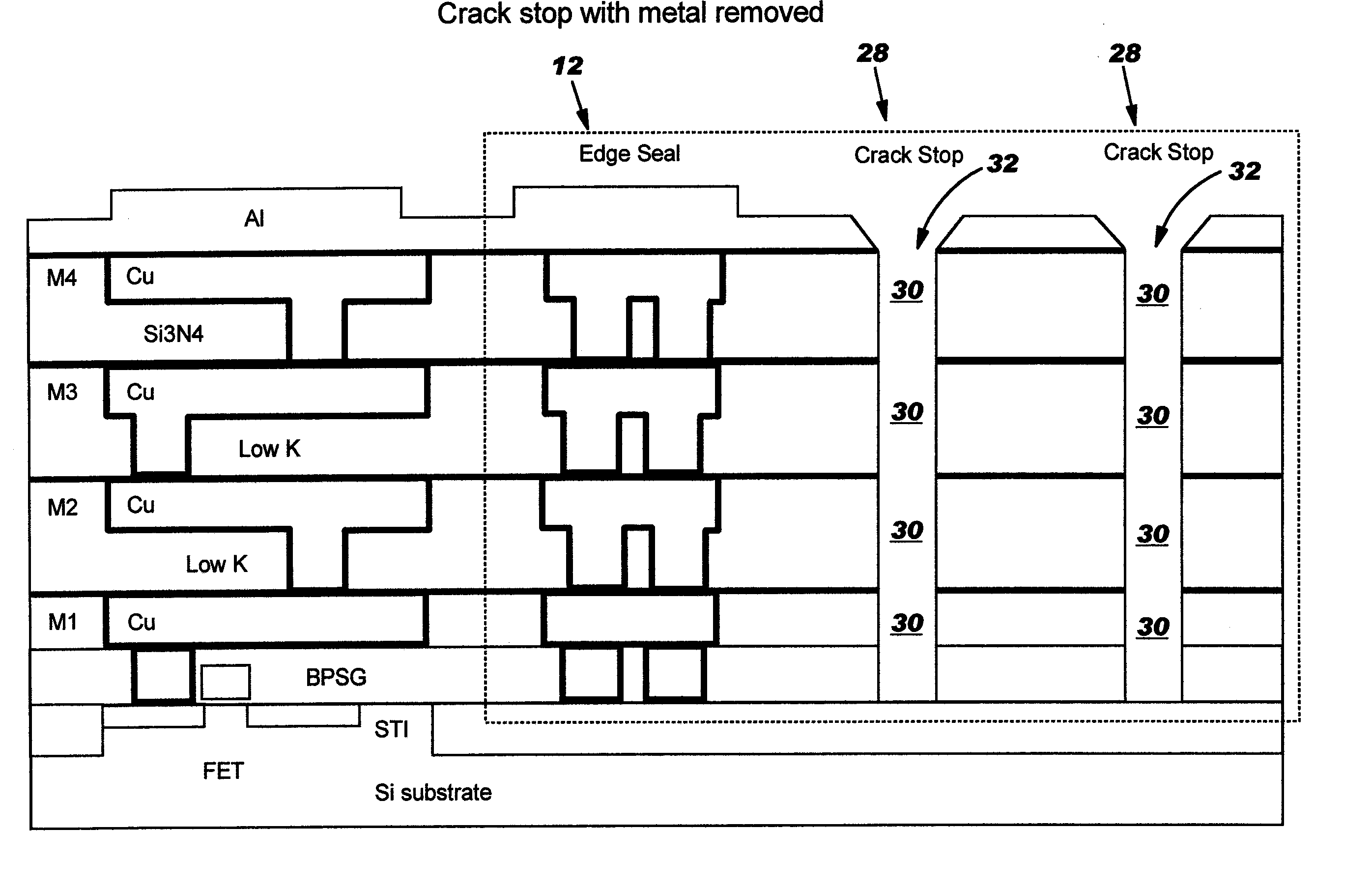

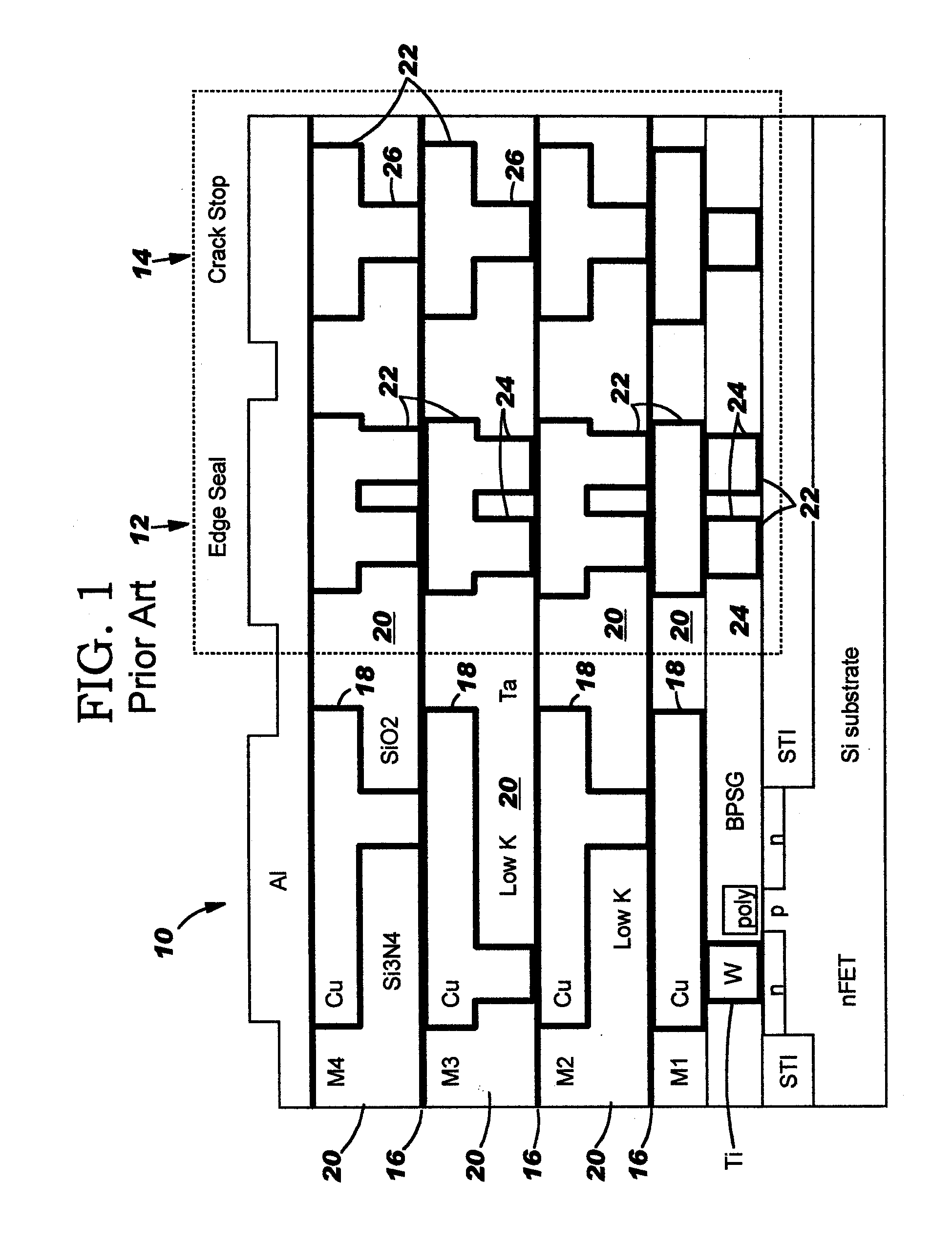

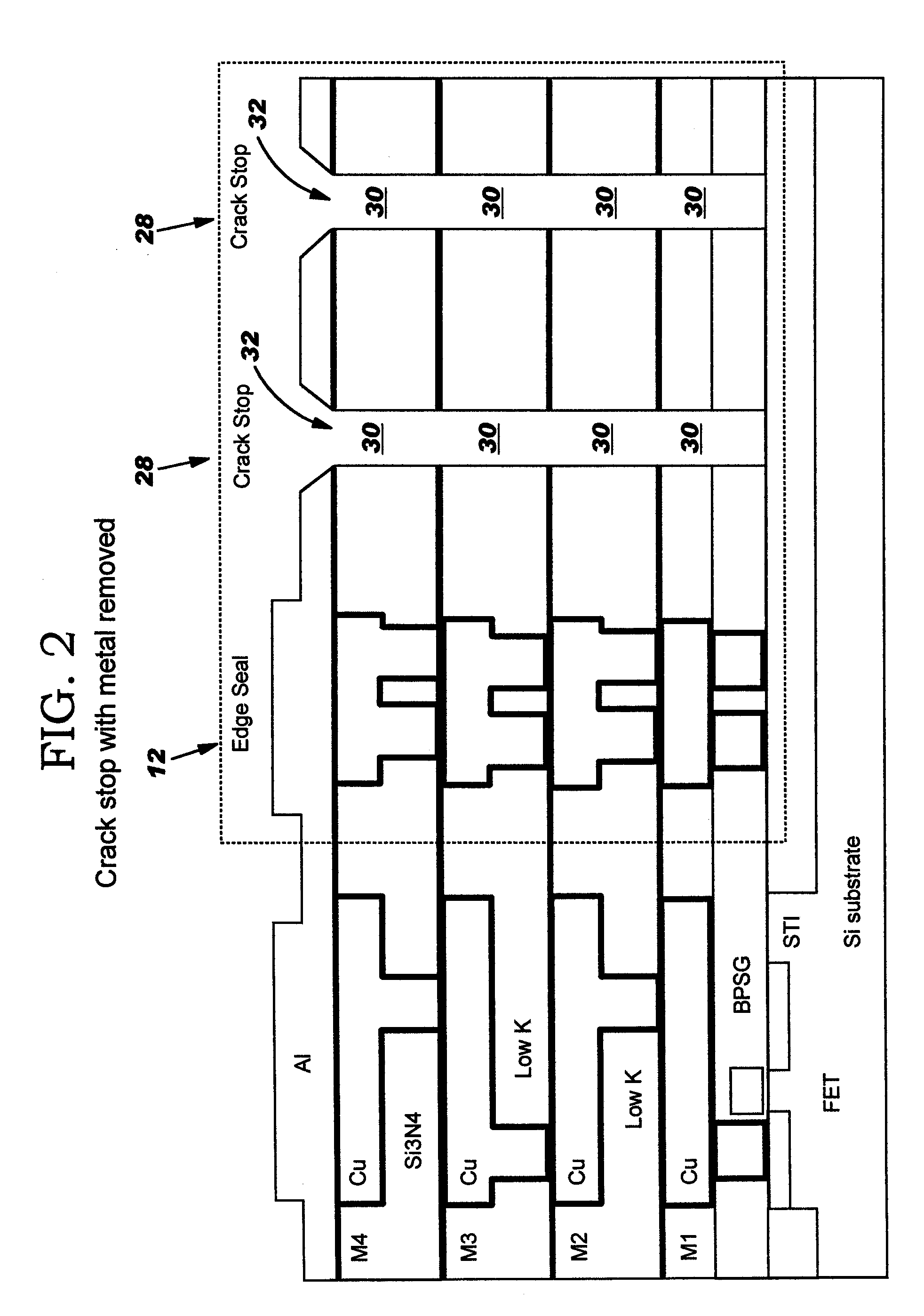

[0014]FIG. 1 illustrates a prior art metal stack crack stop which has been used in copper interconnect technology on IC chips to prevent the propagation of cracks formed during dicing of the IC chip into brittle BEOL dielectrics of the IC chip. The active circuit area 10 of the IC chip is formed generally to the left in FIG. 1, and is bordered by a moisture barrier / edge seal 12 formed along its outer peripheral edge, and a metal stack crack stop 14 formed outside of the edge seal.

[0015] The IC chip is formed on a silicon Si substrate, and an exemplary active area of the IC chip is shown on the left side of FIG. 1. The exemplary active area includes an npn nFET transistor device surrounded by shallow trench isolation STI, with a poly conductor above the p gate, a titanium Ti or TiN liner formed around tungsten W above the left n region, and a layer of BPSG (borophospho silicate glass) above the right n region. The active area includes metal layers M1, M2, M3, M4, separated by cappin...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More