Ferroelectric random access memory capacitor and method for manufacturing the same

a random access memory and capacitor technology, applied in the field of semiconductor devices, can solve the problems of deterioration of the ferroelectric property of the feram capacitor, several shortcomings of the conventional method for manufacturing the feram capacitor, etc., and achieve the effect of enhancing the ferroelectric property and preventing the cracking of the ferroelectric layer

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

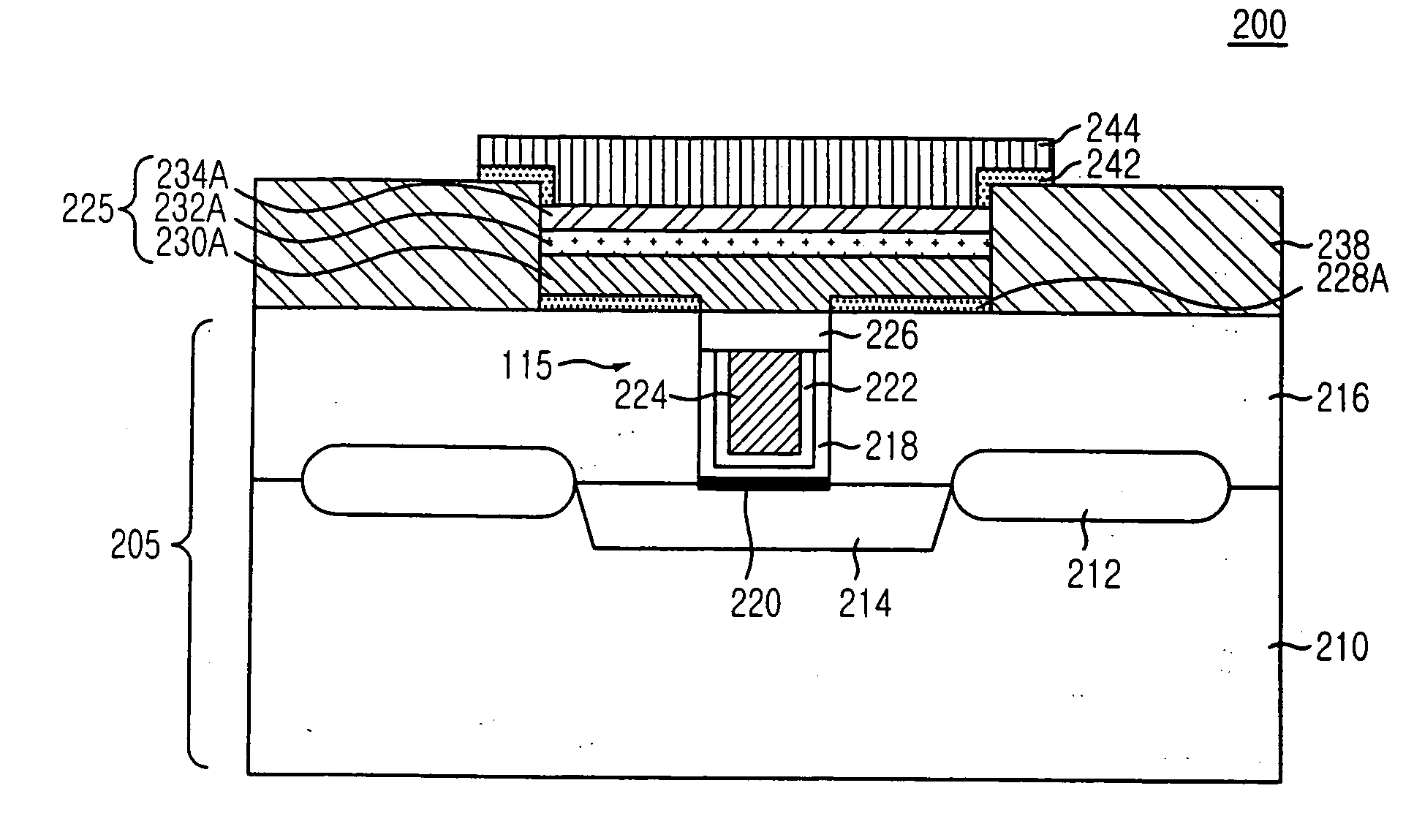

[0028] There are provided in FIG. 2, FIGS. 3A to 3F, FIG. 4 and FIG. 5 cross sectional views and a plane view setting forth a ferroelectric random access memory (FeRAM) capacitor and a method for manufacturing the same in accordance with a preferred embodiment of the present invention. It should be noted that like parts appearing in FIG. 2, FIGS. 3A to 3F, FIG. 4 and FIG. 5 are represented by like reference numerals.

[0029] Referring to FIG. 2, there is shown a cross sectional view illustrating an inventive FeRAM capacitor 200 with a merged top electrode plate line (MTP) structure including an active matrix 205, a capacitor stack 225, a second interlayer dielectric (ILD) 238 and a plate line 244. The active matrix 205 includes a semiconductor substrate 210 having field oxide (FOX) regions 212 and a source / drain region 214, a first ILD 216 formed on the semiconductor substrate 210 and a storage node contact 215 achieved after patterning the first ILD 216 into a predetermined configur...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More