Semiconductor memory system and method for the transfer of write and read data signals in a semiconductor memory system

a memory system and semiconductor technology, applied in the field of semiconductor memory systems, can solve the problems of excessively increasing the cost of such a system, unable to detect and correct errors, and unable to use the transfer of separate dqs signals for synchronization,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

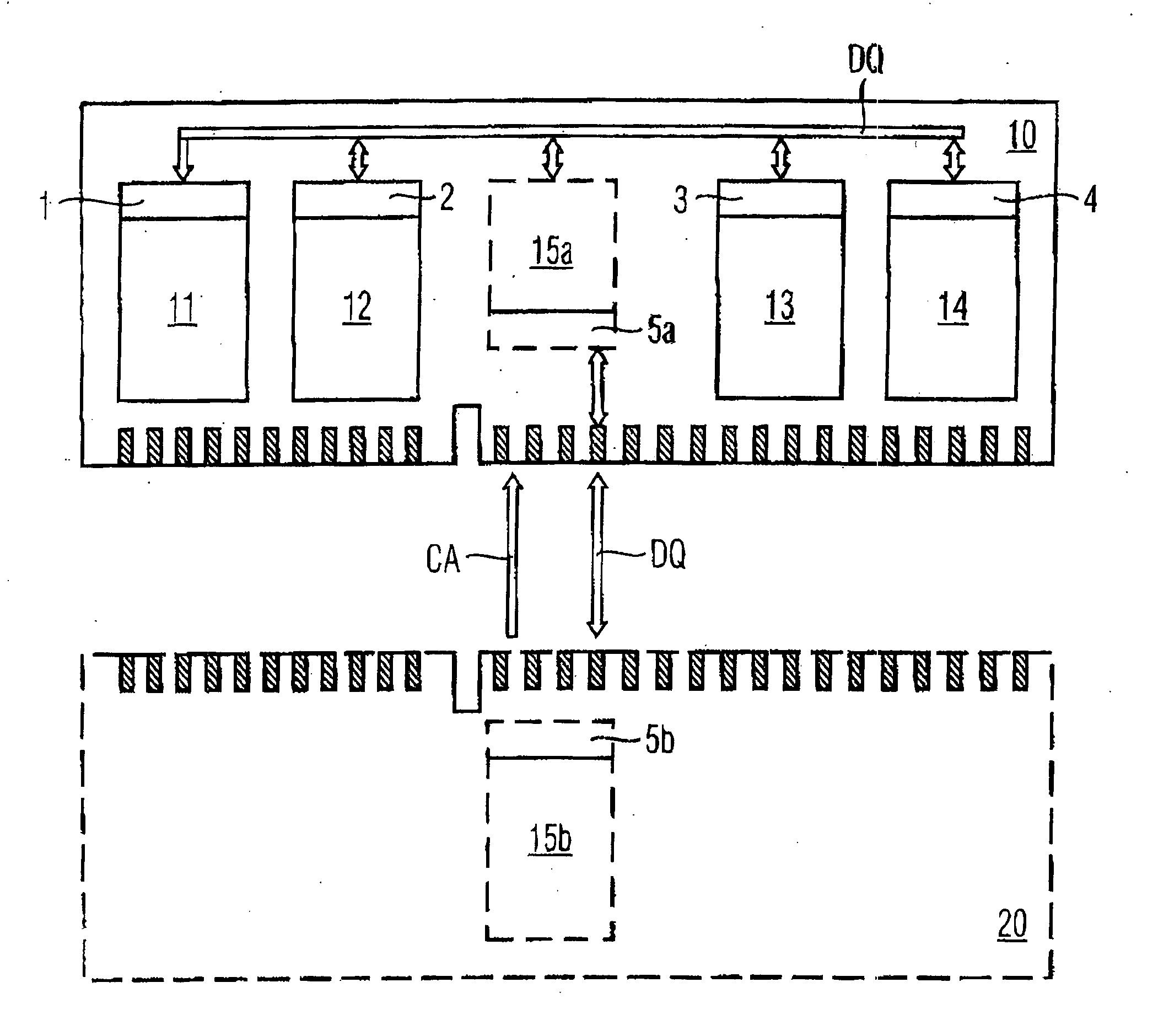

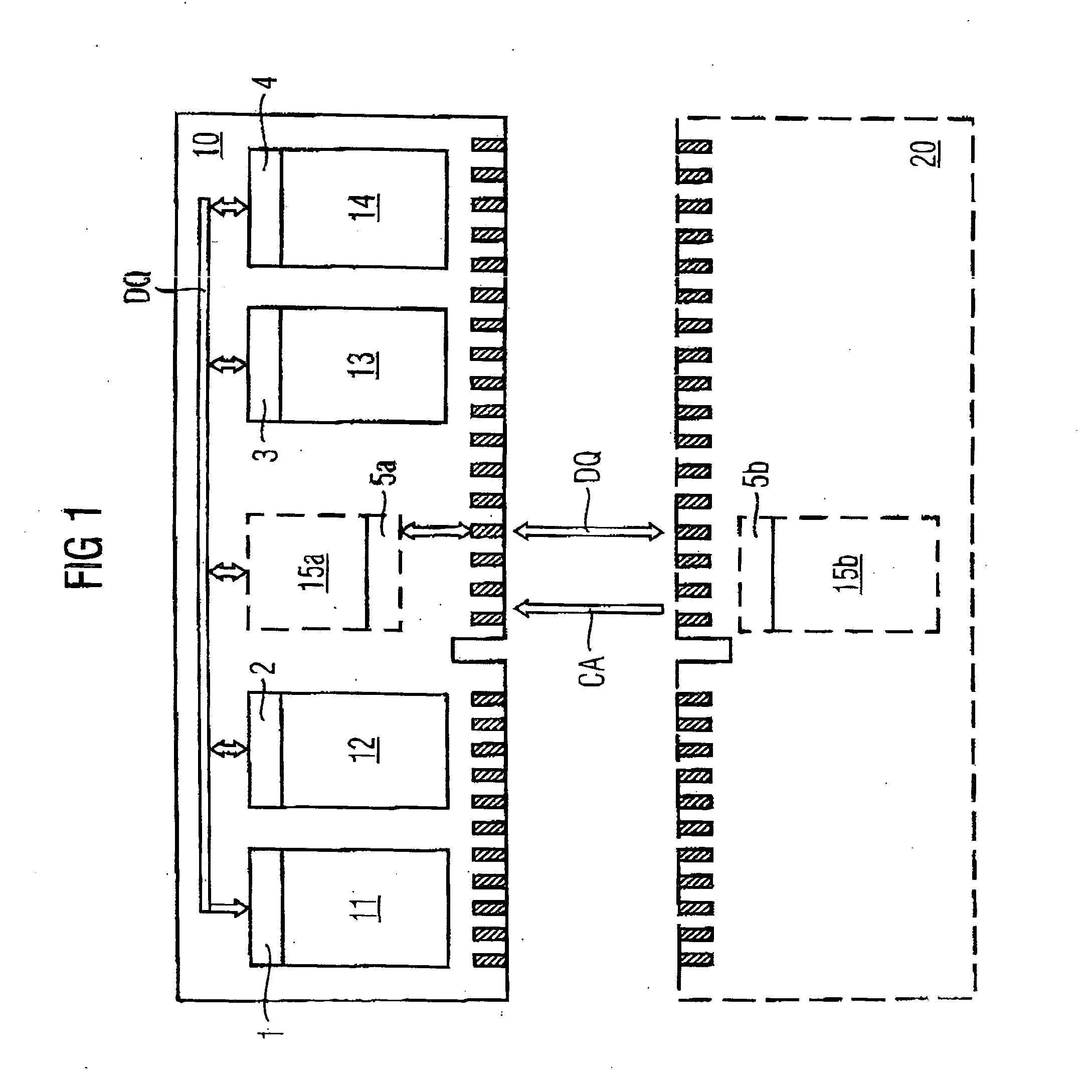

[0020] The following illustration of a preferred embodiment of the invention by means of FIGS. 1 and 2 will be preceded by a description of the prior art signal-time diagram of FIG. 3 illustrating a conventional method for the transfer of write and read data signals. According to this transfer method and on the basis of the fundamental clock of the frequency fb1 shown in the first line A, for example within a frequency range fb1=800-1600 MHz corresponding to a period length PPR—b1 of 1250-625 ps, and a fundamental clock of the frequency 1.5×fb1 that is shown in the second line B and is immediately derived from the fundamental clock according to line A, for example within a frequency range of 1333-2400 MHz corresponding to a period length of 750-416 ps, either a reference clock fref with a period length Tper—ref that is shown in the third line C is generated according to a “2N” rule which means that a CA unit interval is twice the period length of the fundamental clock according to t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More