Semiconductor device and method for fabricating the same

a semiconductor and semiconductor technology, applied in the direction of semiconductor devices, electrical devices, transistors, etc., can solve the problems of difficult to meet the overlay accuracy required for the impurity diffused layer, the margin for forming patterns cannot meet the requirement of downsizing the device pattern, and the device isolation by sti conducted independently in the peripheral circuit region and the flash memory cell region requires unrealistic step administration, etc., to achieve high accuracy and high accuracy. , the effect of high accuracy

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

A First Embodiment

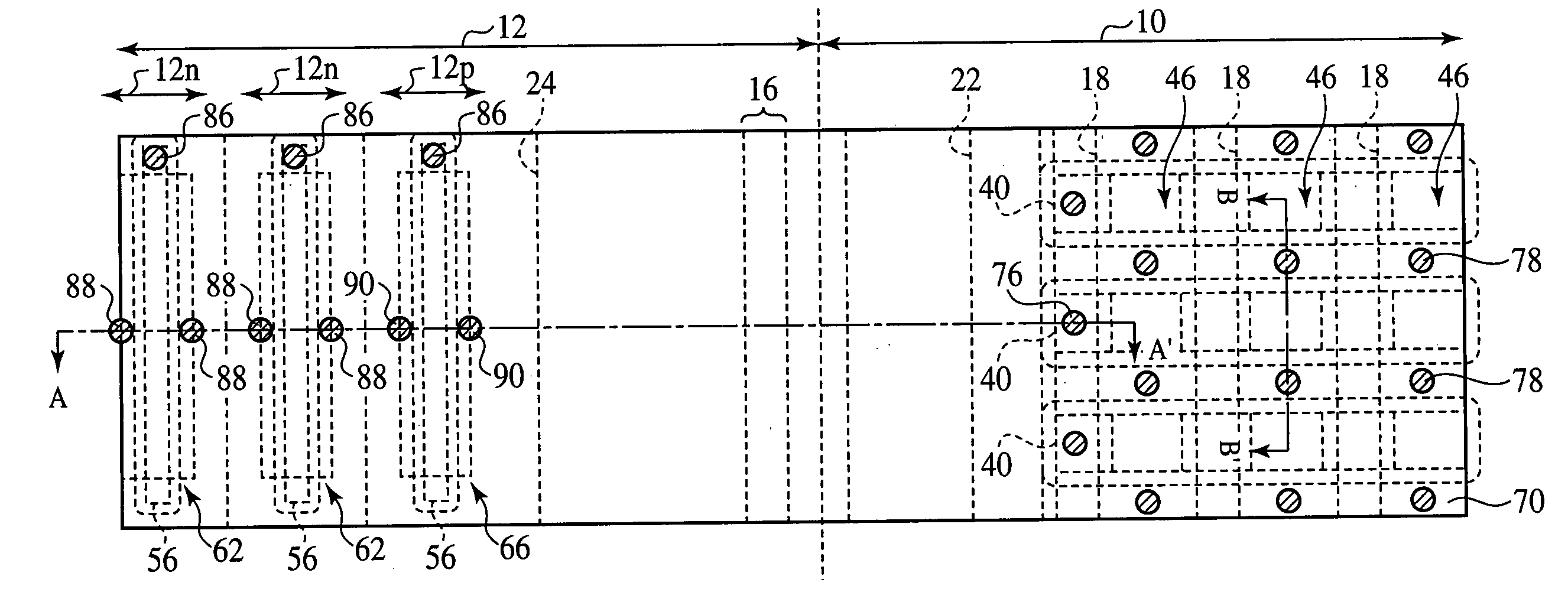

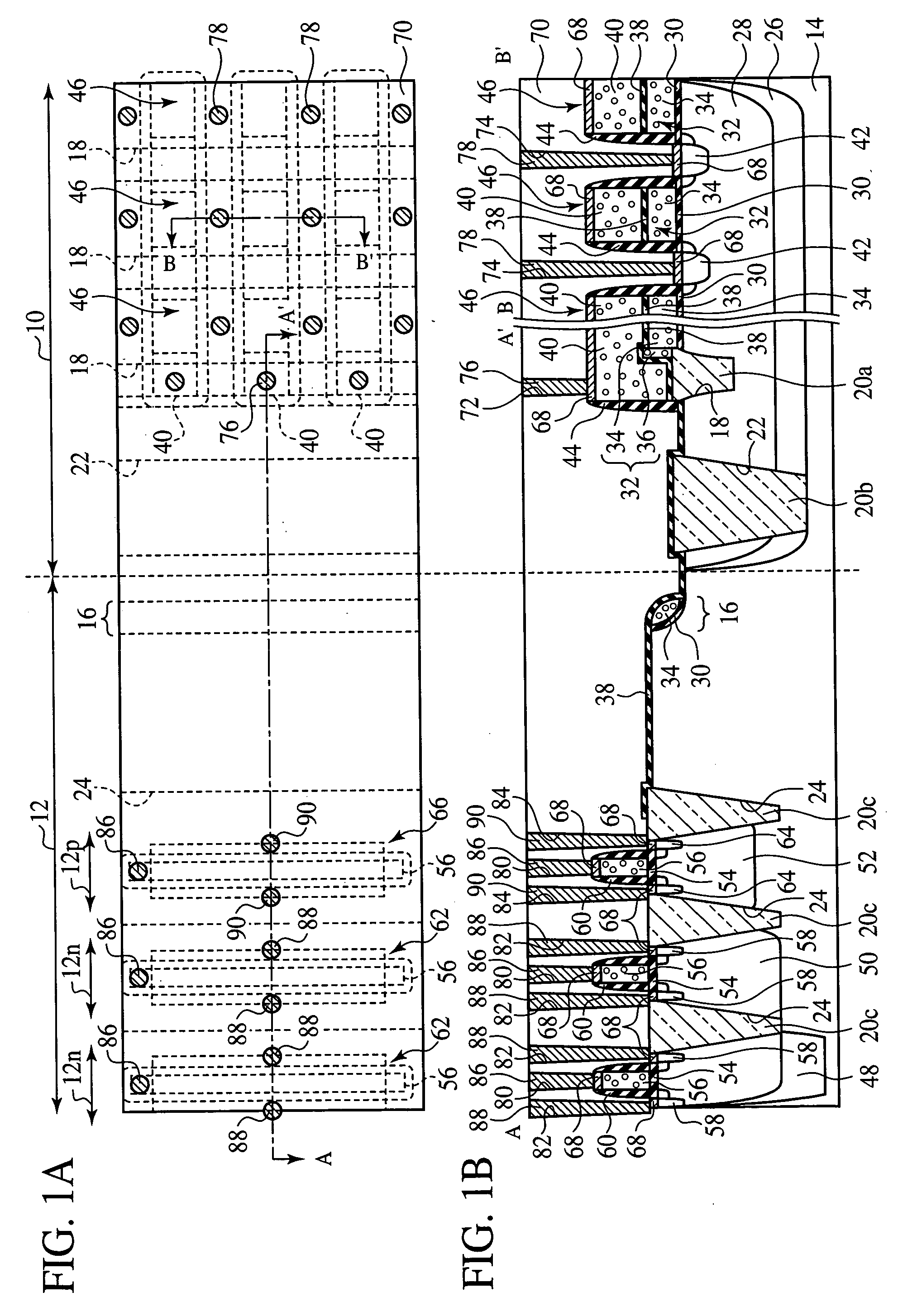

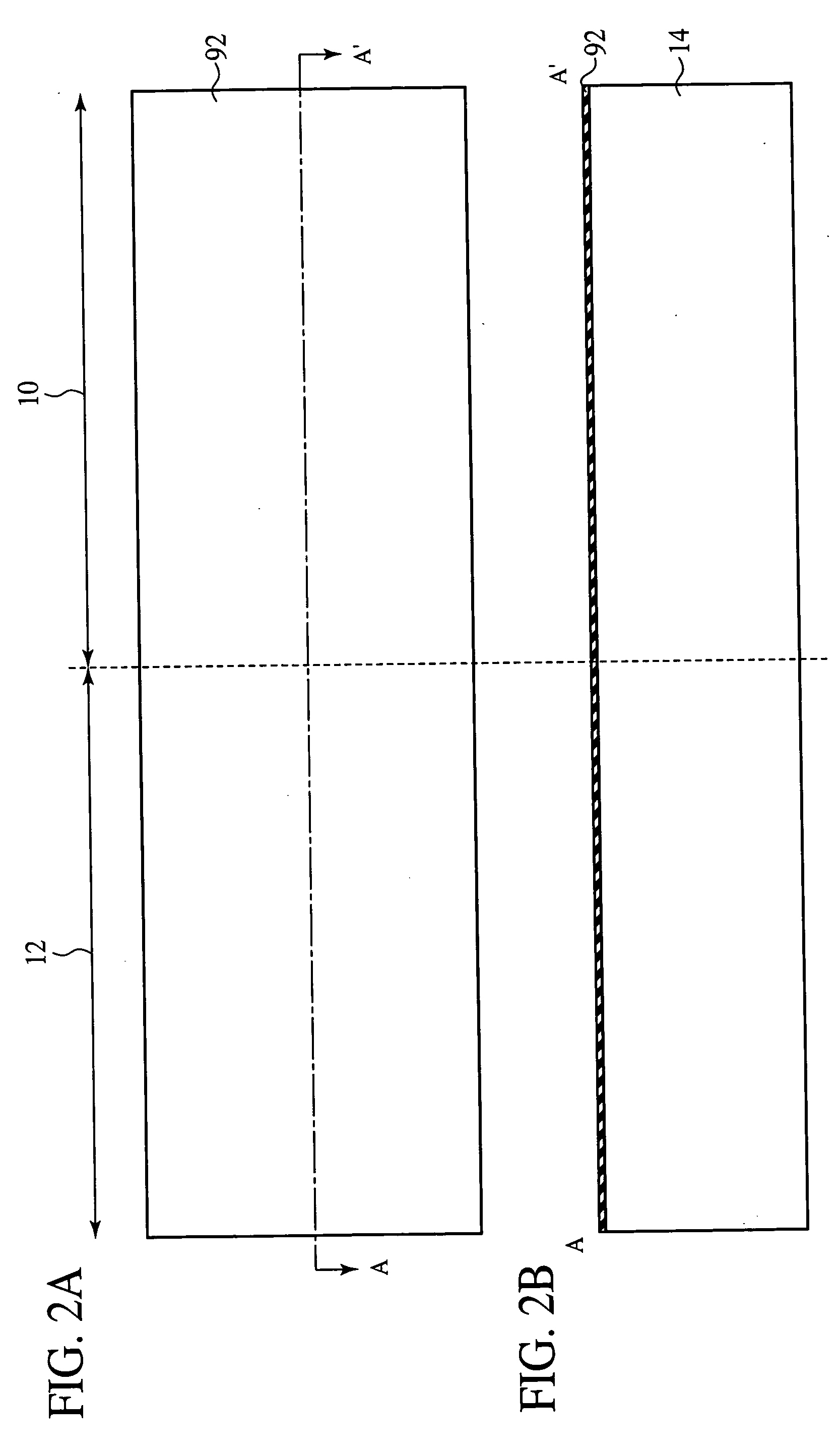

[0028] The semiconductor device and the method for fabricating the same according to a first embodiment of the present invention will be explained with reference to FIGS. 1A to 48. FIGS. 1A and 1B are diagrammatic views of the semiconductor device according to the present embodiment, which illustrate a structure thereof. FIGS. 2A to 41B are diagrammatic views of the semiconductor device according to the present embodiment in the steps of the method for fabricating the same, which illustrate the method. FIGS. 42A to 48 are sectional views of the semiconductor device in the steps of the method for fabricating the same, which illustrate the inconvenience caused when no step is formed in the surface of a silicon substrate.

[0029] First, the structure of the semiconductor device according to the present embodiment will be explained with reference to FIGS. 1A and 1B. FIG. 1A is a plan view of the semiconductor device, which illustrates the structure thereof. FIG. 1B is s...

second embodiment

A Second Embodiment

[0184] The semiconductor device and the method for fabricating the same according to a second embodiment of the present invention will be explained with reference to FIGS. 52A to 59B. FIGS. 52A and 52B are diagrammatic views of the semiconductor device according to the present embodiment, which illustrate a structure thereof. FIGS. 53A to 59B are sectional views of the semiconductor device according to the present embodiment in the steps of the method for fabricating the same, which illustrate the method. The same members of the present embodiment as those of the semiconductor device and the method for fabricating the same according to the first embodiment are represented by the same reference numbers not to repeat or to simplify their explanation.

[0185] First, the structure of the semiconductor device according to the present embodiment will be explained with reference to FIGS. 52A and 52B. FIG. 52A is a plan view of the semiconductor device according to the pre...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More