CMOS Circuits with High-K Gate Dielectric

a gate dielectric and high-k technology, applied in the field of electromechanical devices, can solve the problems of affecting the achievement of the desired threshold voltage value, affecting the performance improvement of devices of deeply sub-micron generation, and increasing complexity of technology

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

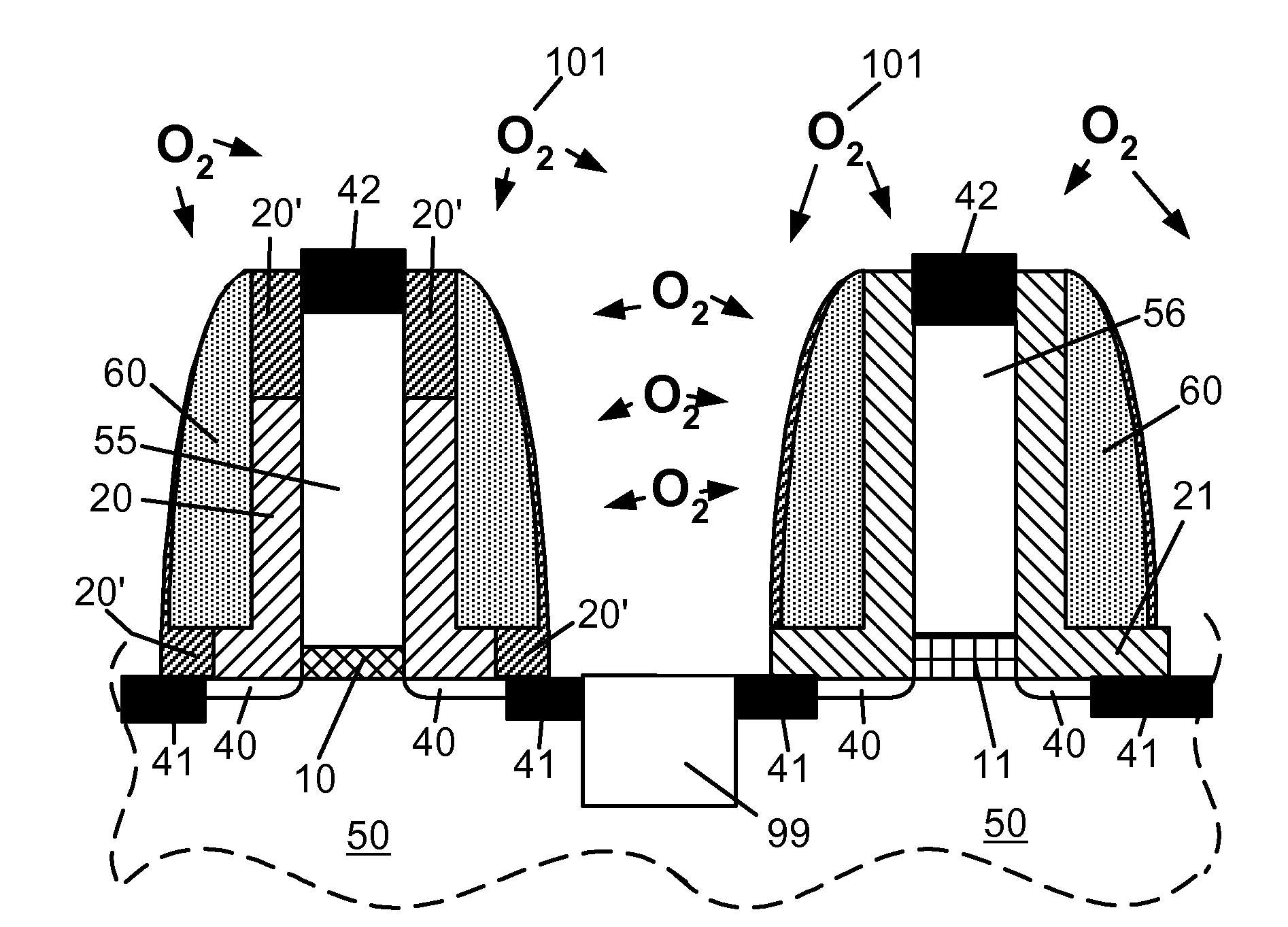

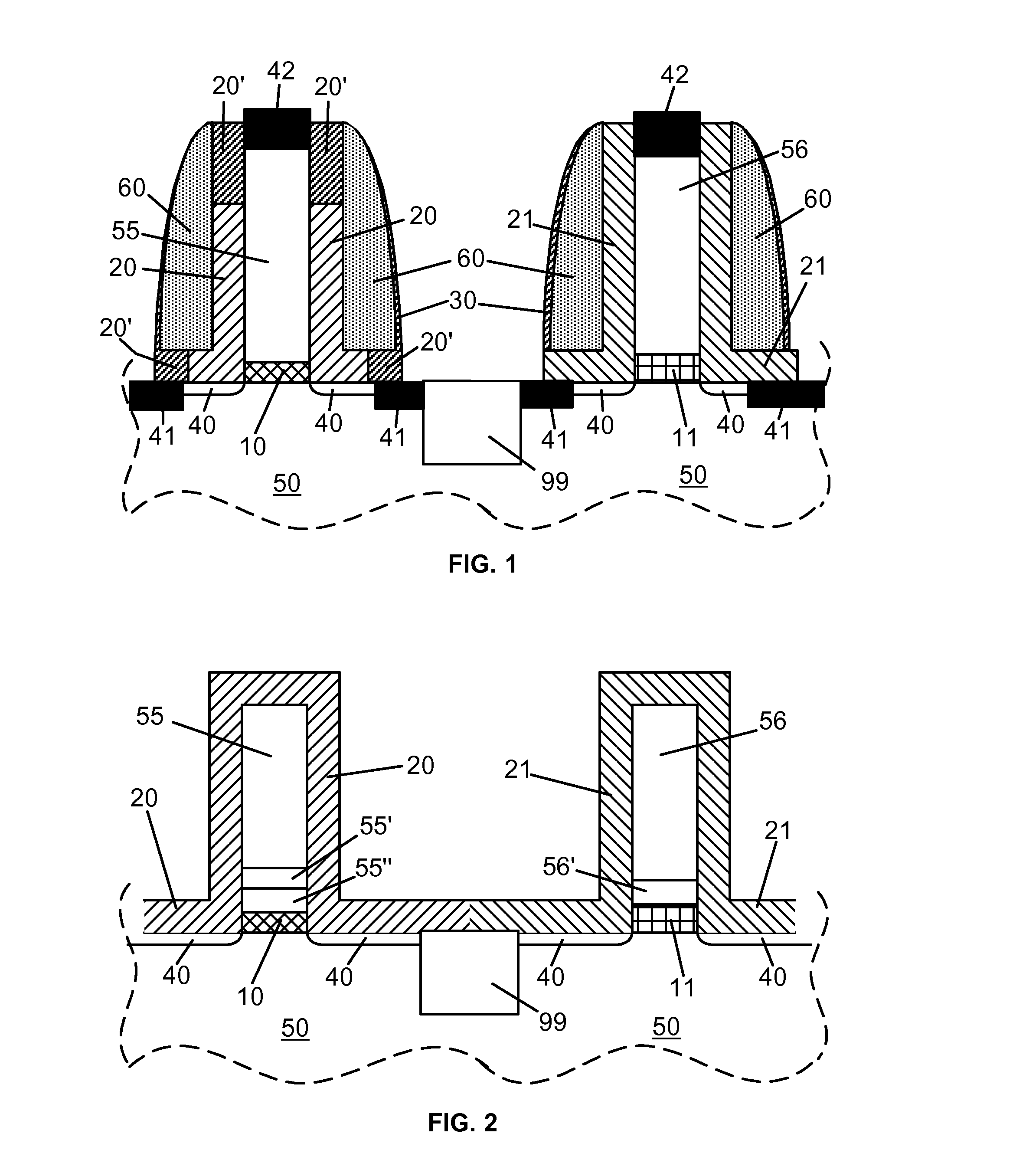

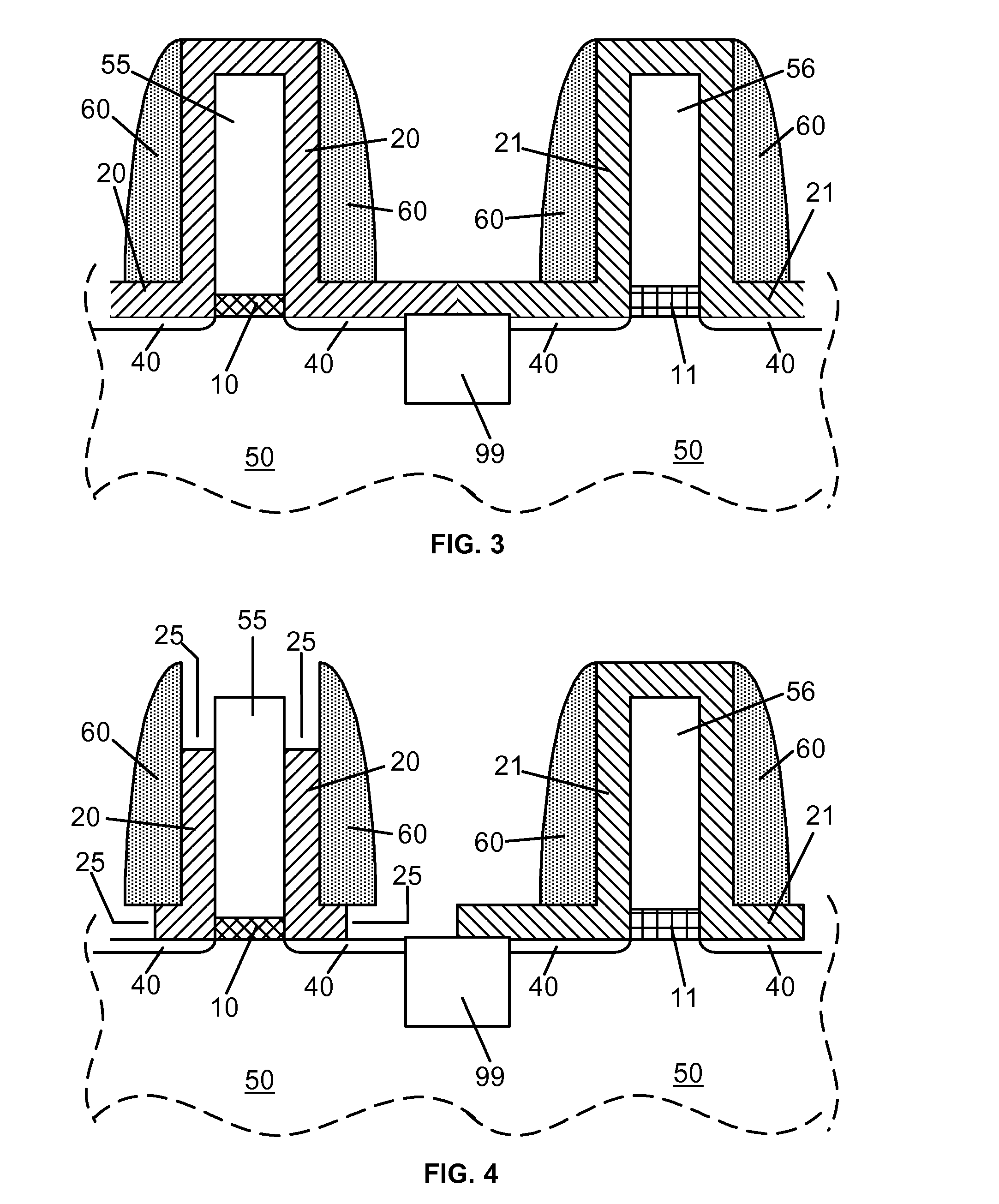

Image

Examples

Embodiment Construction

[0016]It is understood that Field Effect Transistor-s (FET) are well known in the electronic arts. Standard components of a FET are the source, the drain, the body in-between the source and the drain, and the gate. The body is usually part of a substrate, and it is often called substrate. The gate is overlaying the body and is capable to induce a conducting channel in the body between the source and the drain. In the usual nomenclature, the channel is hosted by the body. The gate is separated from the body by the gate insulator. There are two type of FET devices: a hole conduction type, called PFET, and an electron conduction type, called NFET. Often, but exclusively, PFET and NFET devices on the same chip are wired into CMOS circuits. A CMOS circuit contains at least one PFET and at least one NFET device. In manufacturing, or processing, when NFET and PFET devices are fabricated together on the same chip, one is dealing with CMOS processing and the fabrication of CMOS structures.

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More