Nonvolatile semiconductor memory device

a semiconductor memory and non-volatile technology, applied in information storage, static storage, digital storage, etc., can solve the problems of increased access time or occurrence of erroneous reading, inaccurate reading, and inability to quickly change the read current, etc., to achieve high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

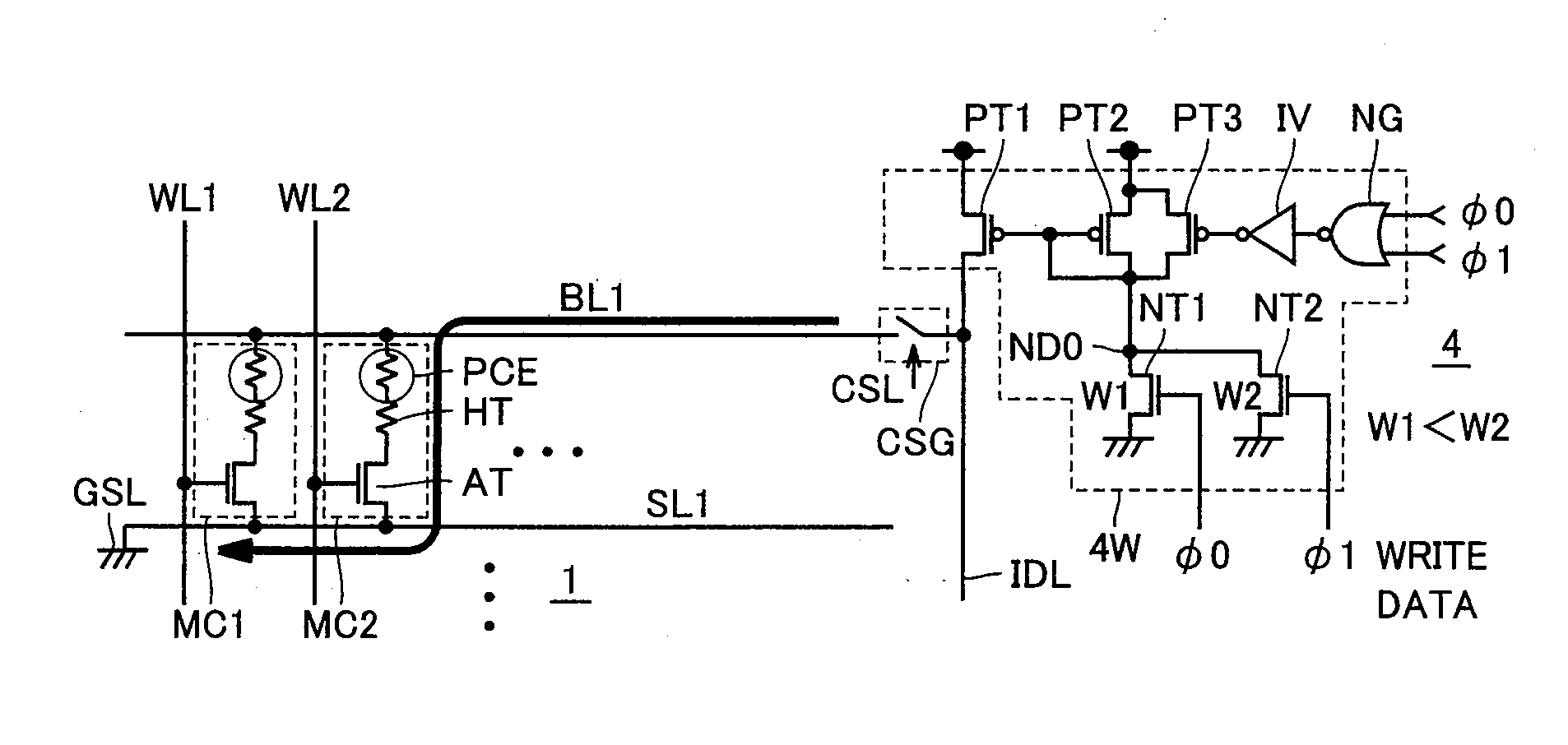

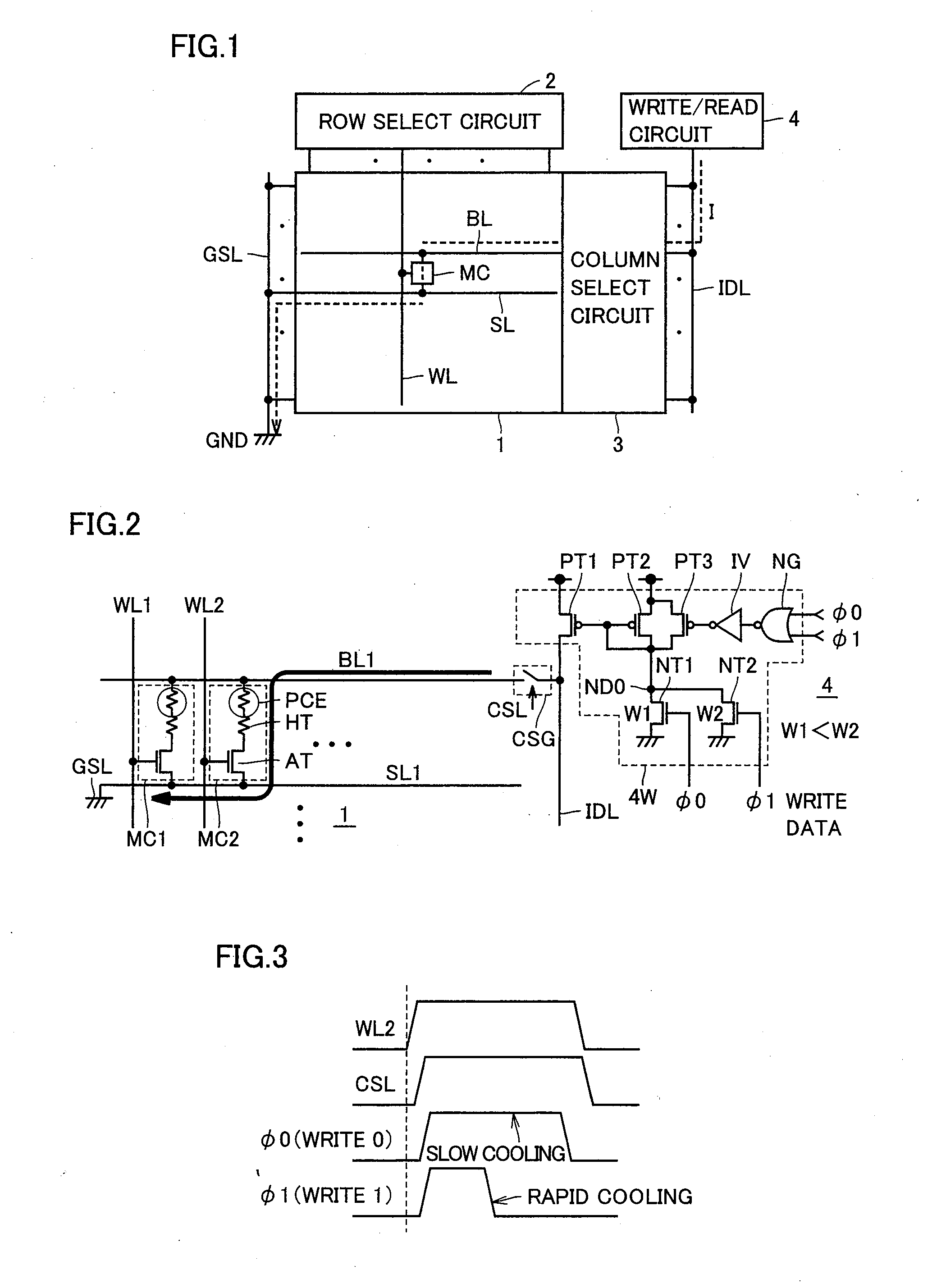

[0098]FIG. 1 schematically shows a configuration of a main portion of a nonvolatile semiconductor memory device according to a first embodiment of the invention. In FIG. 1, a nonvolatile semiconductor memory device includes a memory cell array 1 having memory cells MC arranged in rows and columns. In memory cell array 1, word lines WL are arranged corresponding to the respective rows of memory cells MC, and bit lines BL are arranged corresponding to the respective memory cell columns. Source lines SL are provided corresponding to and in parallel to bit lines BL, respectively. Source lines SL are coupled to a global source line GSL that extends along a first side of memory cell array 1 perpendicularly to bit line BL and source line SL. Global source line GSL is coupled to a ground node (ground pad; reference potential source). Memory cell MC, of which structure will be described later, includes a phase change material element as a storage element, and the phase change material elemen...

second embodiment

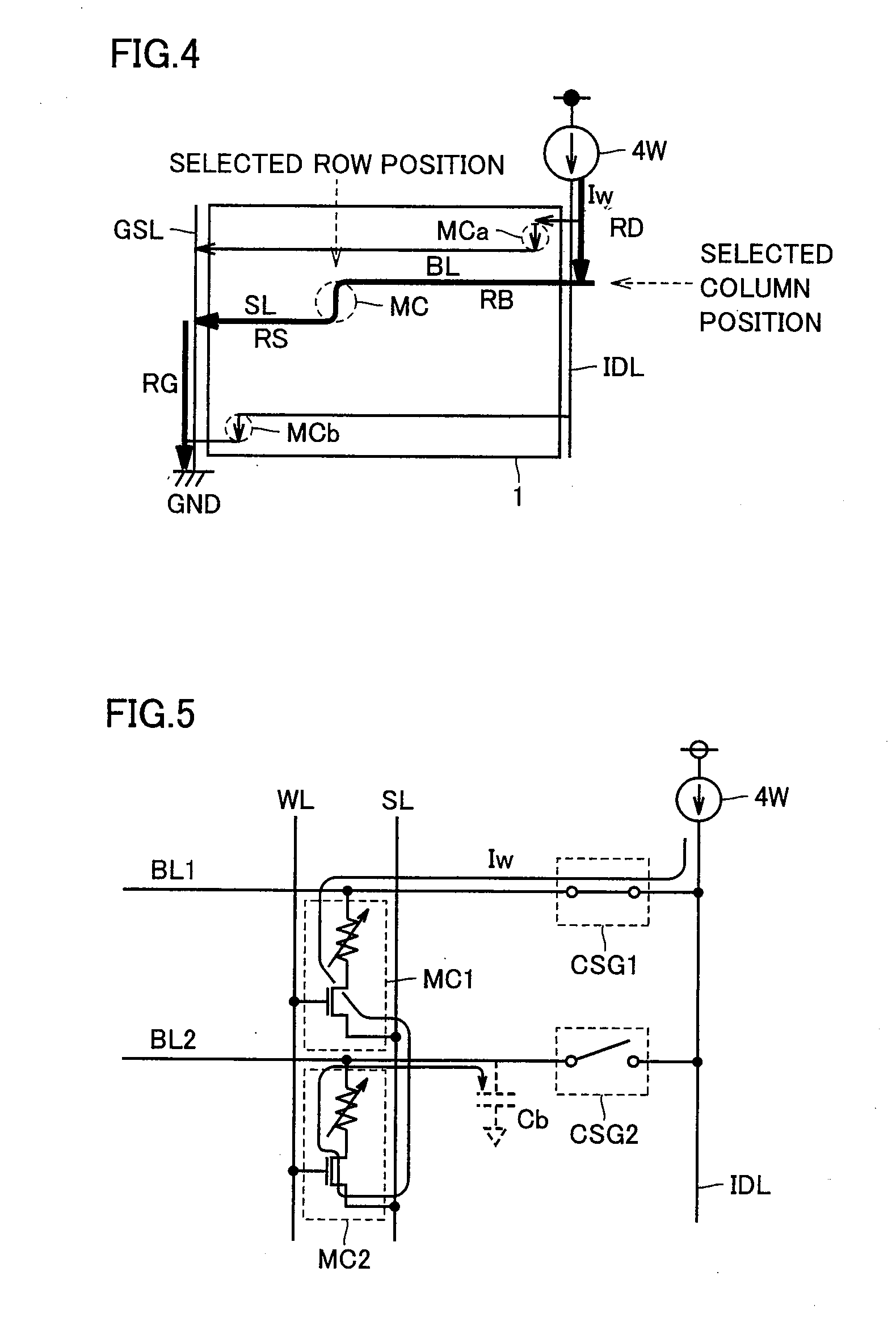

[0161]FIG. 12 shows a construction of an array portion of a nonvolatile semiconductor memory device according to a second embodiment of the invention. In FIG. 12, bit lines BL1-BL4 are arranged, and source line SL1 is arranged corresponding to and between bit lines BL1 and BL2, in parallel to them. Source line SL2 is arranged corresponding to and between bit lines BL3 and BL4, in parallel to them. Bit lines BL1-BL4 are coupled to an internal write data line WDB included in internal data line IDL via column select gates CSG1-CSG4, respectively.

[0162]Source lines SL1 and SL2 are commonly connected to global source line GSL. Memory cells MC11, MC12, . . . are connected to bit line BL1, memory cells MC21, MC22, . . . are connected to bit line BL2, memory cells MC31, MC32, . . . are connected to bit line BL3 and memory cells MC41, MC42, . . . are connected to bit line BL4.

[0163]Source line SL1 is shared between the memory cells connected to bit line BL1 and BL2. Thus, access transistors ...

third embodiment

[0285]FIG. 39 schematically shows a construction of a main portion of a nonvolatile semiconductor memory device according to a third embodiment of the invention. In FIG. 39, the nonvolatile semiconductor memory device includes, similarly to the first embodiment, memory cell array 1 having memory cells MC arranged in rows and columns, row select circuit 2 for driving a word line corresponding to the selected row in memory cell array 1 to the selected state, column select circuit 3 for producing a column select signal for a selected column in memory cell array 1 according to an address signal (not shown), and connecting the selected column to write data line WDB according to the column select signal, and write / read circuit 4 including variable current source 4W supplying the write current to write data line WDB in the data write operation.

[0286]In memory cell array 1, bit line BL is arranged corresponding to each column of memory cells MC, and word line WL is arranged corresponding to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More