Digital readout method and apparatus

a digital readout and readout technology, applied in the field of focal plane arrays for signal processing, can solve the problems of not being able to meet the above requirements in combination, not being able to meet the above requirements, and being unable to meet the requirements of specific analog designs,

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

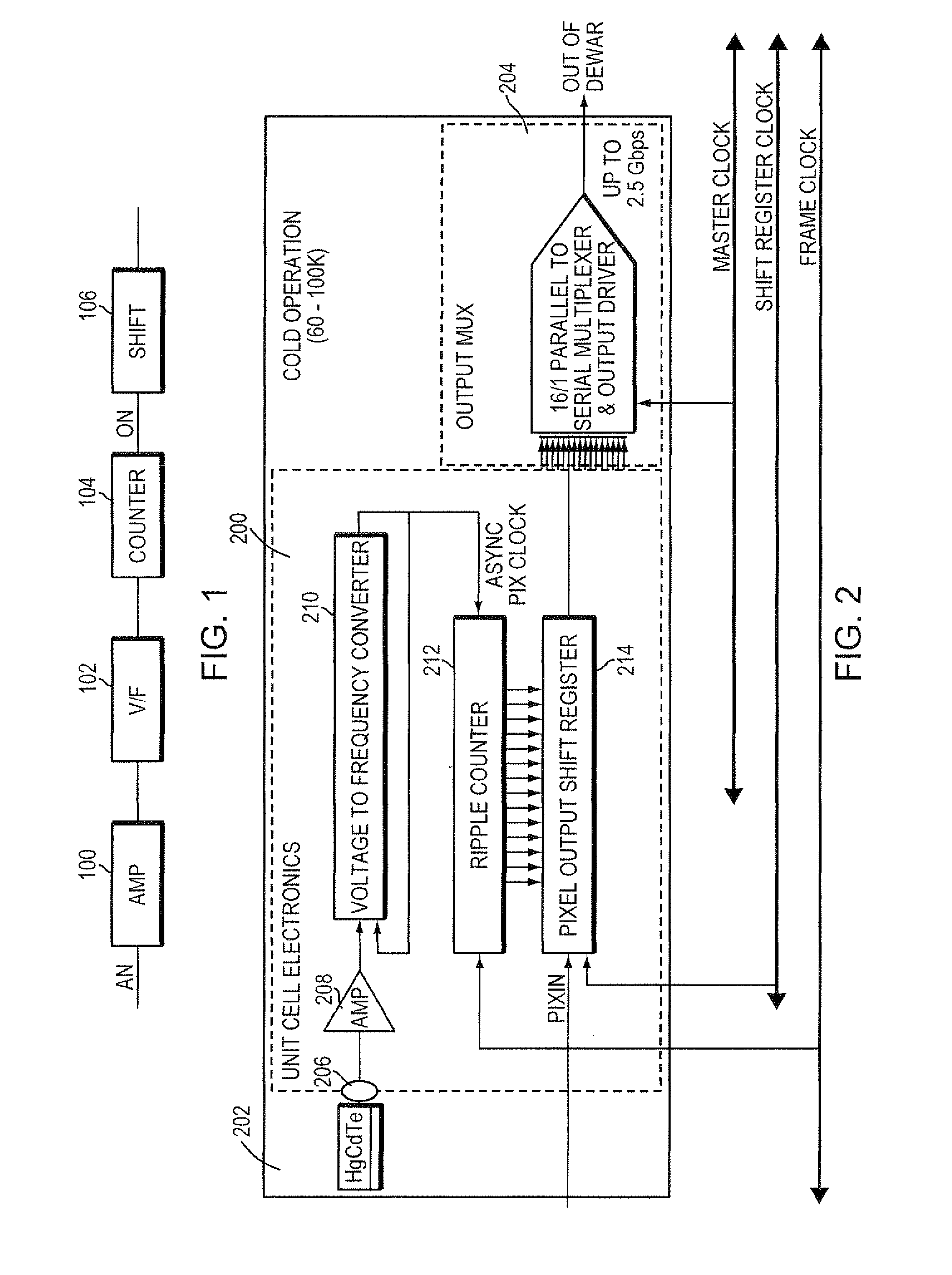

[0044]The block diagram of FIG. 1 illustrates the major components of an individual ADC, such as may be found employed within a focal plane sensor array in accordance with the principles of the present invention. An amplifier 100 (which is optional, depending upon the quality of the signal to be converted) accepts an analog signal, AN, for conversion, amplifies and conditions the signal, AN, and provides the conditioned signal to a voltage to frequency converter (V-to-F) 102. In illustrative embodiments the amplifier 100 may be a direct injection, buffered direct injection, source-follower, or transimpedance amplifier, for example. The voltage-to-frequency converter 102 converters the voltage signal from the amplifier to a serial digital signal, the frequency of which is representative of the voltage input. The digital output of the voltage-to-frequency converter is routed to a counter 104, where the digital stream is counted. The resulting count, DN, is a digital signal the magnitu...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More