Interface apparatus for semiconductor integrated circuit and interfacing method thereof

a technology of integrated circuits and interface apparatuses, applied in the direction of logic circuit coupling/interface arrangements, single output arrangements, pulse techniques, etc., can solve the problems of complex interpolation and oversampling processes that are too complicated to be simply realized in the output block, and may occur bit errors

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

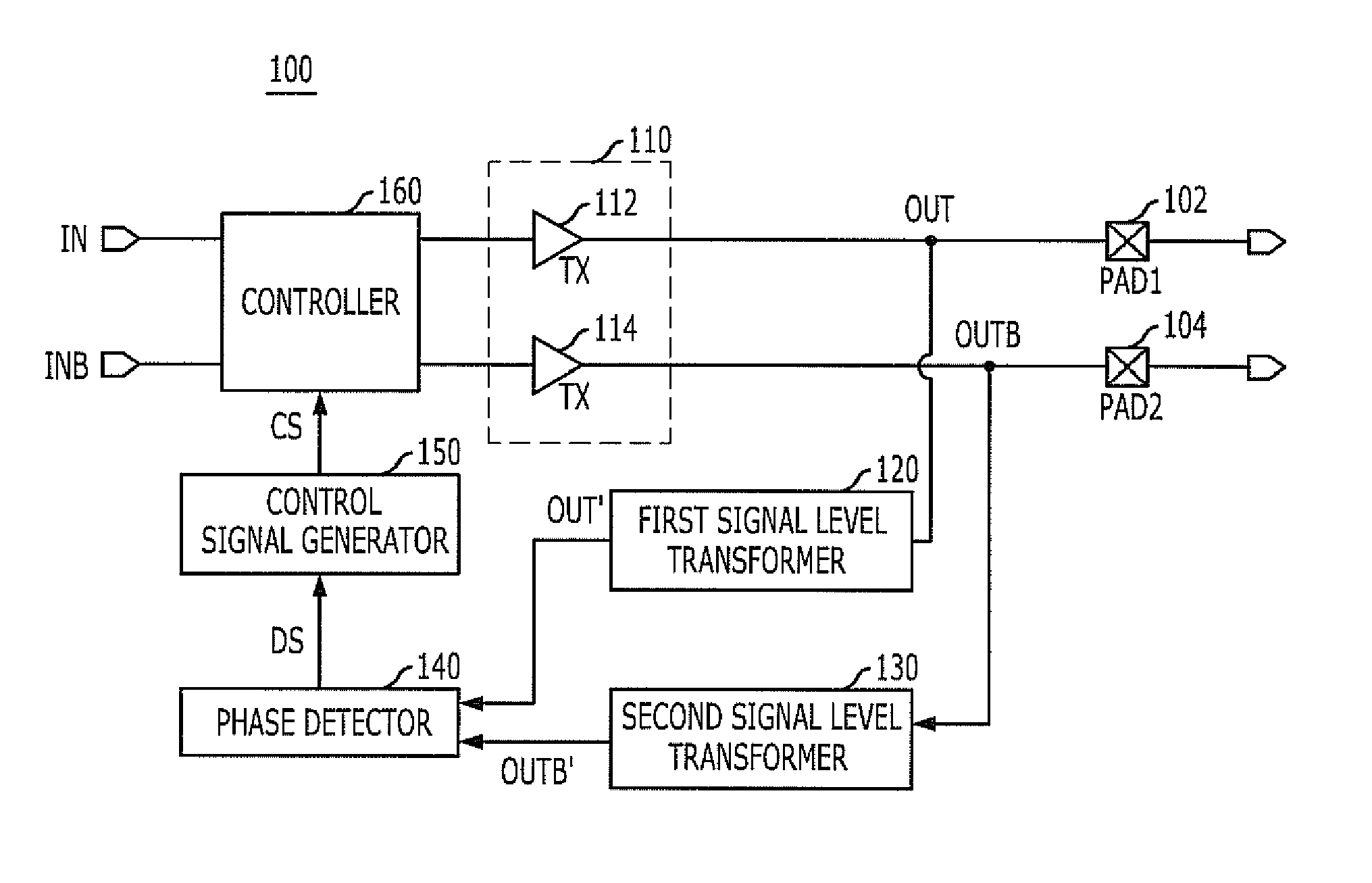

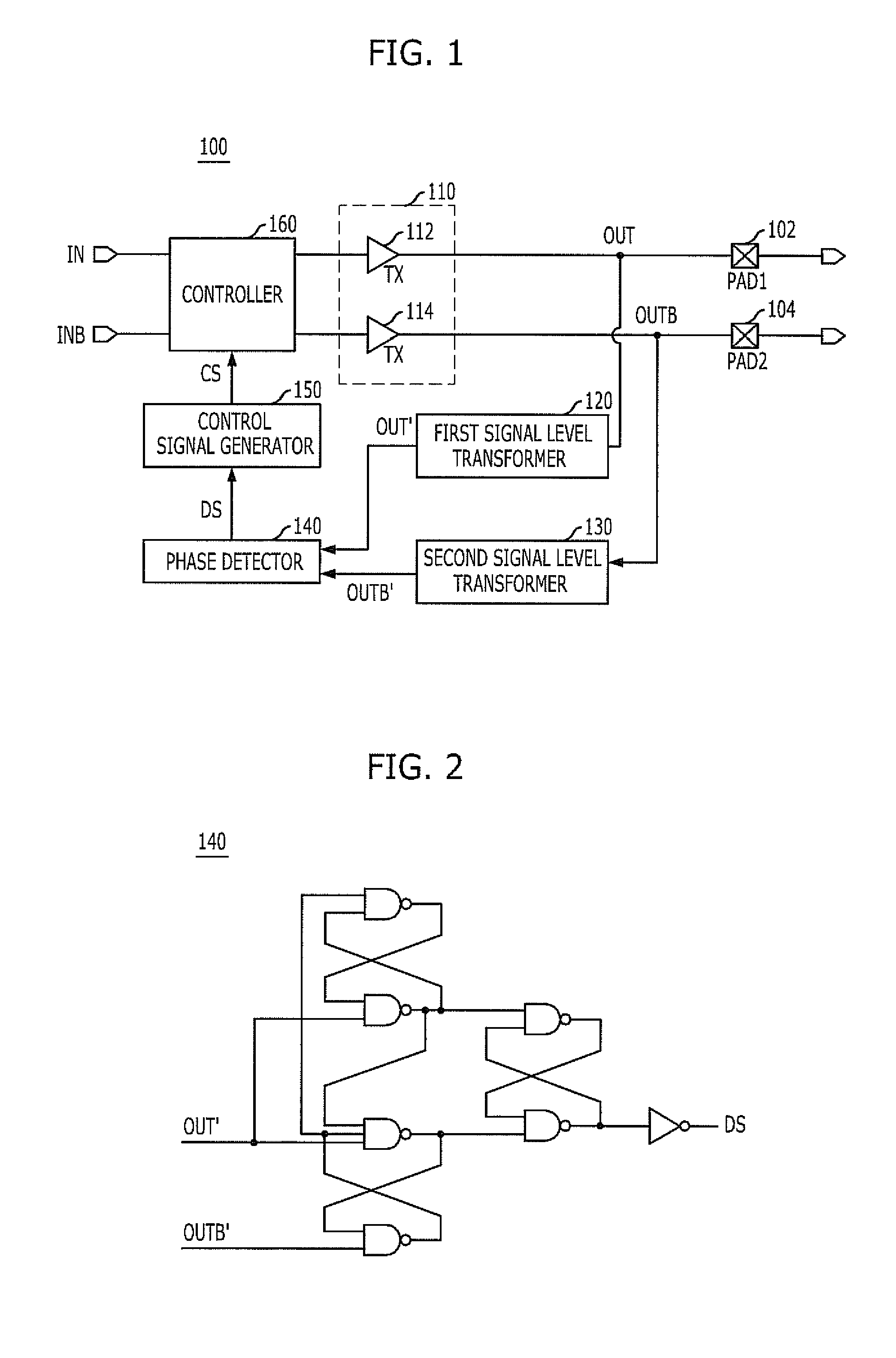

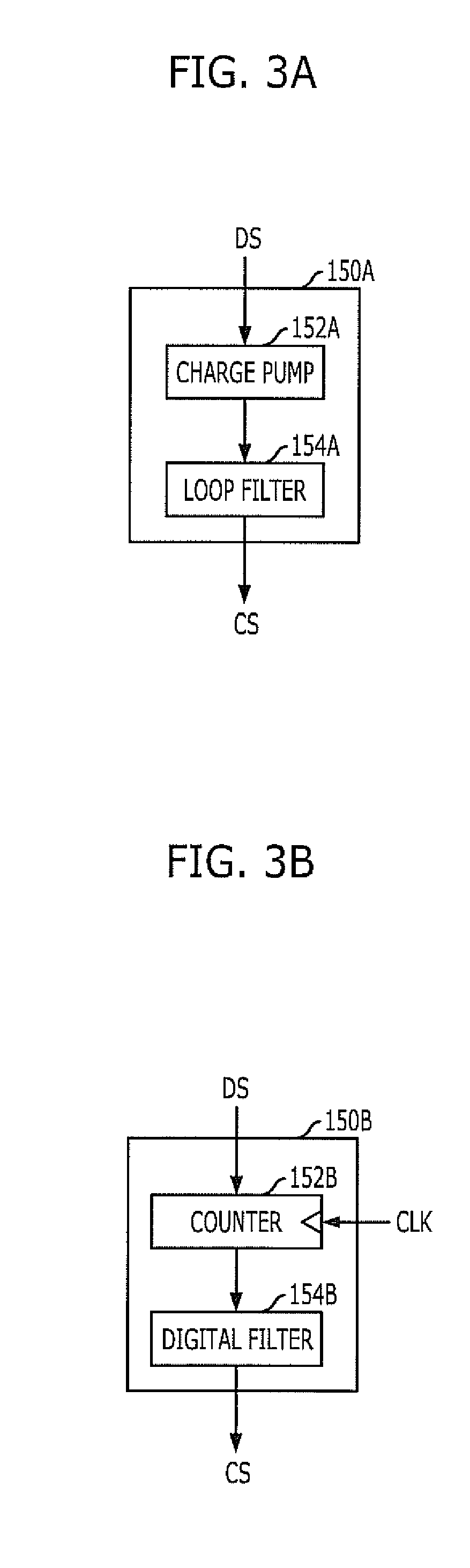

[0026]FIG. 1 is a block diagram illustrating an interface apparatus for a semiconductor integrated circuit in accordance with the present invention. FIG. 2 illustrates a phase detector shown in FIG. 1. FIGS. 3A to 3C are block diagrams describing an analog control signal generator and two digital control signal generators. FIGS. 4A and 4B illustrate a controller shown in FIG. 1 along with a first output buffer.

[0027]In the first embodiment, a one-directional interface apparatus including an output block has been selected as an example and is described as follows. Referring to FIG. 1, an interface apparatus 100 provided within a semiconductor integrated circuit (IC) includes an output block 110, which buffers a signal IN and a bar signal INB generated by an internal circuit (not shown) of the semiconductor integrated circuit and outputs the buffered signals to an external circuit (not shown) through a first pad 102 (PAD1) and a second pad 104 (PAD2). The output block 110 includes a f...

second embodiment

[0052]Hereafter, an operation of the interface apparatus in accordance with the present invention is described below, referring to FIG. 8.

[0053]FIG. 8 is a flowchart illustrating an interfacing method of the interface apparatus in accordance with the second embodiment of the present invention.

[0054]Herein, it is assumed in the description of the second embodiment that controlling VOX corresponds to controlling a time delay.

[0055]Referring to FIG. 8, in step S210, an output block 210 is enabled by an output enable signal EN. In step S202, the output block 210 begins to be driven and enters into an output stand-by state and at the same time a first switch 232 and a second switch 234 are controlled to be open. Since the first switch 232 and the second switch 234 are open, an input block 220 is switched from an input stand-by state to a feedback stand-by state.

[0056]When a signal IN and a bar signal INB output by an internal circuit of a semiconductor integrated circuit are transferred ...

third embodiment

[0062]FIG. 9 is a block diagram illustrating an interface apparatus of a semiconductor integrated circuit in accordance with the present invention. FIG. 10 is a circuit diagram illustrating an output controller shown in FIG. 9. For the sake of convenience in description, only a line for a signal IN is illustrated in FIG. 10.

[0063]The third embodiment of the present invention is designed to control a slew of a signal and a bar signal generated by an internal circuit of a semiconductor integrated circuit. The interface apparatus in accordance with the third embodiment of the present invention may be applied to both a one-directional interface apparatus and a bi-directional interface apparatus. The same reference numerals are given to the same constituent elements as those shown in the first embodiment and a description on the same constituent elements has been omitted herein.

[0064]Referring to FIGS. 9 and 10, the interface apparatus 100′ includes a timing control and output block 110′...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com