Low input bias current chopping switch circuit and method

a chopping switch and low input bias current technology, applied in the direction of pulse automatic control, dc isolation amplifier, pulse technique, etc., can solve the problem of not much design flexibility for adjusting these two variables in order to meet certain design requirements, and the prior art chopper stabilization circuitry is associated with an increased input bias current and other problems, to achieve the effect of low output ripple noise and low input bias curren

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

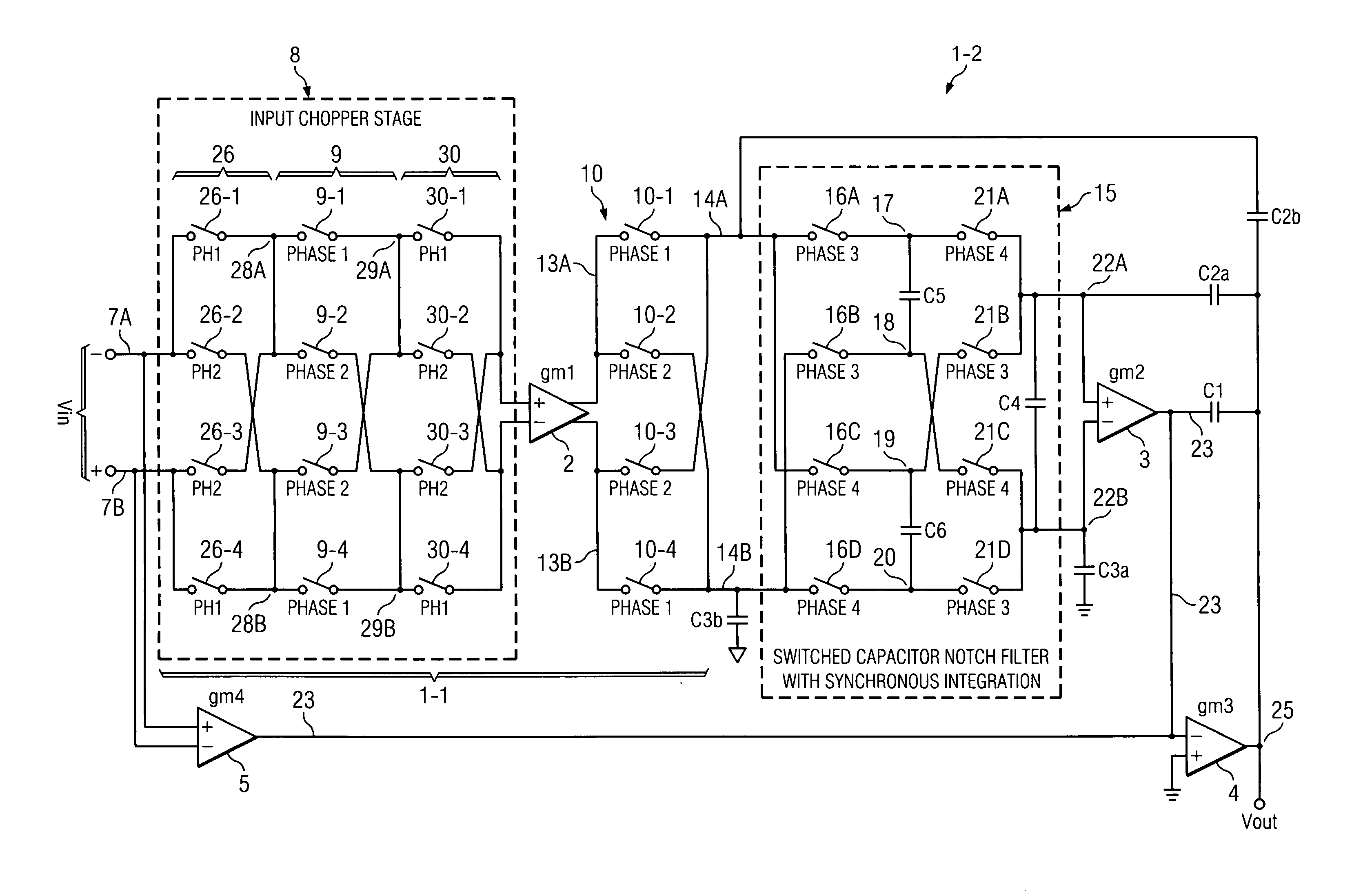

[0030]Referring to FIG. 3A, operational amplifier 1-1 includes (−) input conductor 7A and (+) input conductor 7B by means of which an input signal Vin is applied to input chopping stage 8, which includes a low-frequency pre-chopping circuit 26, a high-frequency chopping circuit 9, and a low-frequency post-chopping circuit 30. Pre-chopping circuit 26 includes switches 26-1 and 26-2 having first terminals connected to (−) input conductor 7A and switches 26-3 and 26-4 having first terminals connected to (+) input conductor 7B. Switches 26-1 and 26-3 have second terminals connected by conductor 28A to one input of input chopping circuit 9, and switches 9-2 and 9-4 have second terminals connected by conductor 28B to another input of input chopping circuit 9. Input chopping circuit 9 includes switches 9-1 and 9-2 having first terminals connected to conductor 28A and switches 9-3 and 9-4 having first terminals connected to conductor 28B. Switches 9-1 and 9-3 have second terminals connected...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More