High density interconnect module

a high-density, interconnect module technology, applied in the direction of basic electric elements, electrical apparatus construction details, solid-state devices, etc., can solve the problems of increasing the cost of circuits, limited space along one-dimensional edges of integrated circuit chips, and increasing the size of the system

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

While the present invention is described herein with reference to illustrative embodiments for particular applications, it should be understood that the invention is not limited thereto. Those having ordinary skill in the art and access to the teachings provided herein will recognize additional modifications, applications, and embodiments within the scope thereof and additional fields in which the present invention would be of significant utility.

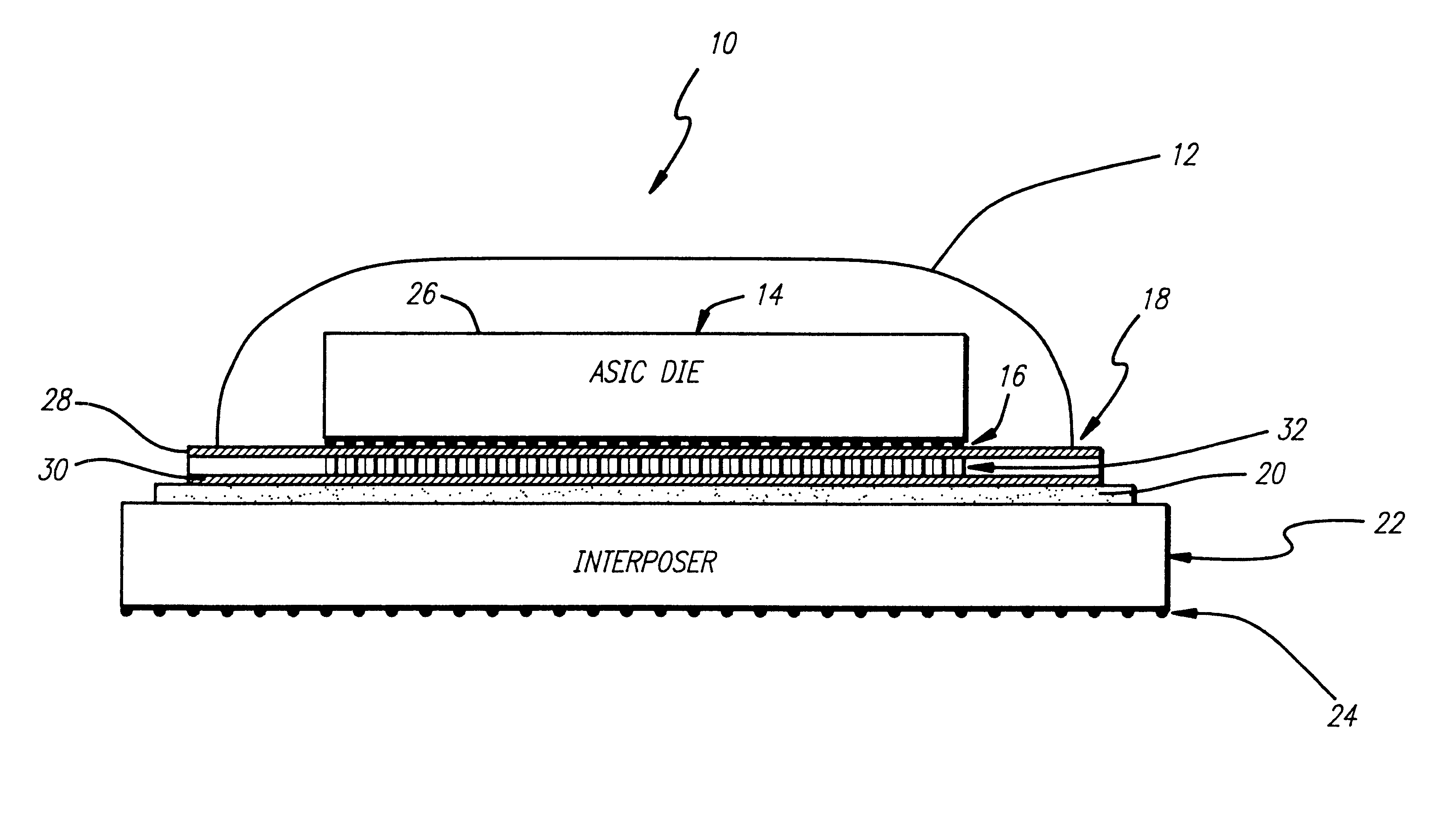

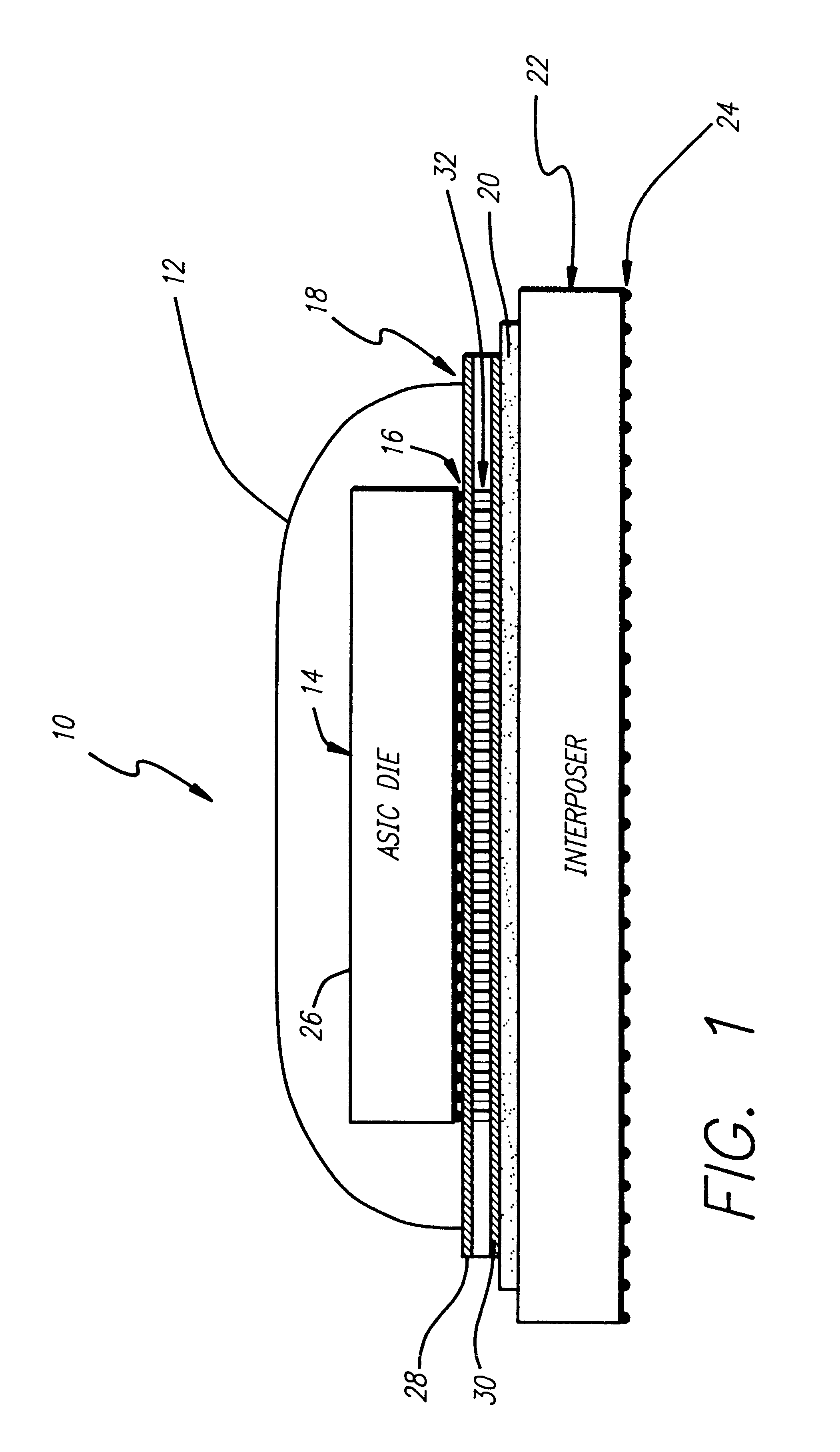

FIG. 1 is a diagram of a packaging system 10 constructed in accordance with the teachings of the present invention. The packaging system 10 includes, from top to bottom, an encapsulant sealer 12, an application specific integrated circuit (ASIC) die or chip 14, a first array of input / output contacts 16, a double-sided DECAL 18, a z-axis adhesive 20, an interposer 22, and a second array of input / output contacts 24.

The encapsulant sealer 12 is a non-non-hermetic and is made of plastic in the present specific embodiment. The ASIC die 14 is an ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More