Nonvolatile semiconductor memory device and method for operating the same

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

first embodiment

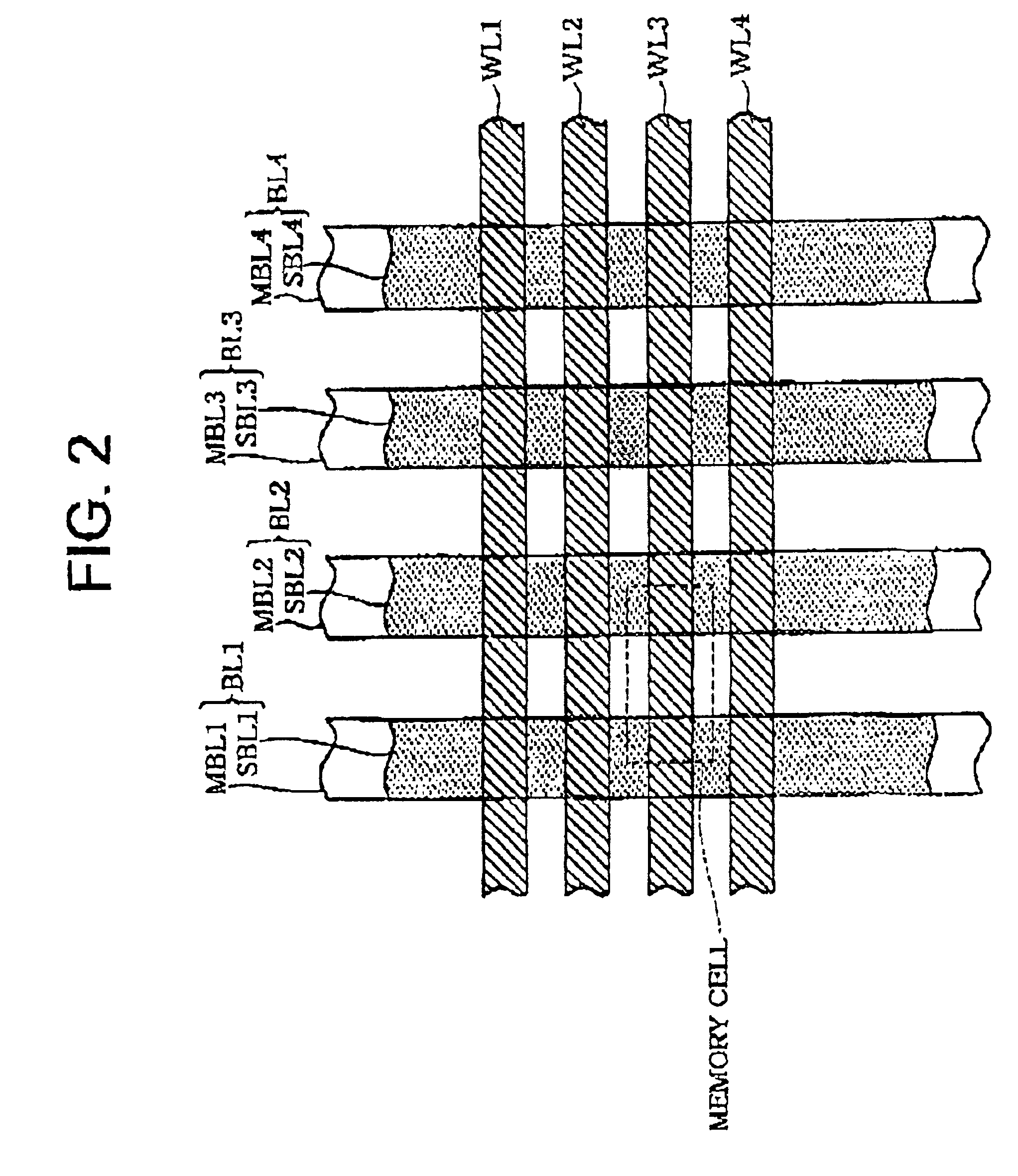

[0072]The first embodiment relates to a virtual grounding NOR type nonvolatile semiconductor memory device.

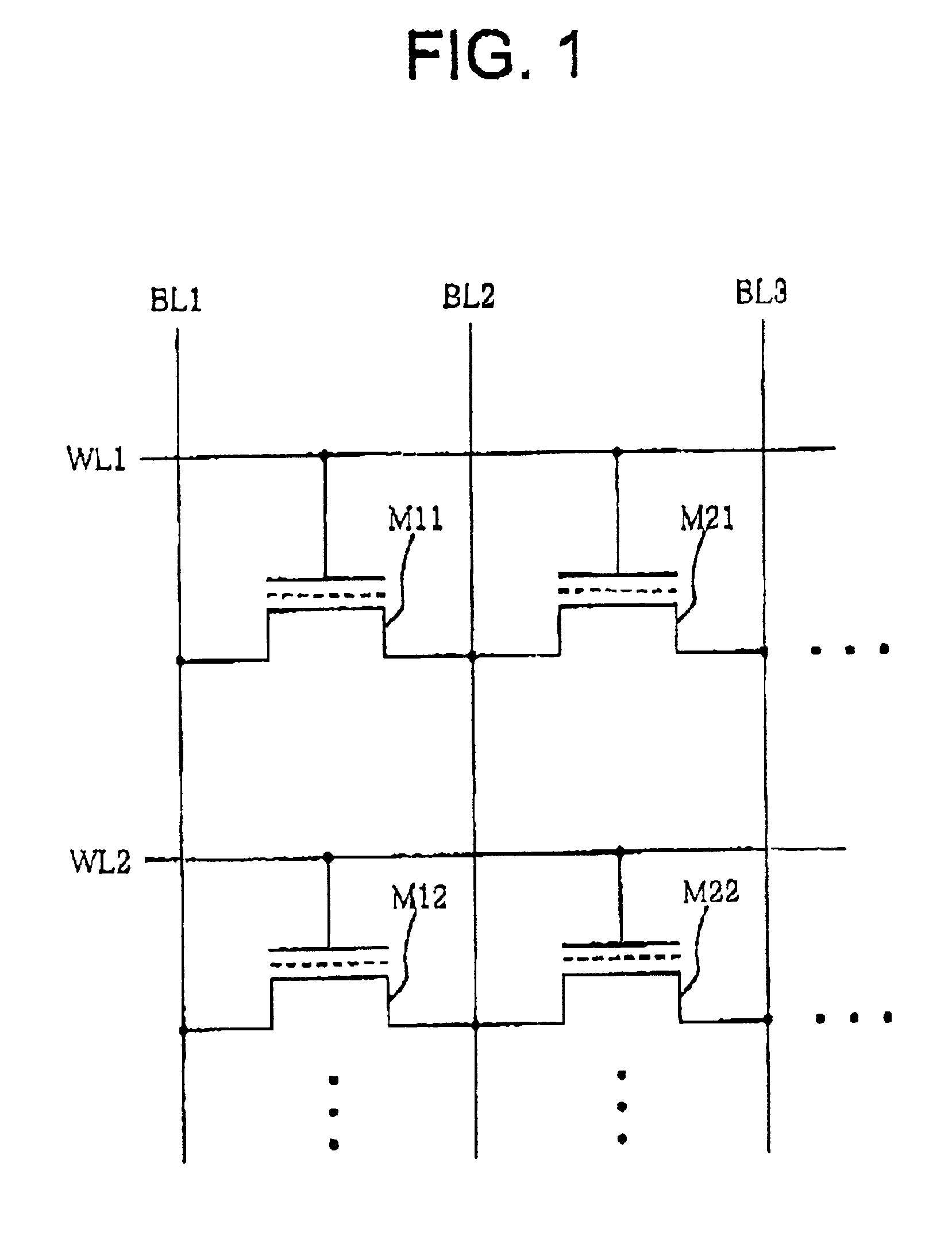

[0073]FIG. 1 is a circuit diagram of the configuration of a virtual grounding NOR type memory cell array.

[0074]In this memory cell array, each memory cell is comprised of a single memory transistor. For example, m×n memory transistors M11, M21, . . . , Mm1, M12, M22, . . . , M1n, . . . , Mmn are arranged like a matrix. Shown in FIG. 1 are only 2×2 memory transistors.

[0075]Each gate of memory transistors in one row is connected to the same word line. That is, in FIG. 1, gates of memory transistors belonging to the same row M11, M21, . . . , are connected to the word line WL1. While, gates of memory transistors belonging to the other row M12, M22, . . . , are connected to the word line WL2.

[0076]Each source of memory transistors is connected to the drain of a memory transistor adjacent at one side in the word direction. The drain of a memory transistor is connected to the source ...

second embodiment

[0131]The second embodiment relates to a modification of the configuration of the gate insulating film of a memory transistor in a virtual grounding NOR type nonvolatile semiconductor memory device. Tho circuit diagram in FIG. 1 and the plain view in FIG. 2 are also applicable to the second embodiment.

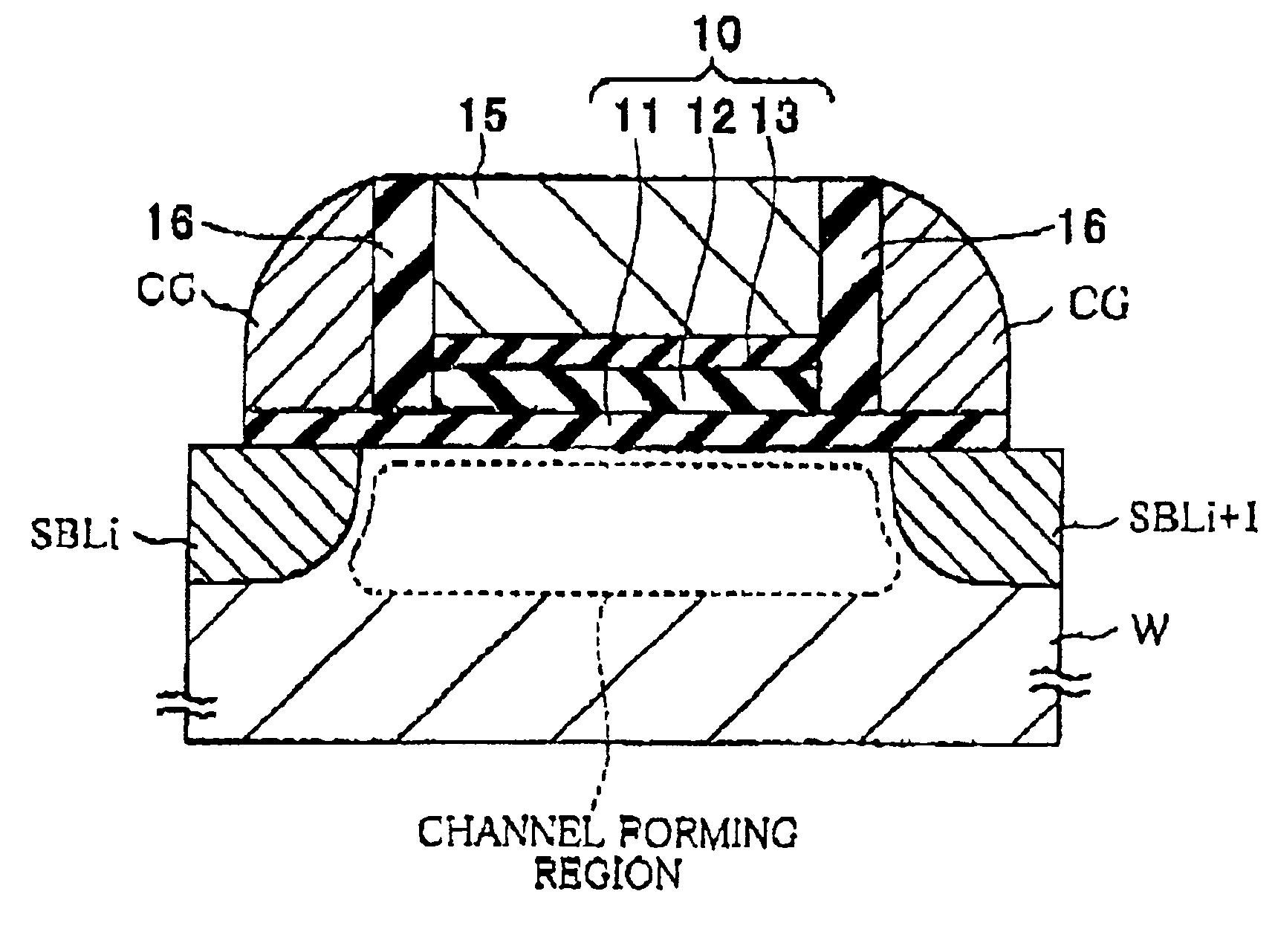

[0132]FIG. 10 is a cross-sectional view for illustrating the configuration of a memory transistor related to the second embodiment.

[0133]In this memory transistor, the gate insulating film consists of a gate insulating film 10a at the side of the sub-bit line SBLi and a gate insulating film 10b at the side of the sub-bit line SBLi+1. The two gate insulating films 10a and 10b are spatially separated by a single layer gate insulating film 14 above the central portion of the channel.

[0134]The gate insulating films 10a and 10b have the same structure as gate insulating film 10 in the first embodiment. That is, the gate insulating film 10a consists of a bottom insulating film 11a (FN tunnel...

third embodiment

[0149]The third embodiment relates to an application of the technique of FN tunneling low barrier to a transistor of a configuration comprising a second gate electrode, so-called control gate, at the source and / or drain side.

[0150]FIG. 11 and FIG. 12 are circuit diagrams of examples of configurations of memory cell arrays according to the third embodiment.

[0151]These memory transistor arrays are basically virtual grounding NOR type memory cell arrays the same as that in the fifth embodiment. But, in the present memory cell arrays, however, in each memory transistor, the control gates are provided to extend from the source and drain impurity region side to partly overlap with the channel forming region.

[0152]Further, the arrays are provided with a control line CL1a commonly connecting the control gates at one side of the memory transistors M11, M12, . . . connected in the bit line direction, a control line CL1b commonly connecting the control gates at the other side, a control line C...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More