Data processor and data processing system and method for accessing a dynamic type memory using an address multiplexing system

a data processor and data processing system technology, applied in the field of data processing technology, can solve the problems of large packaging area of the system, more troublesome control of the system than that of the rom, and inability to design the system, and achieve the effect of high versatility

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

embodiment 1

[Embodiment 1]

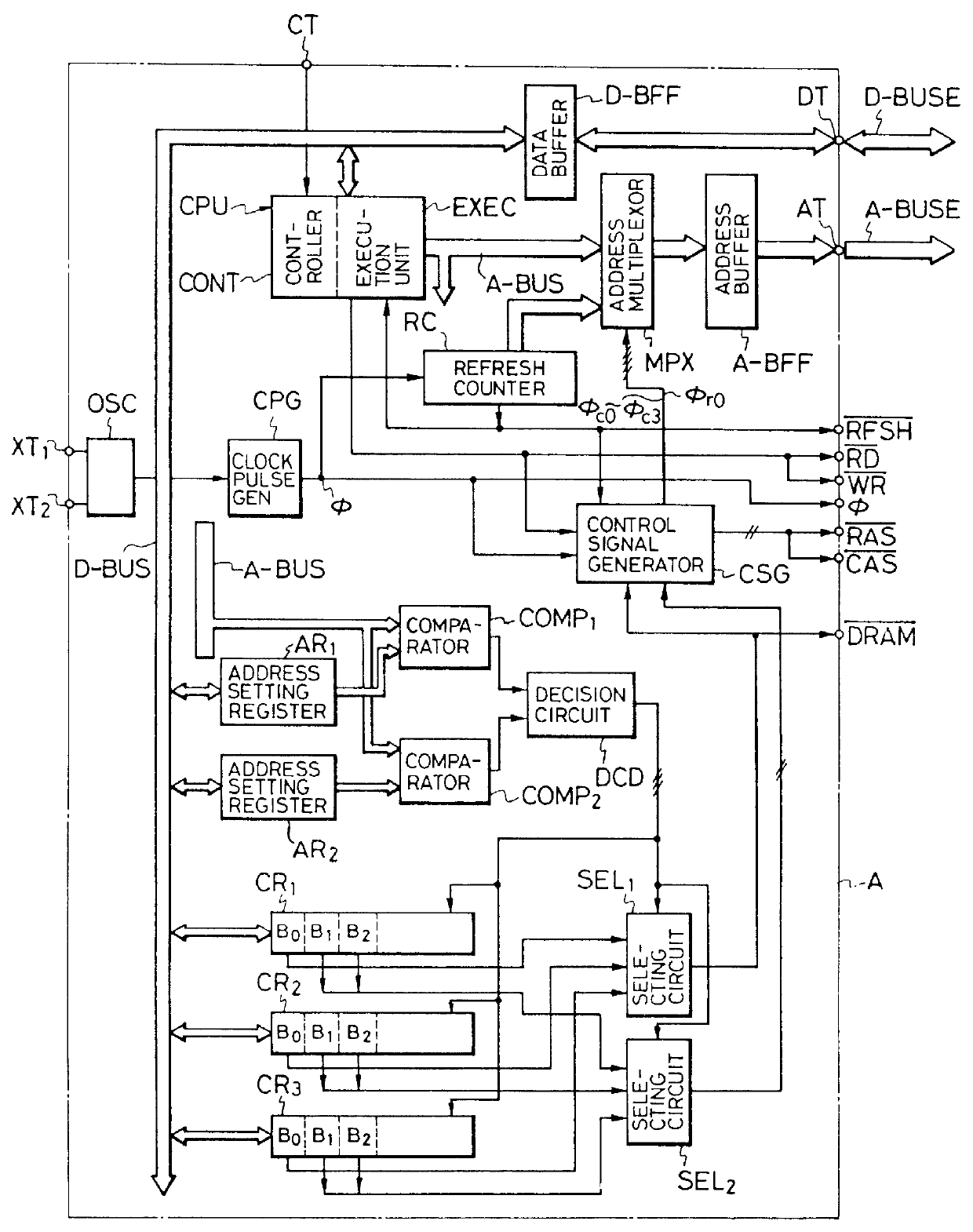

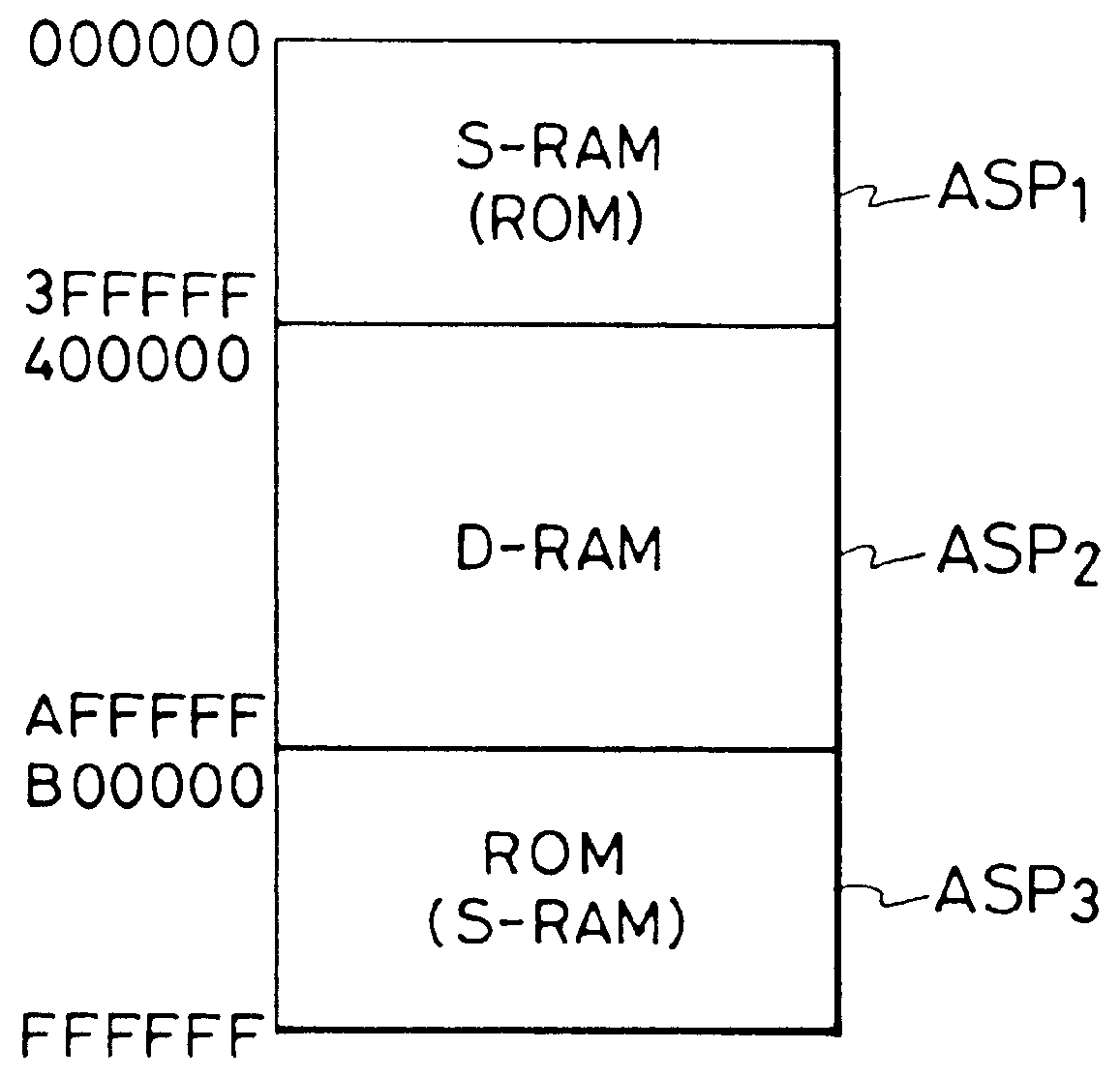

FIG. 1 is a circuit block diagram of one embodiment in the case of applying the present invention to a 16-bit microprocessor. In the figure, a portion enclosed with a chain line A is formed on a single semiconductor substrate such as single-crystal silicon by known semiconductor production technology.

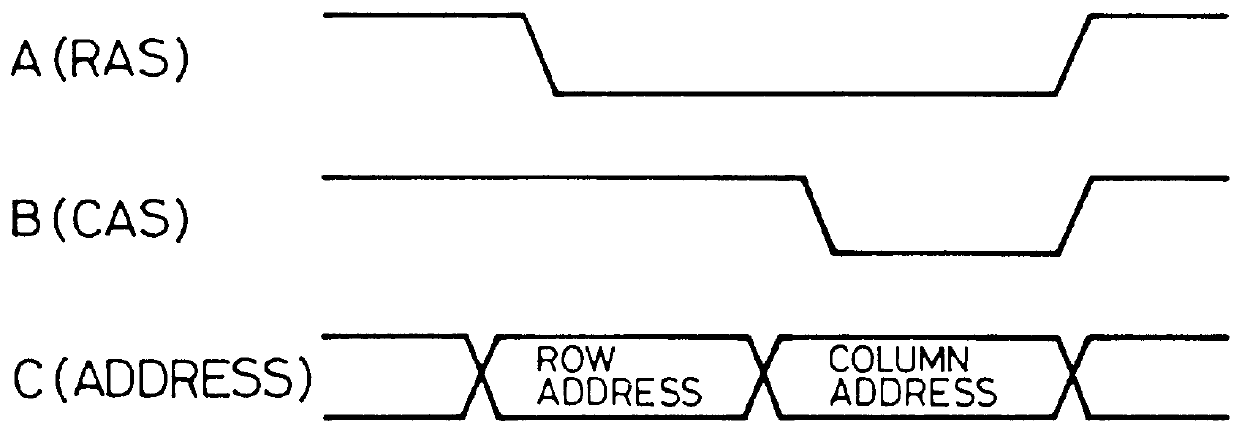

In FIG. 1, shown by circuit symbol CPU is a microprocessor portion. Although this microprocessor portion CPU, the practicable arrangement of which is not directly pertinent to the present invention, is not illustrated in detail, it is constructed of for example execution unit EXEC which is composed of an arithmetic-logic unit, dedicated registers such as a program counter, a stack pointer, a status register, and general-purpose registers for use as work areas, and a controller CONT which is composed of an instruction register to which microprogram instructions read out from an external memory not shown are successively input. micro ROMs in which microinstructions correspon...

embodiment 2

[Embodiment 2]

FIG. 13 is a circuit diagram of an address multiplexor MPX and a part of a control signal generator CSG in another embodiment.

In this embodiment, timing signals .phi..sub.r0, .phi..sub.c0 and .phi..sub.ref in the control signal generator CSG are respectively the same as those of the preceding embodiment.

In the control signal generator CSG, an inverter circuit IV.sub.45 and an AND gate circuit G.sub.1 constitute a decoder which forms an output signal of high level when bit signals B.sub.1 and B.sub.2 are "1" and "0" respectively, namely, when the bit signals B.sub.1 and B.sub.2 indicates a memory such as 64-kilobit memory of 1-bit format.

A timing signal .phi..sub.r1 to be output from an OR gate circuit G.sub.2 is brought to the high level in synchronism with the timing signal .phi..sub.r0 if the bit signals B.sub.1 and B.sub.2 indicate the 64-kilobit memory, and it is maintained at the high level irrespective of the timing signal .phi..sub.r0 unless the bit signals B.su...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More