Methods and apparatus for abbreviated instruction sets adaptable to configurable processor architecture

a processor architecture and instruction set technology, applied in the field of methods and apparatus for abbreviated instruction sets adaptable to configurable processor architecture, can solve the problems of reducing the capability of instruction reduction, reducing the number of instructions required in standard designs for high-performance execution units, and reducing the number of instructions. achieve the effect of increasing the code density and extending the capability of plugging instruction sets

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

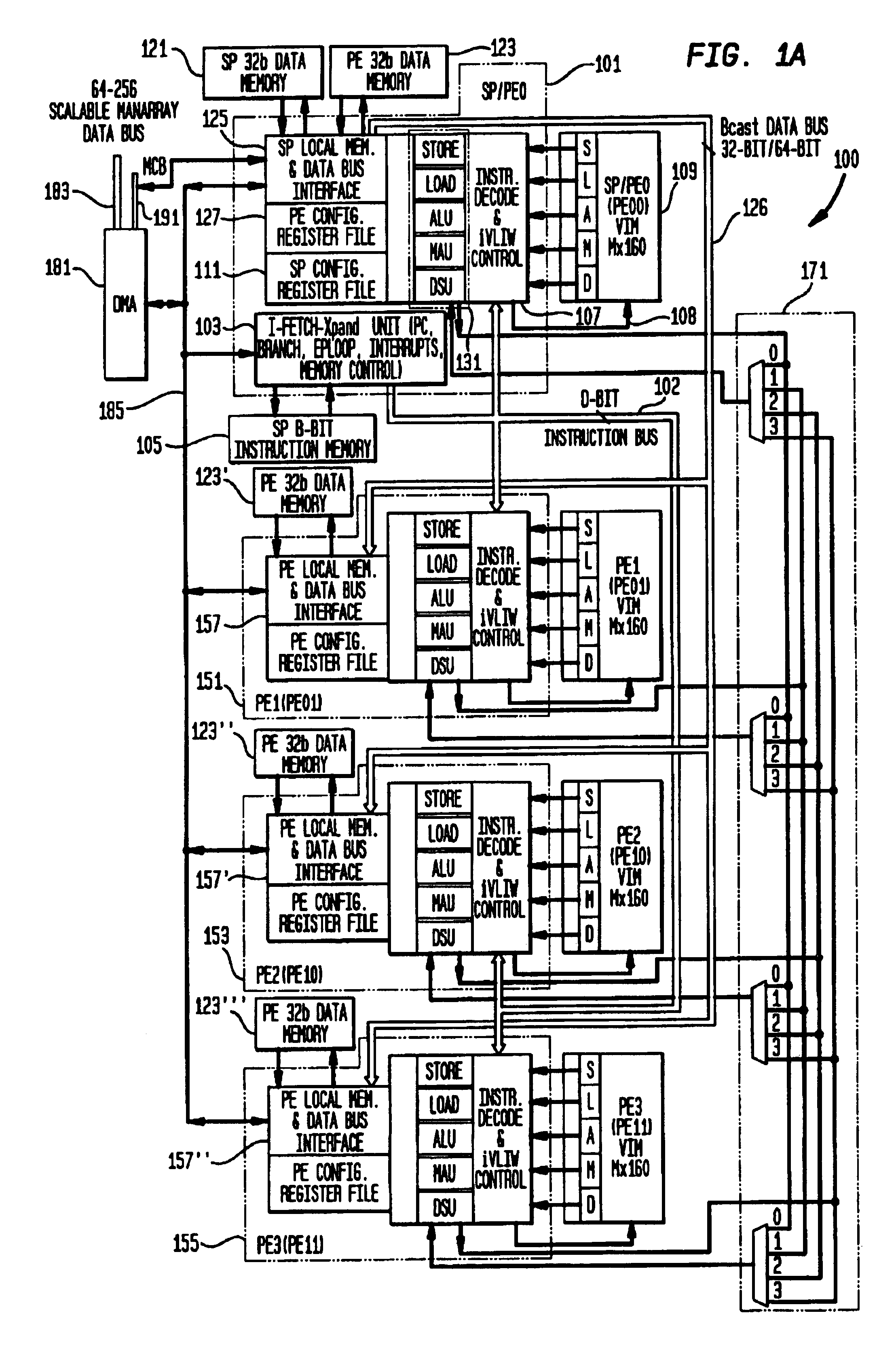

[0035]Further details of a presently preferred ManArray architecture for use in conjunction with the present invention are found in U.S. Pat. No. 6,023,753, U.S. Pat. No. 6,167,502, U.S. patent application Ser. No. 09 / 169,255 filed Oct. 9, 1998, U.S. Pat. No. 6,167,501, U.S. Pat. No. 6,219,776, U.S. Pat. No. 6,151,668, U.S. Pat. No. 6,173,389, U.S. Pat. No. 6,101,592, U.S. Pat. No. 6,216,223, U.S. patent application Ser. No. 09 / 238,446 filed Jan. 28, 1999, U.S. patent application Ser. No. 09 / 267,570 filed Mar. 12, 1999, as well as, Provisional Application Serial No. 60 / 092,130 entitled “Methods and Apparatus for Instruction Addressing in Indirect VLIW Processors” filed Jul. 9, 1998, Provisional Application Serial No. 60 / 103,712 entitled “Efficient Complex Multiplication and Fast Fourier Transform (FFT) Implementation on the ManArray” filed Oct. 9, 1998, Provisional Application Serial No. 60 / 106,867 entitled “Methods and Apparatus for Improved Motion Estimation for Video Encoding” fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More