Patents

Literature

52 results about "Endianness" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

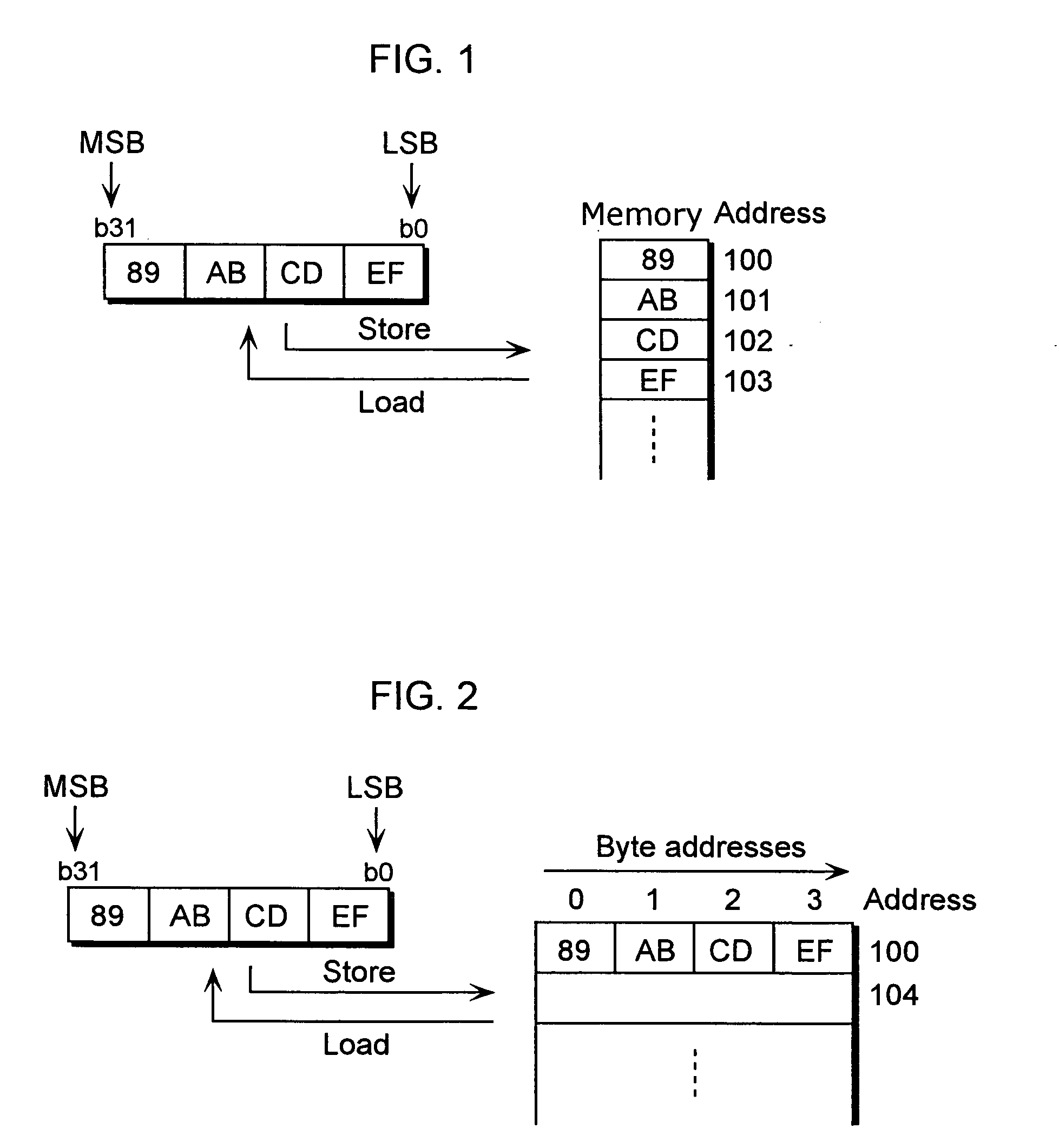

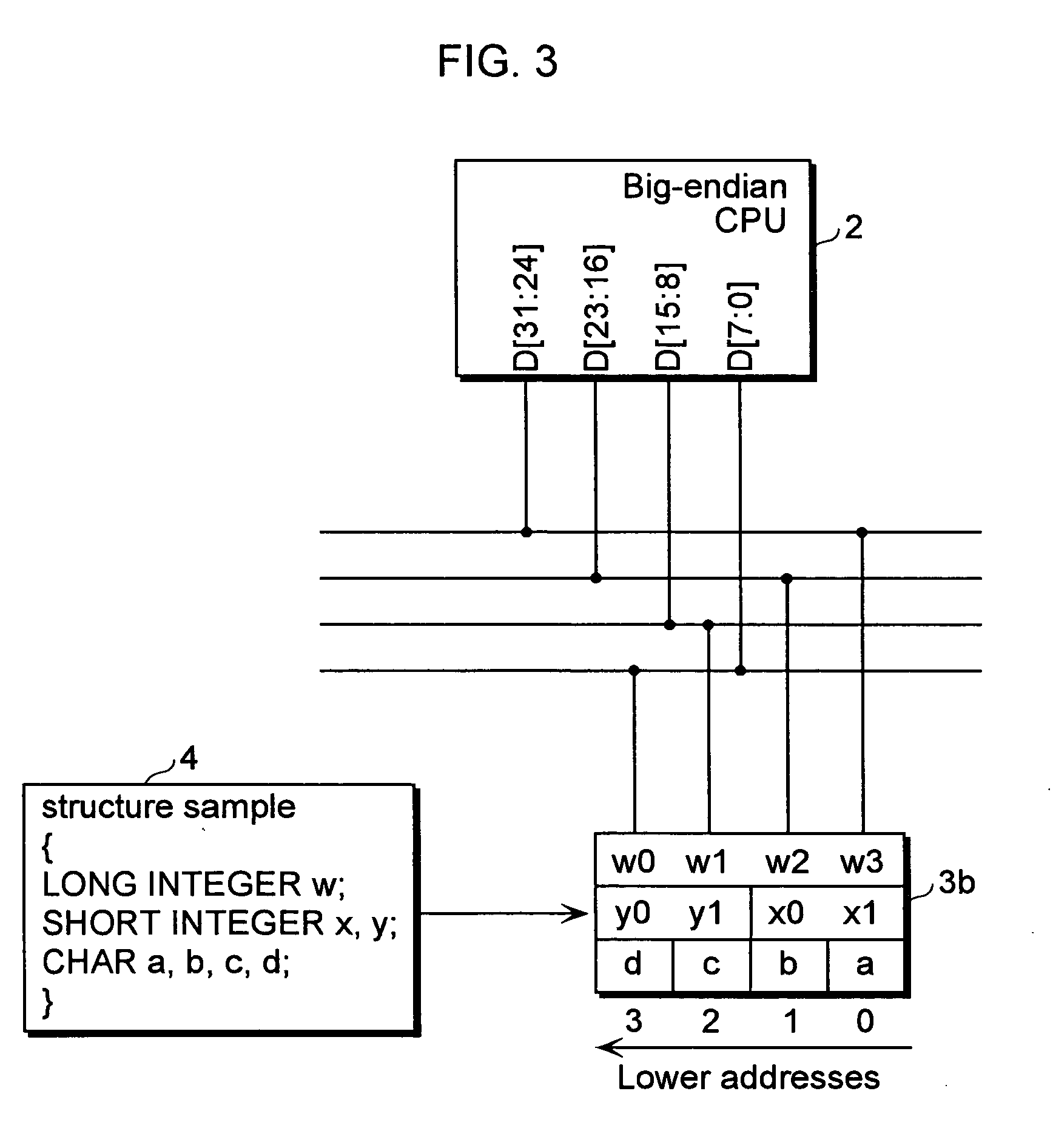

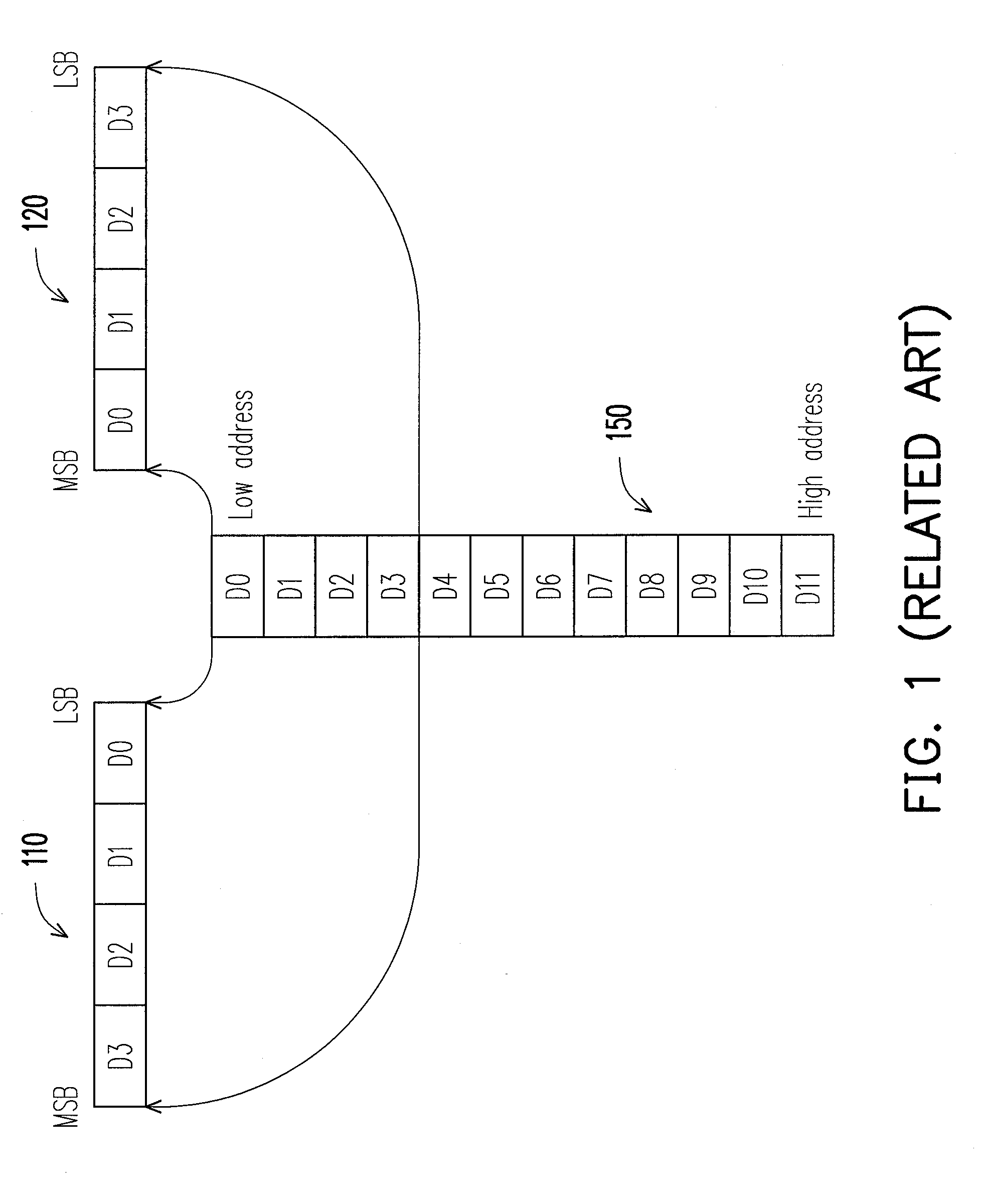

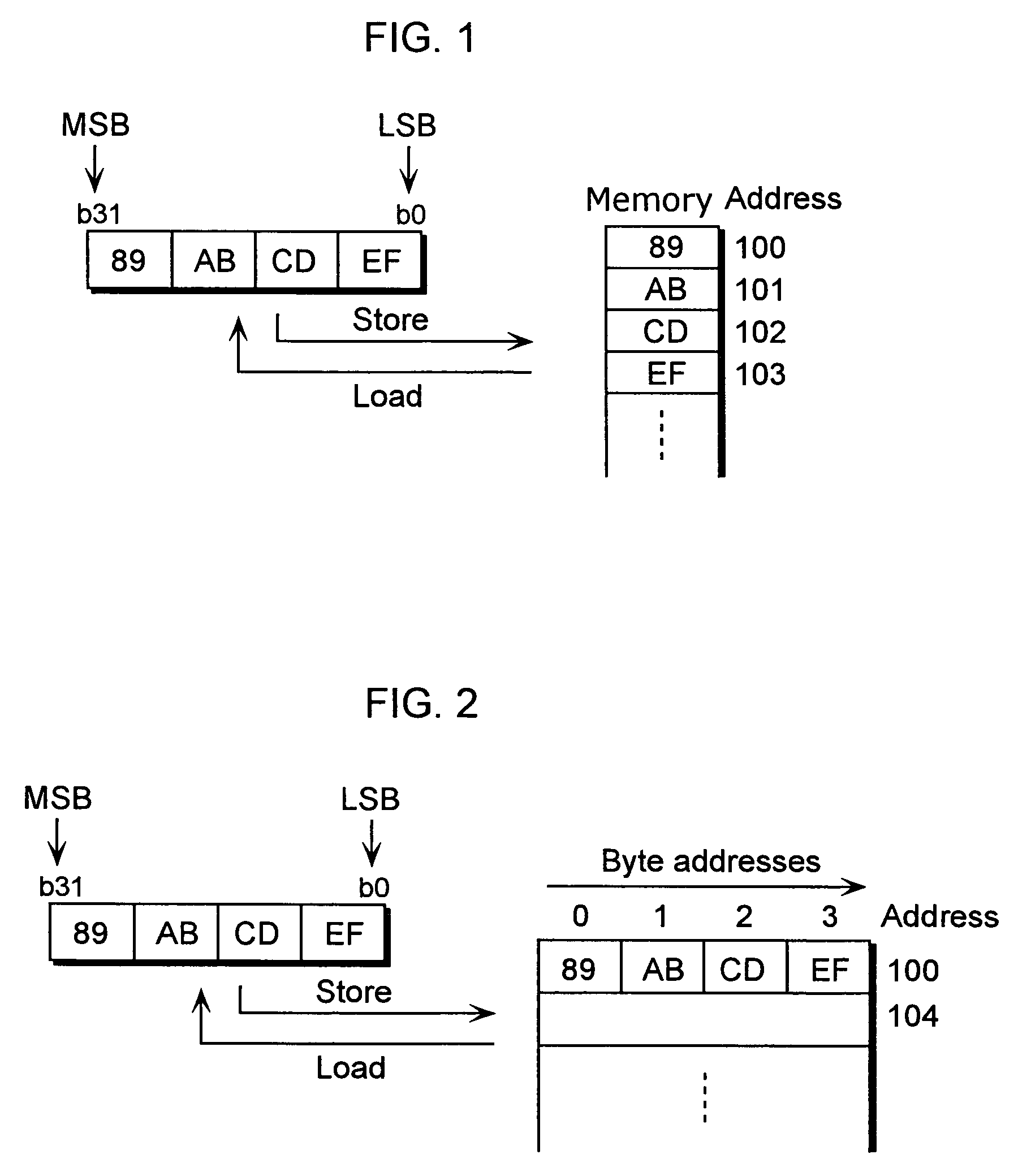

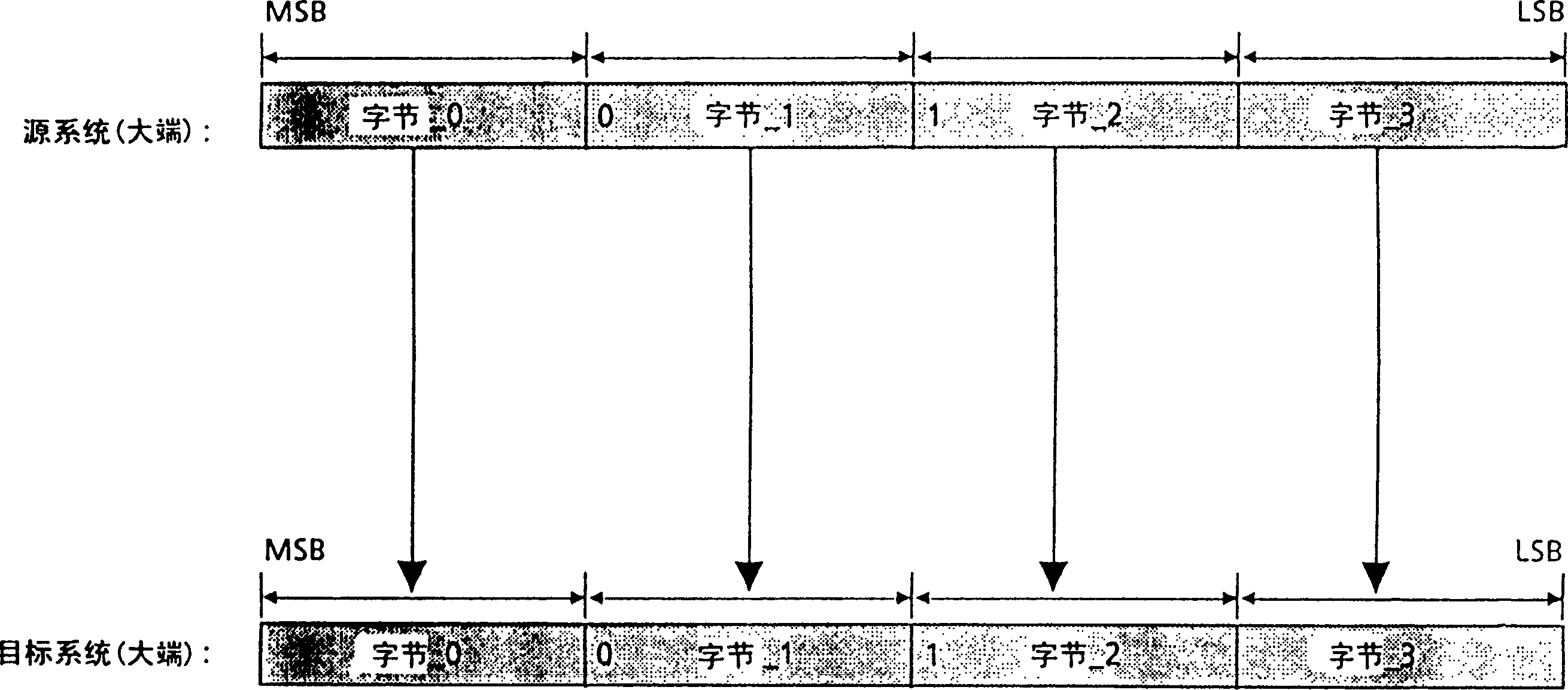

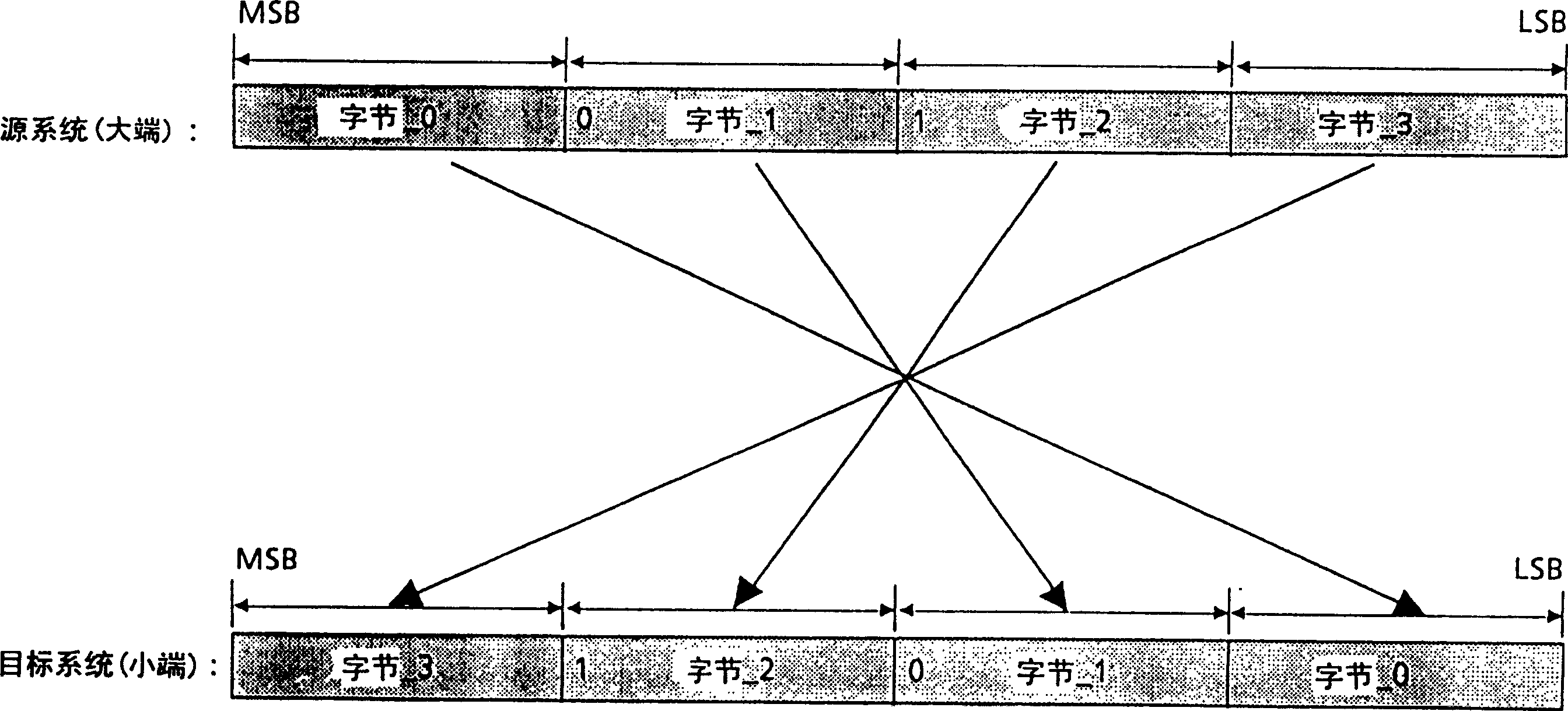

In computing, endianness refers to the order of bytes (or sometimes bits) within a binary representation of a number. It can also be used more generally to refer to the internal ordering of any representation, such as the digits in a numeral system or the sections of a date.

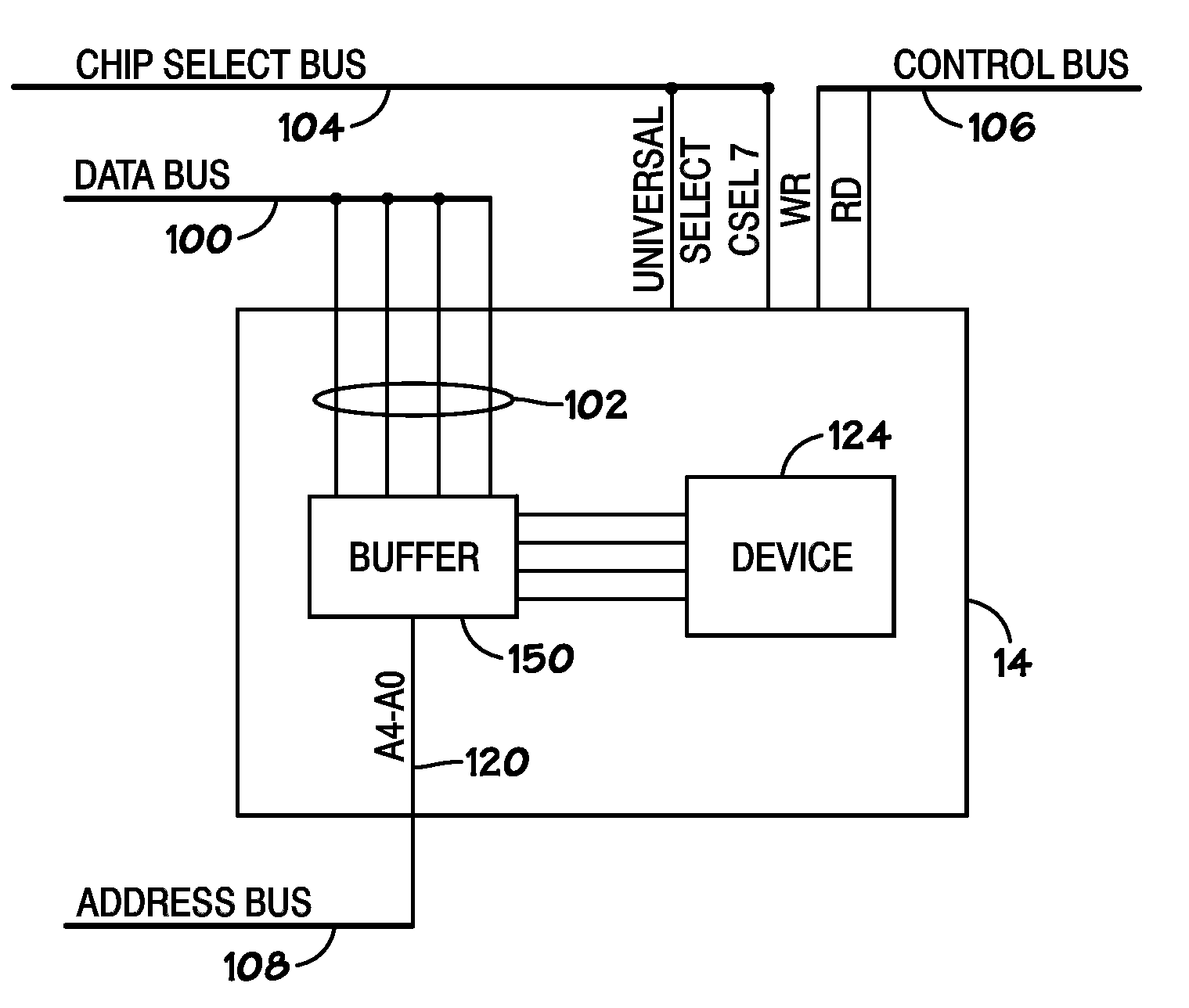

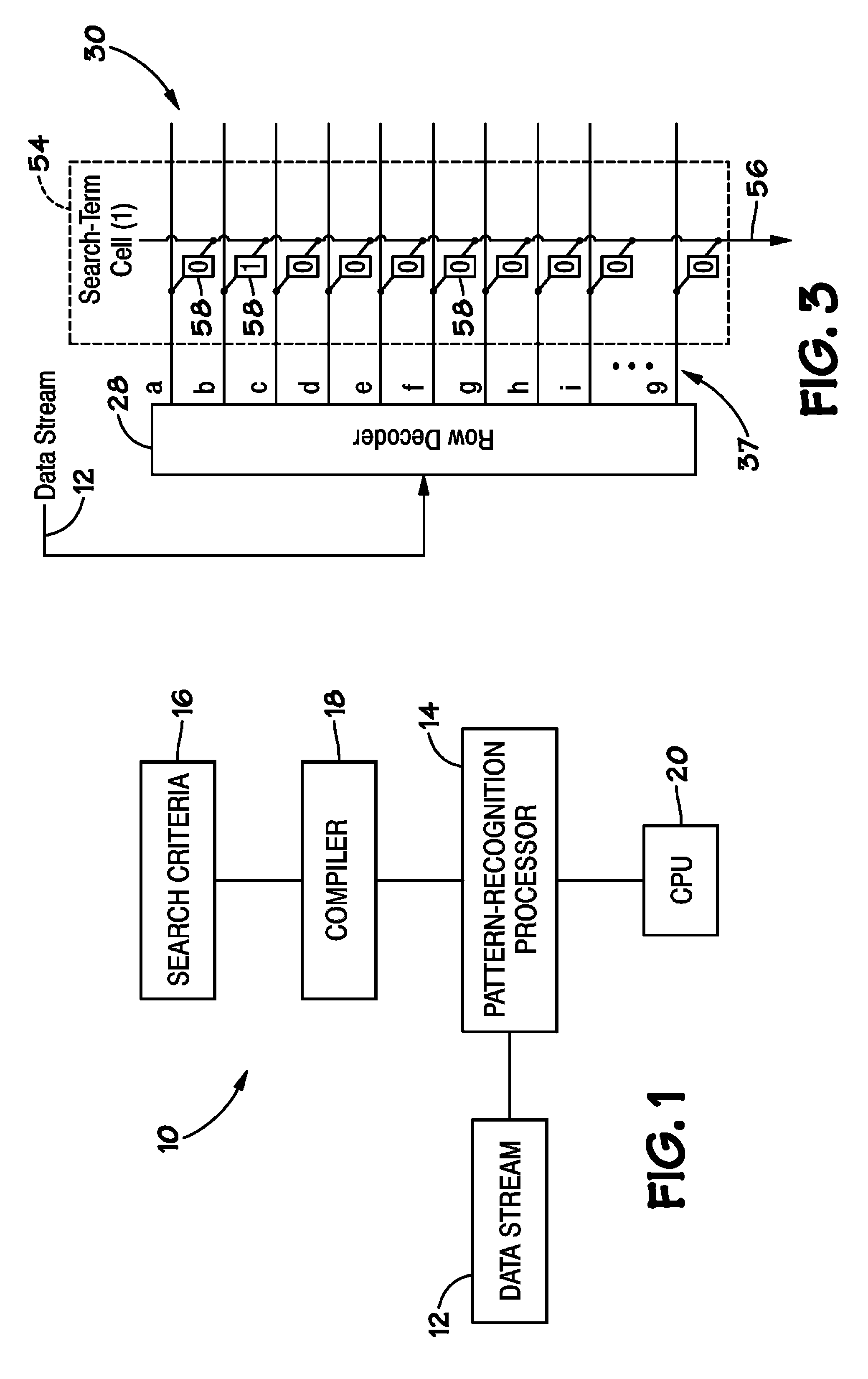

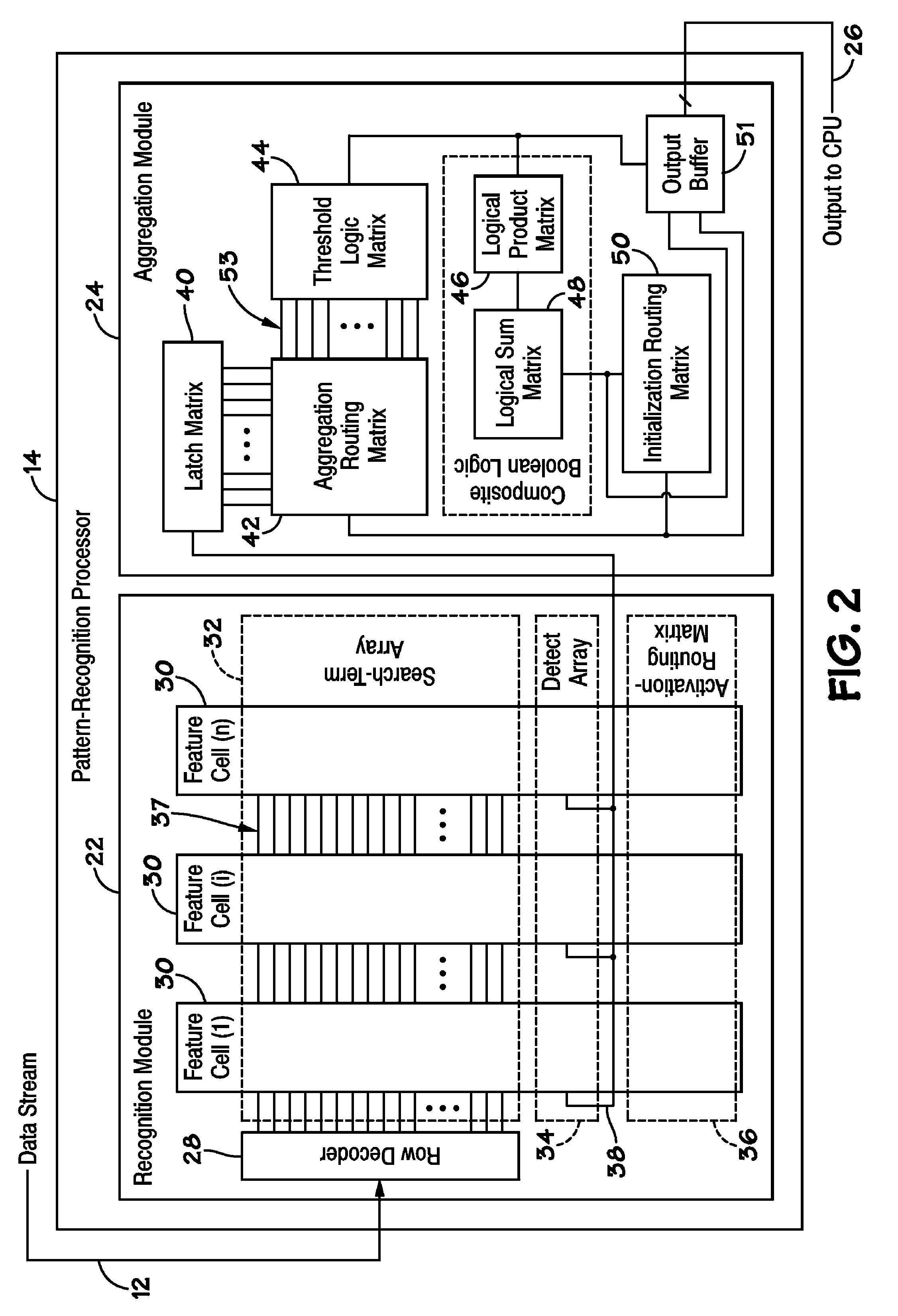

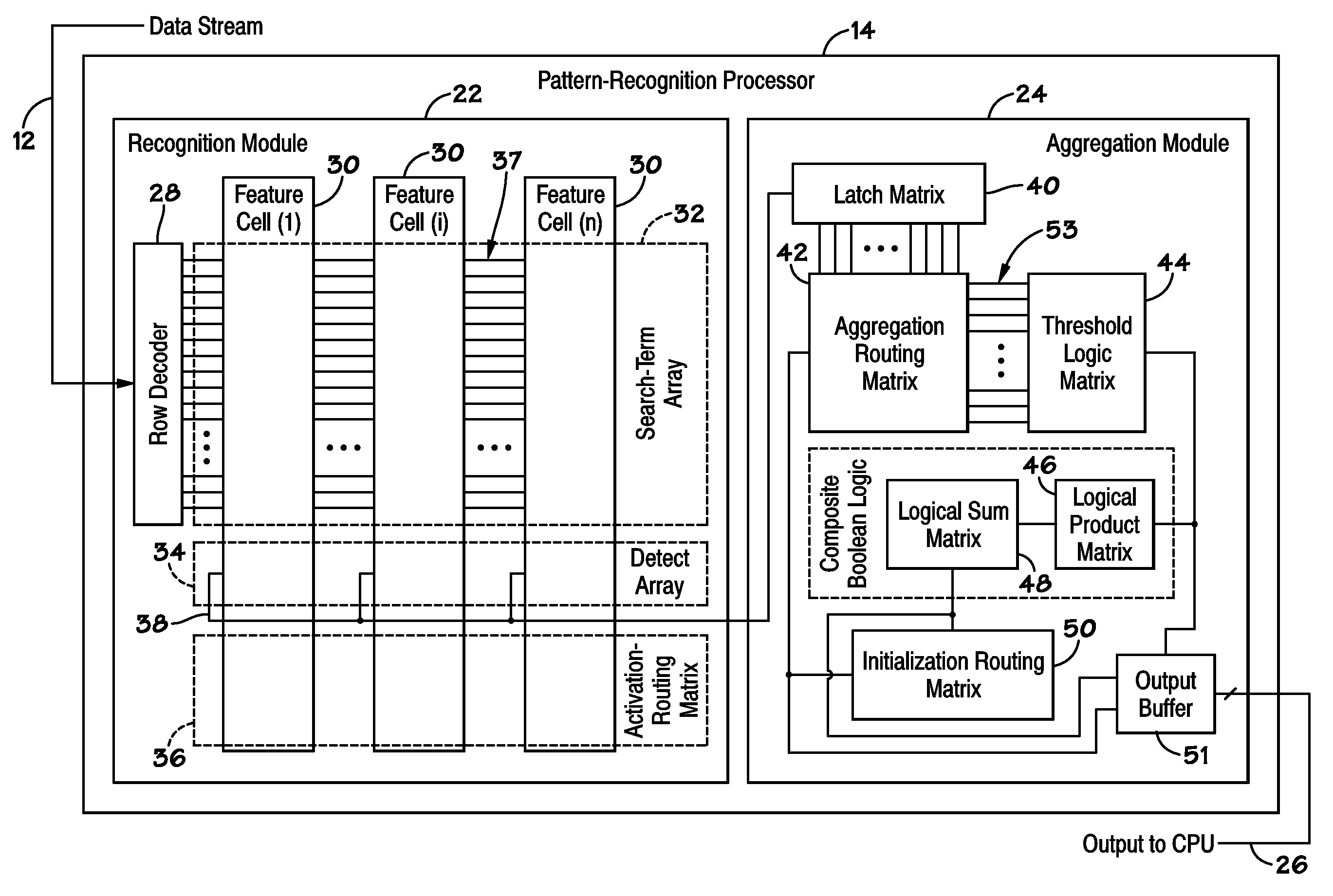

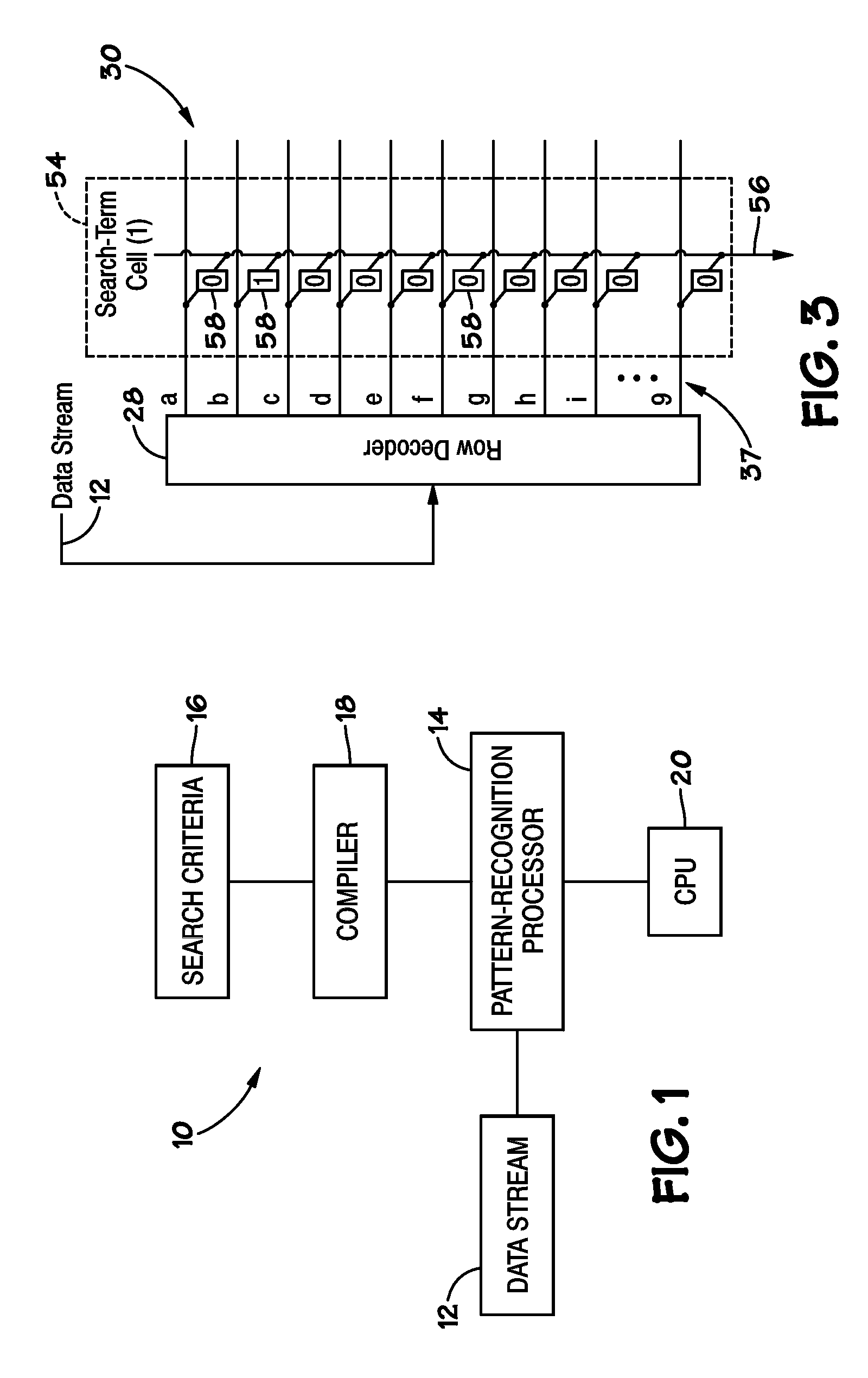

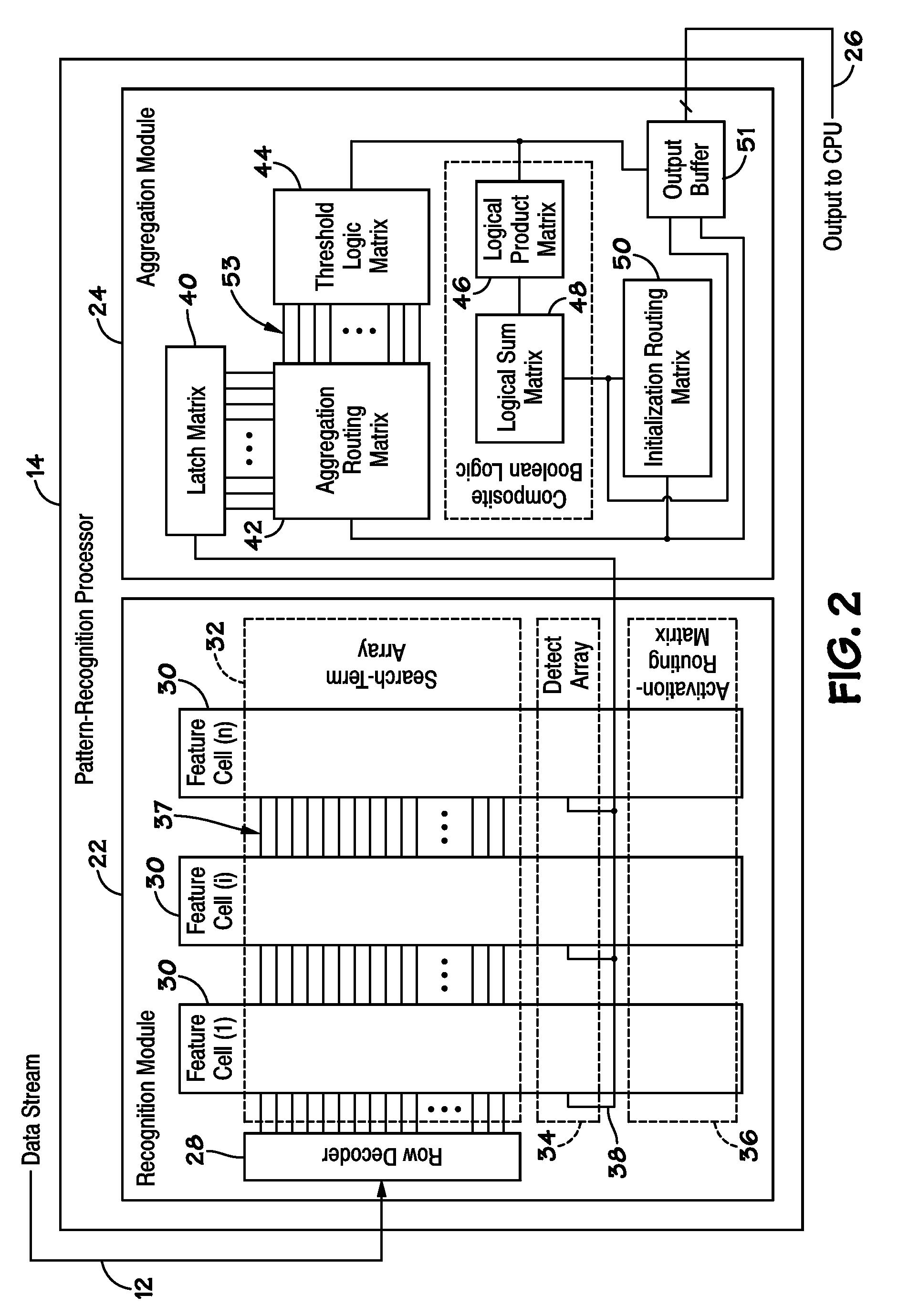

Methods and systems to accomplish variable width data input

Disclosed are methods and systems for variable width data input to a pattern-recognition processor. A variable width data input method may include receiving bytes over a data bus having a first width and receiving one or more signals indicating the validity of each of the one or more bytes The valid bytes may be sequentially provided to a pattern-recognition processor in an 8-bit wide data stream. In an embodiment, a system may include one or more address lines configured to provide the one or more signals indicating the validity of the bytes transferred over the data bus. The system may include a buffer and control logic to sequentially process the valid bytes.

Owner:MICRON TECH INC

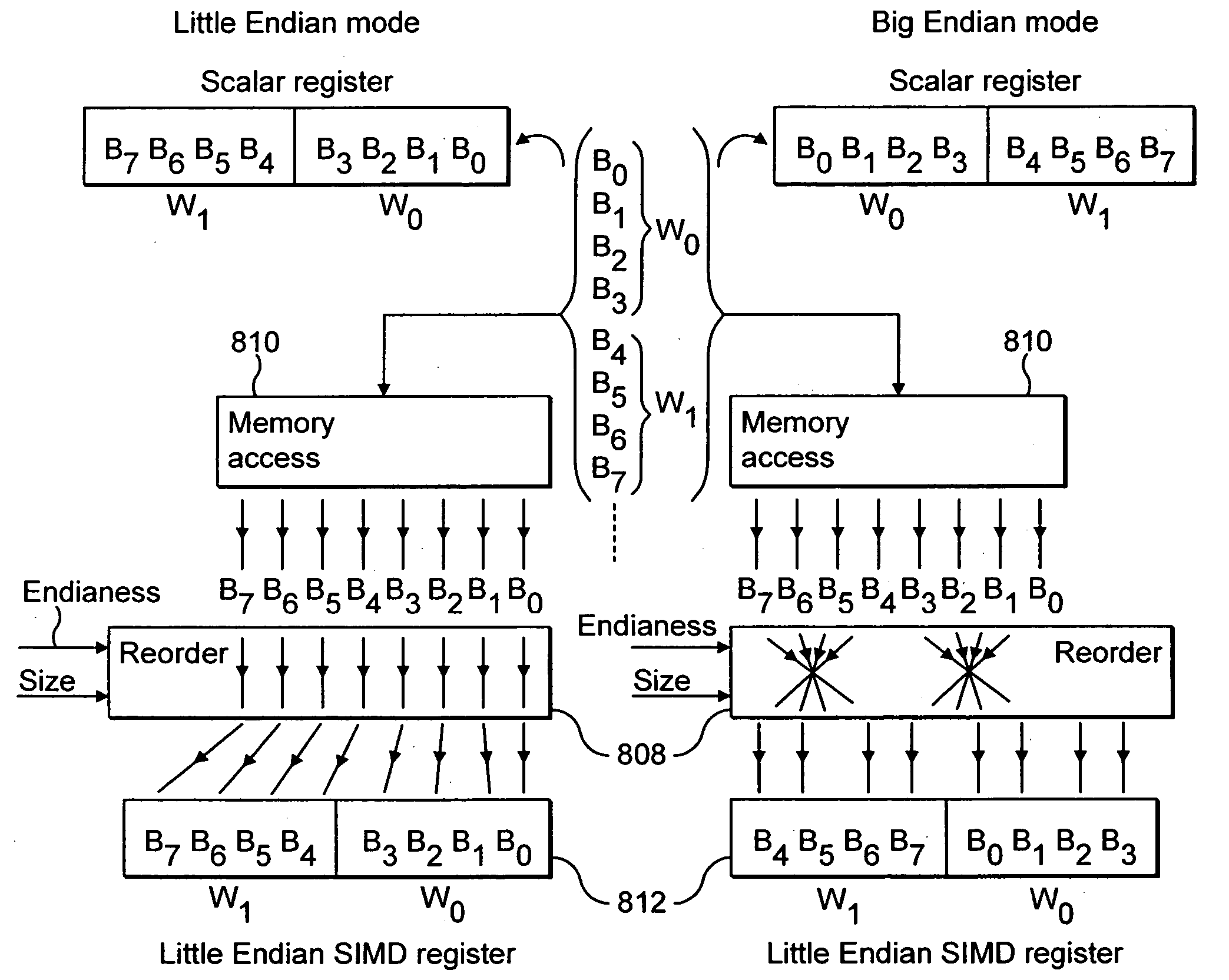

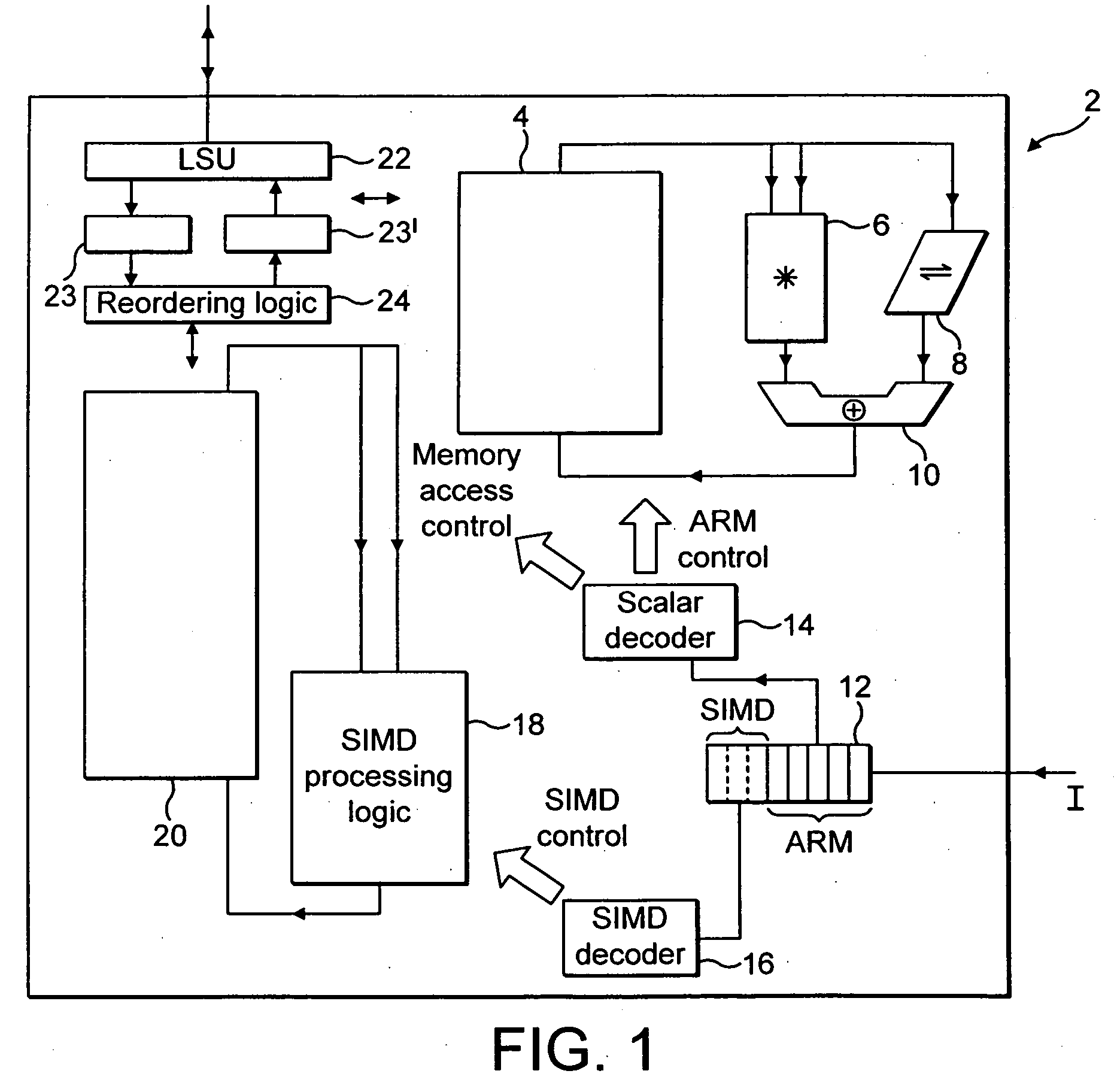

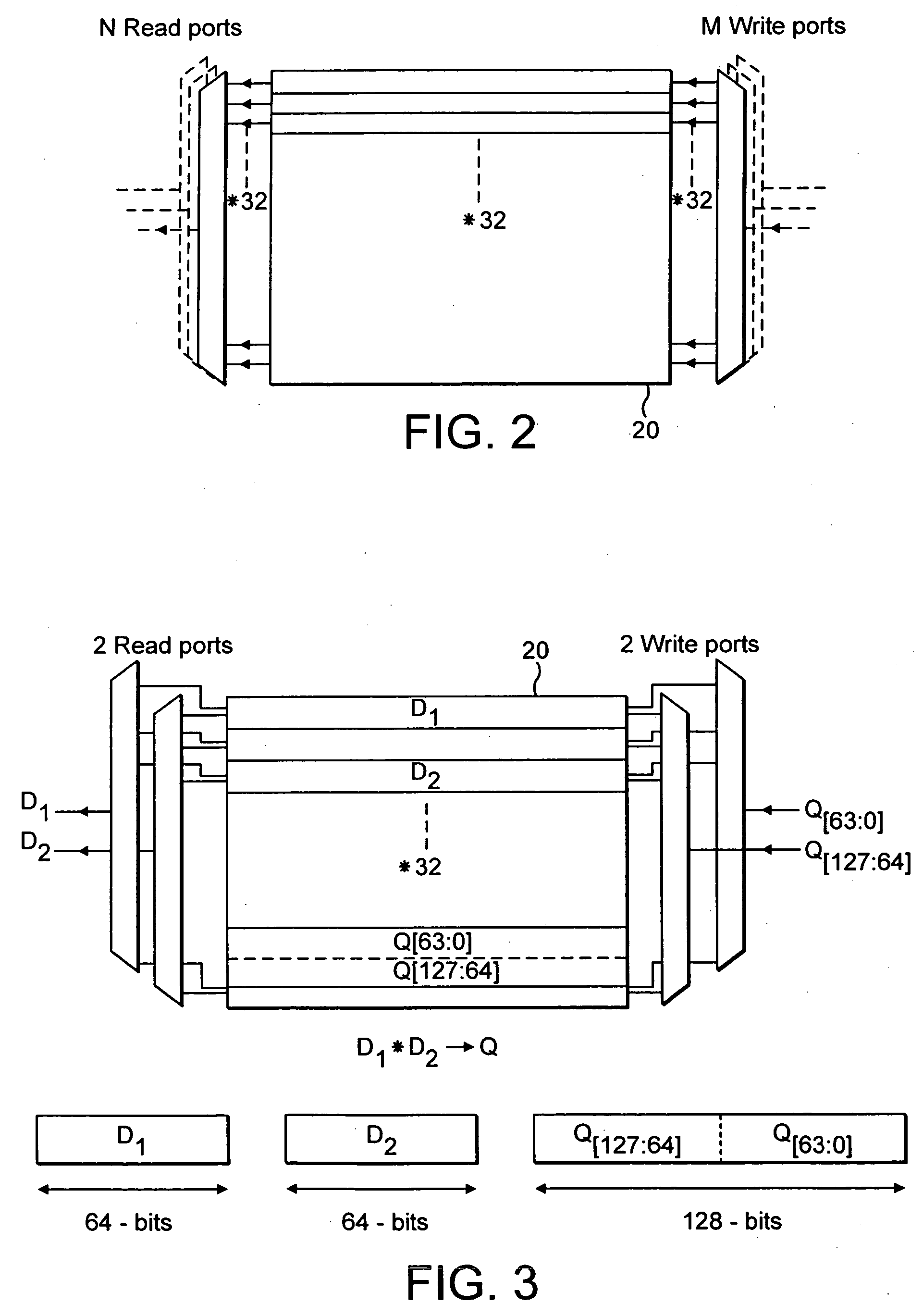

Endianess compensation within a SIMD data processing system

InactiveUS20050125647A1Single instruction multiple data multiprocessorsHandling data according to predetermined rulesData processing systemEndianness

A memory system can store data in either a big endian mode or a little endian mode. Memory accessing logic 810 utilises byte invariant addressing to retrieve multiple data elements from that memory to be stored within a SIMD register 812. Data element reordering logic 808 is responsive to an endianess mode specifying signal and a data element size specifying signal to reorder retrieved bytes such that the data elements when stored within the SIMD registers 812 are invariant irrespective of the endianess mode being used by the memory.

Owner:ARM LTD

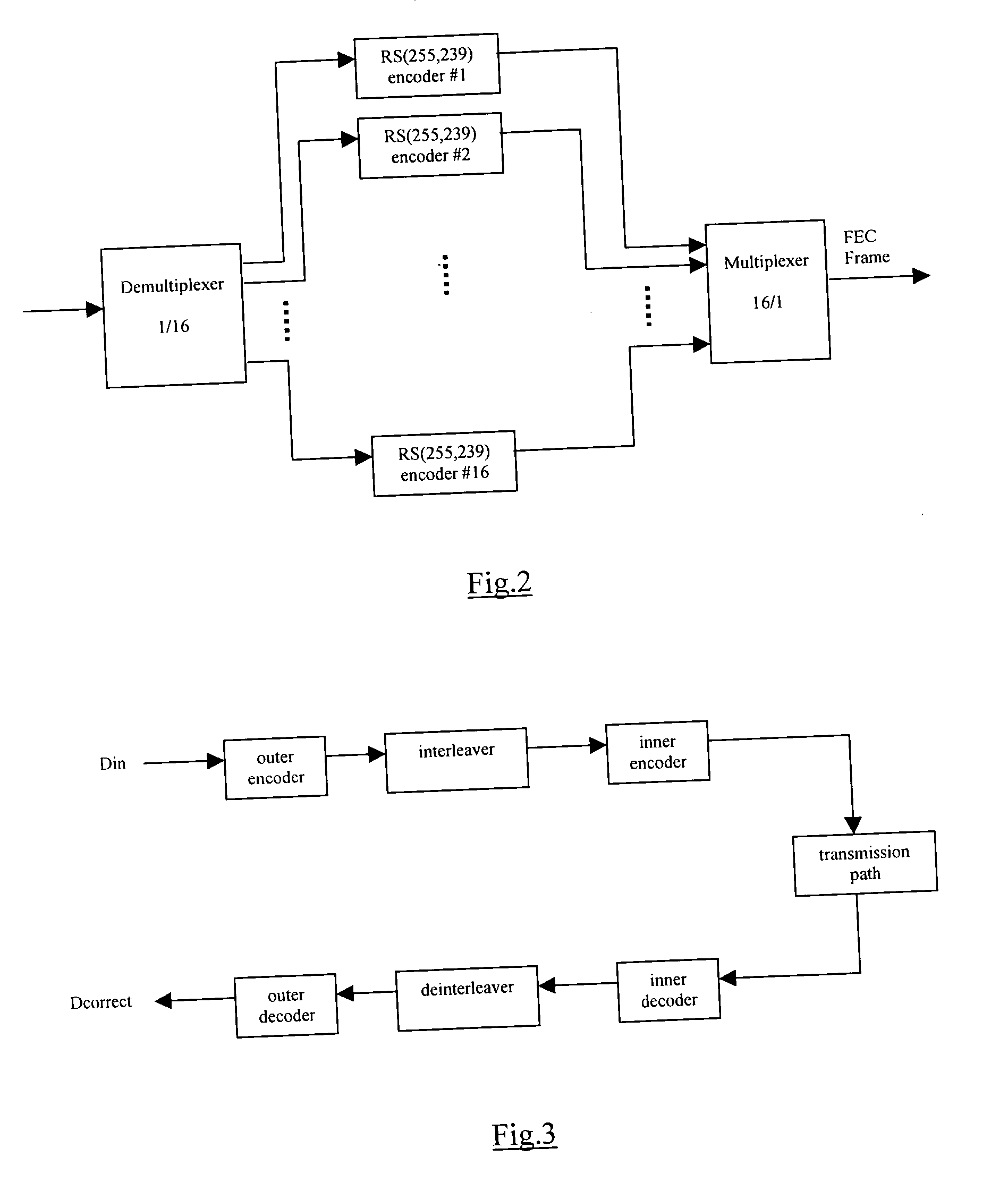

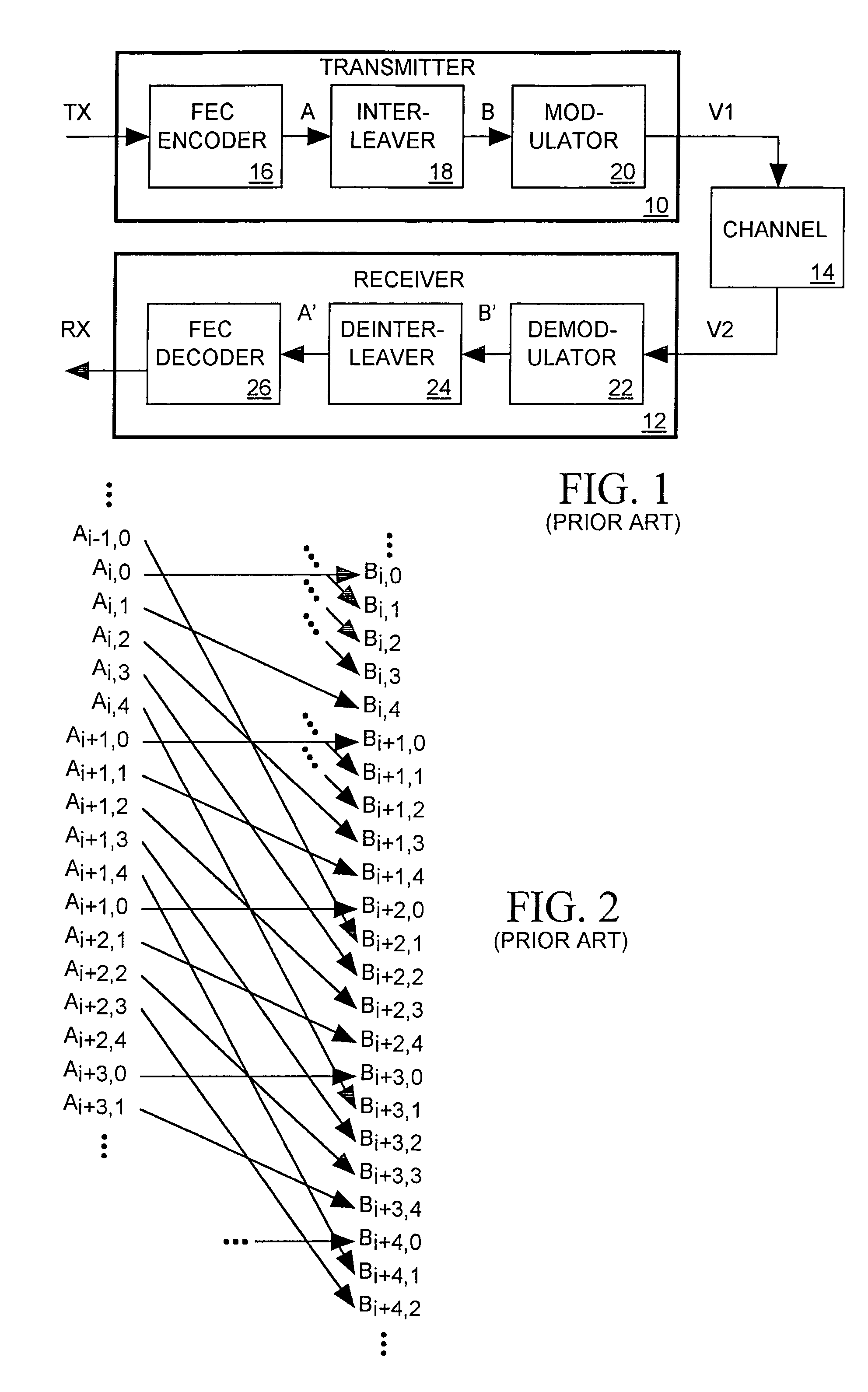

Optimized interleaving of digital signals

InactiveUS20050149820A1Improve network performanceLow costCode conversionError correction/detection by combining multiple code structuresEndiannessTrade offs

A method is described for changing the order of bytes of digital signals transmitted in frames according to a cyclic rotation of the bytes and for changing the frame format. This method can advantageously be used in concatenated coding scheme to achieve the best trade off between coding gain and line bit rate.

Owner:ALCATEL LUCENT SAS

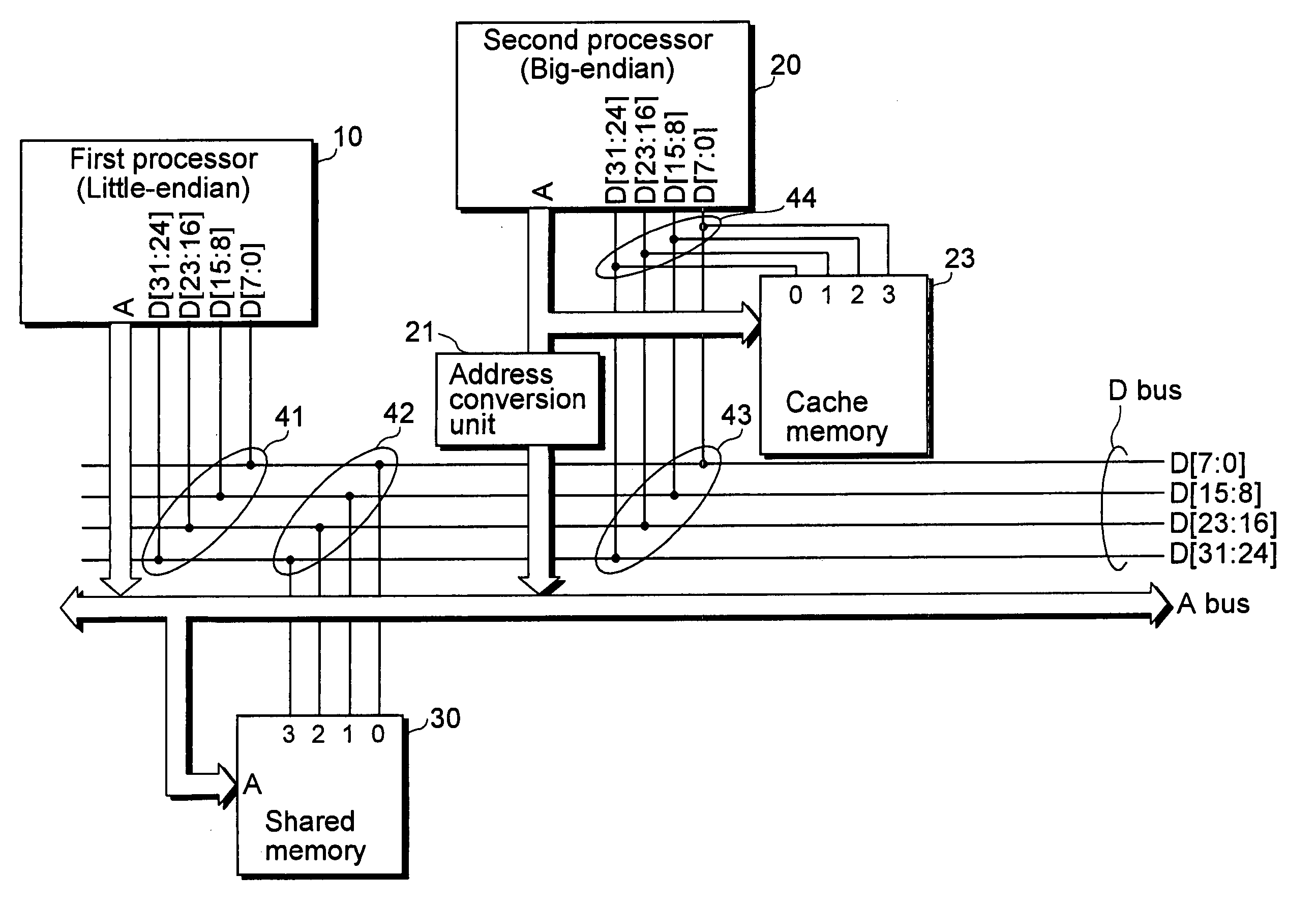

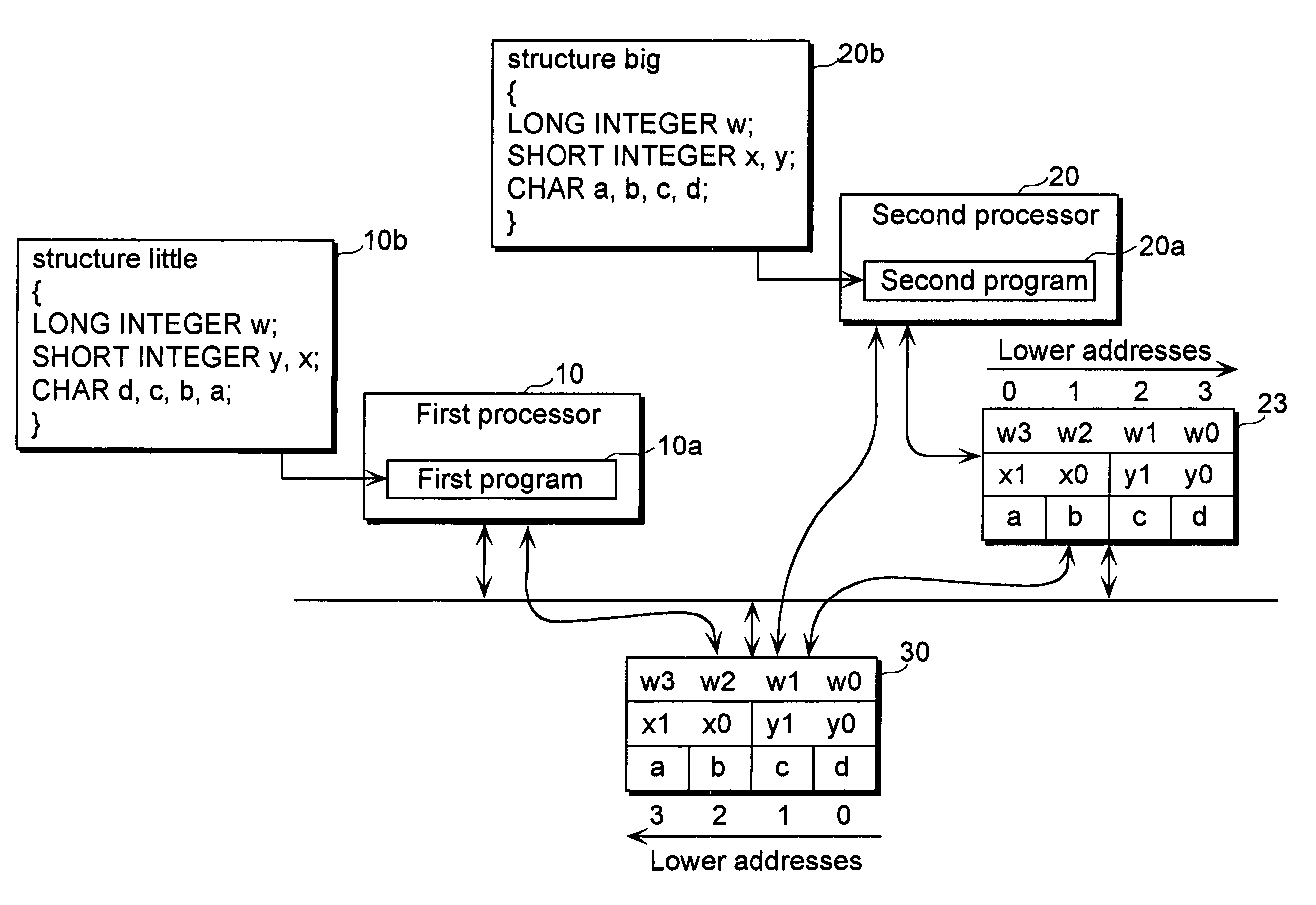

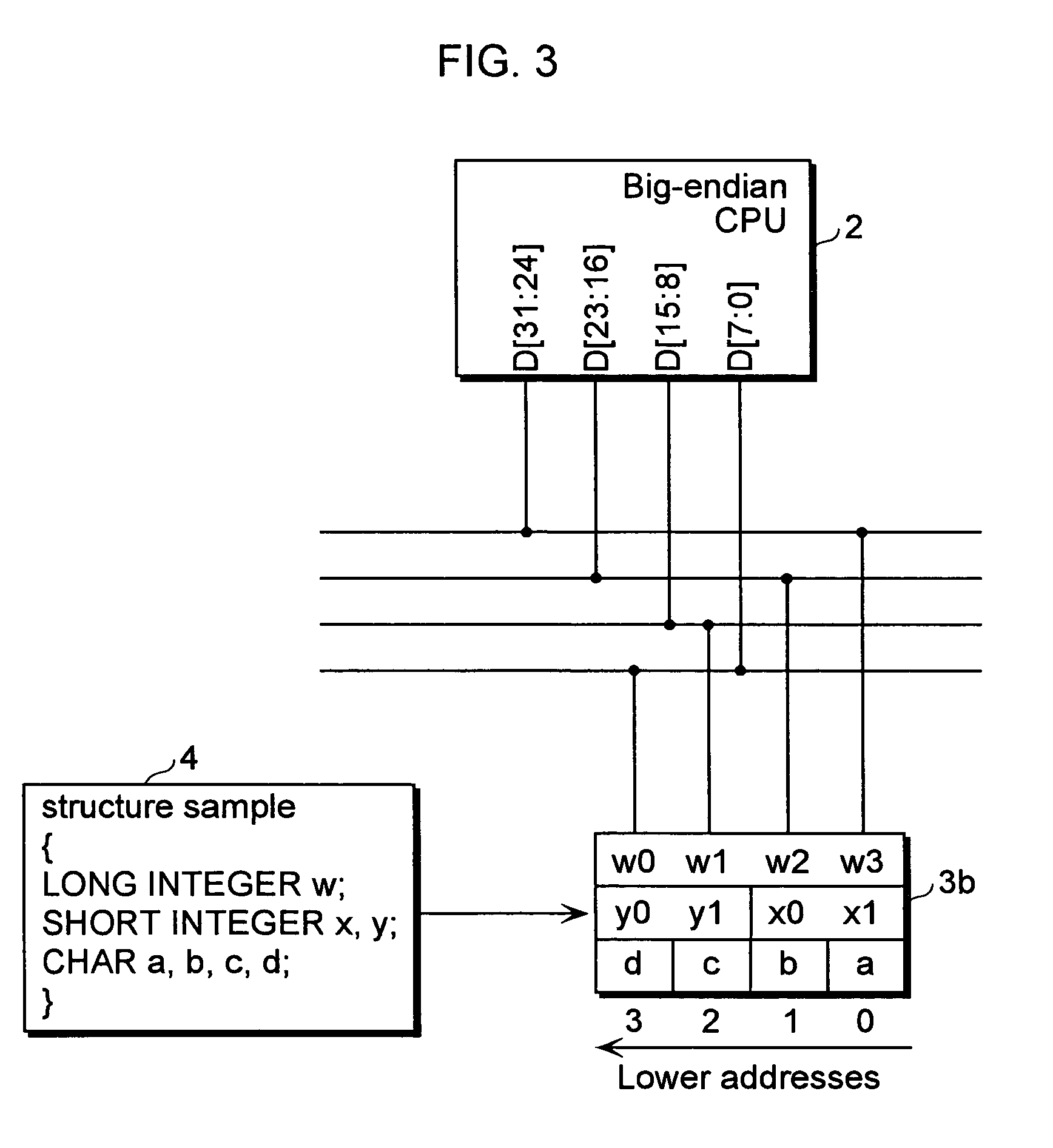

Data sharing apparatus and processor for sharing data between processors of different endianness

InactiveUS20040230765A1Simple structureSmall widthDigital data processing detailsMemory adressing/allocation/relocationEndiannessData sharing

The data sharing apparatus in the present invention includes a first processor 10 and a second processor 20, each of a different endianness, that are both connected to the memory via the data bus, in a byte order based on the endianness of the first processor 10. It also includes an address conversion unit 21 which converts at least one lower bit of an address to indicate a reversed position of data in the data bus, and outputs the converted address to the memory, in the case where the second processor 20 performs a memory access on the shared memory for data with a smaller width than the data bus.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

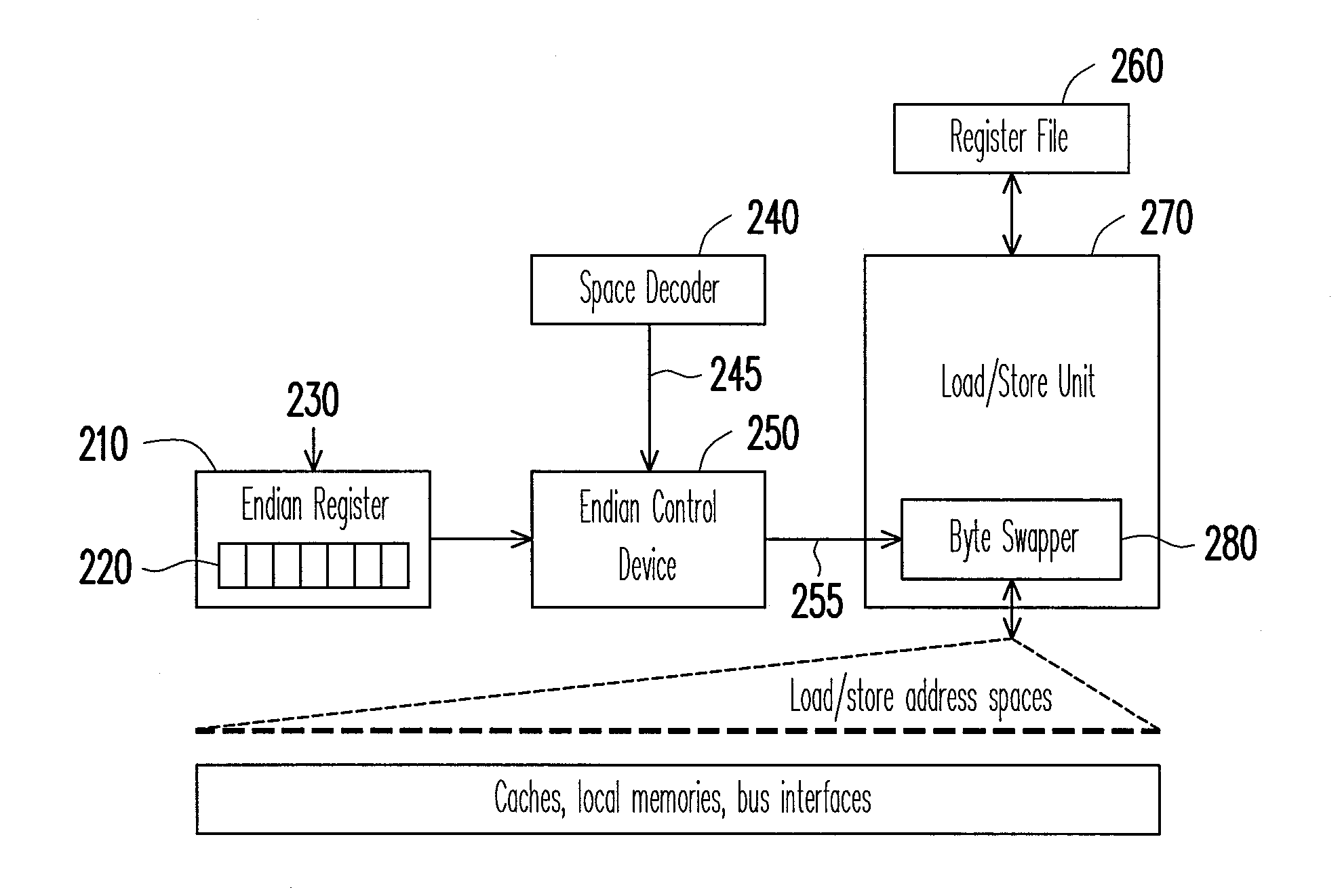

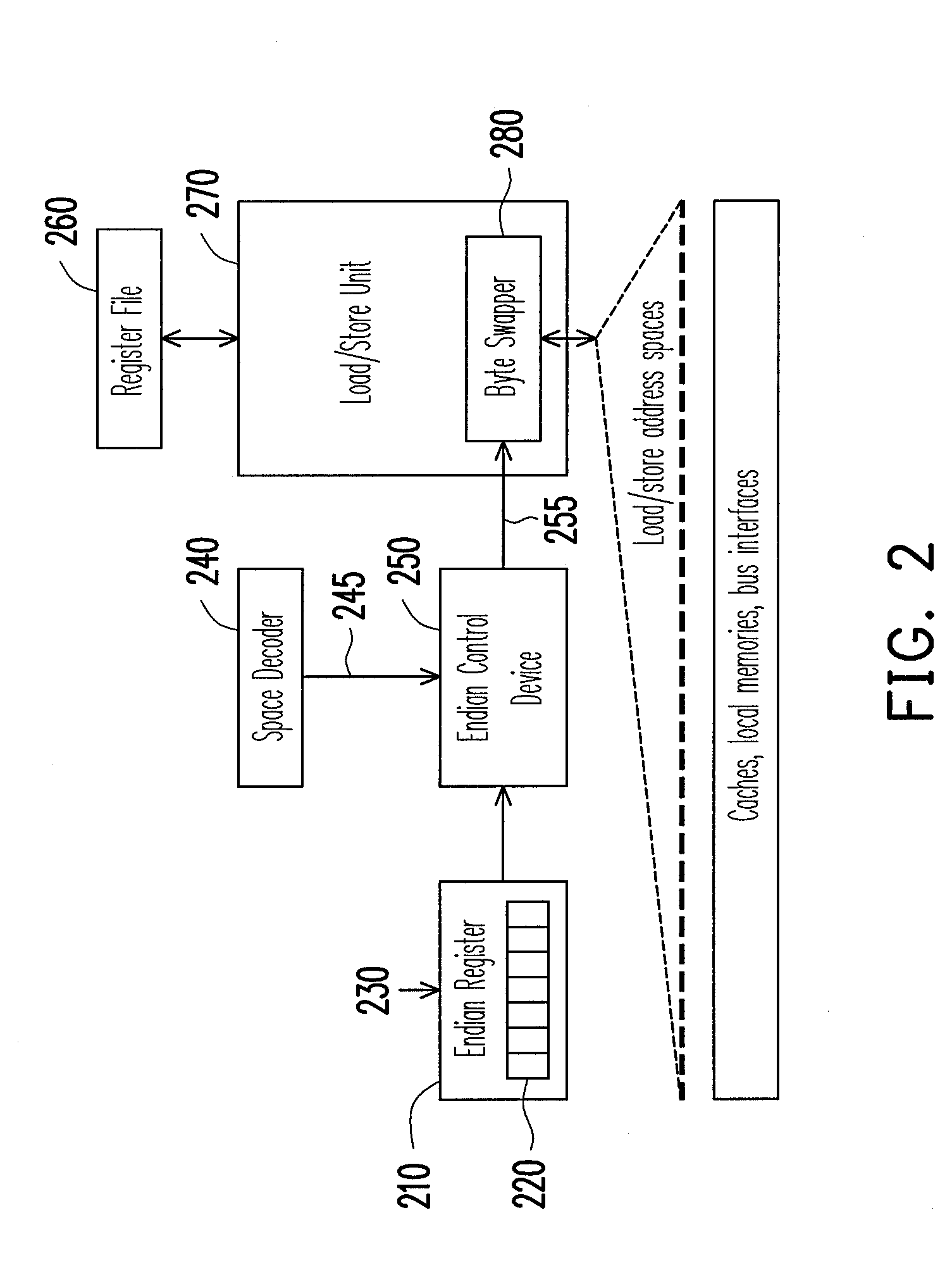

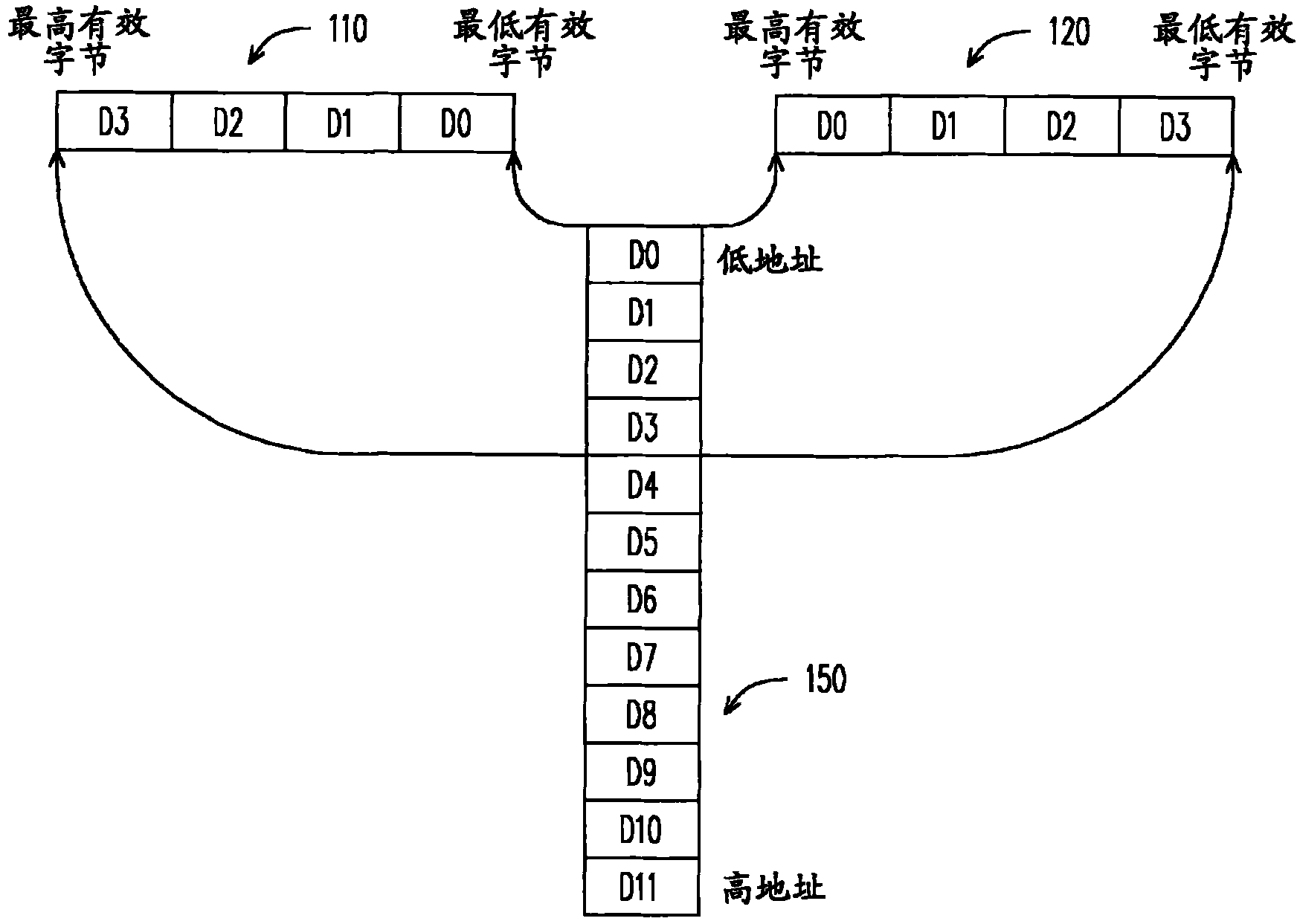

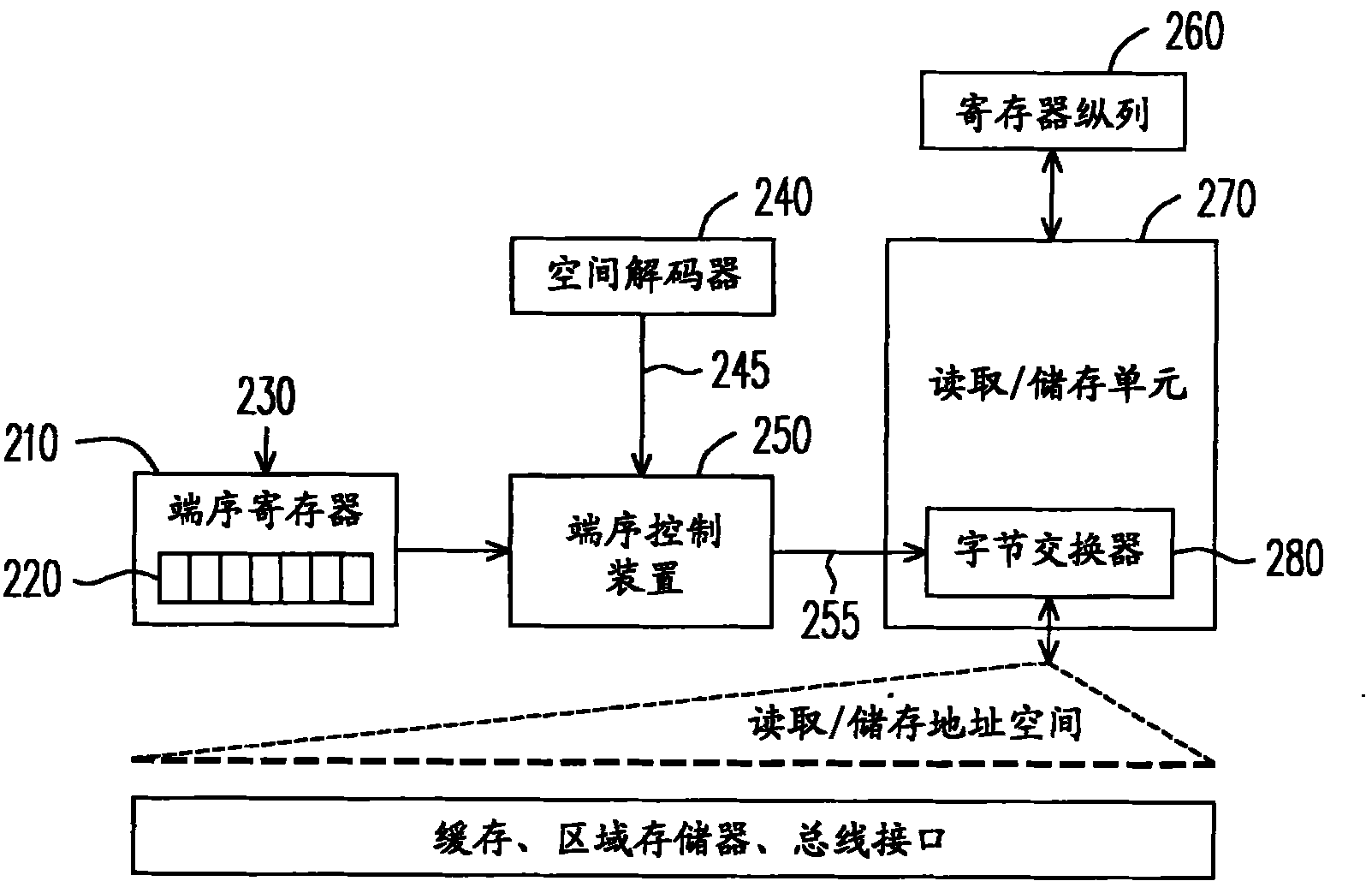

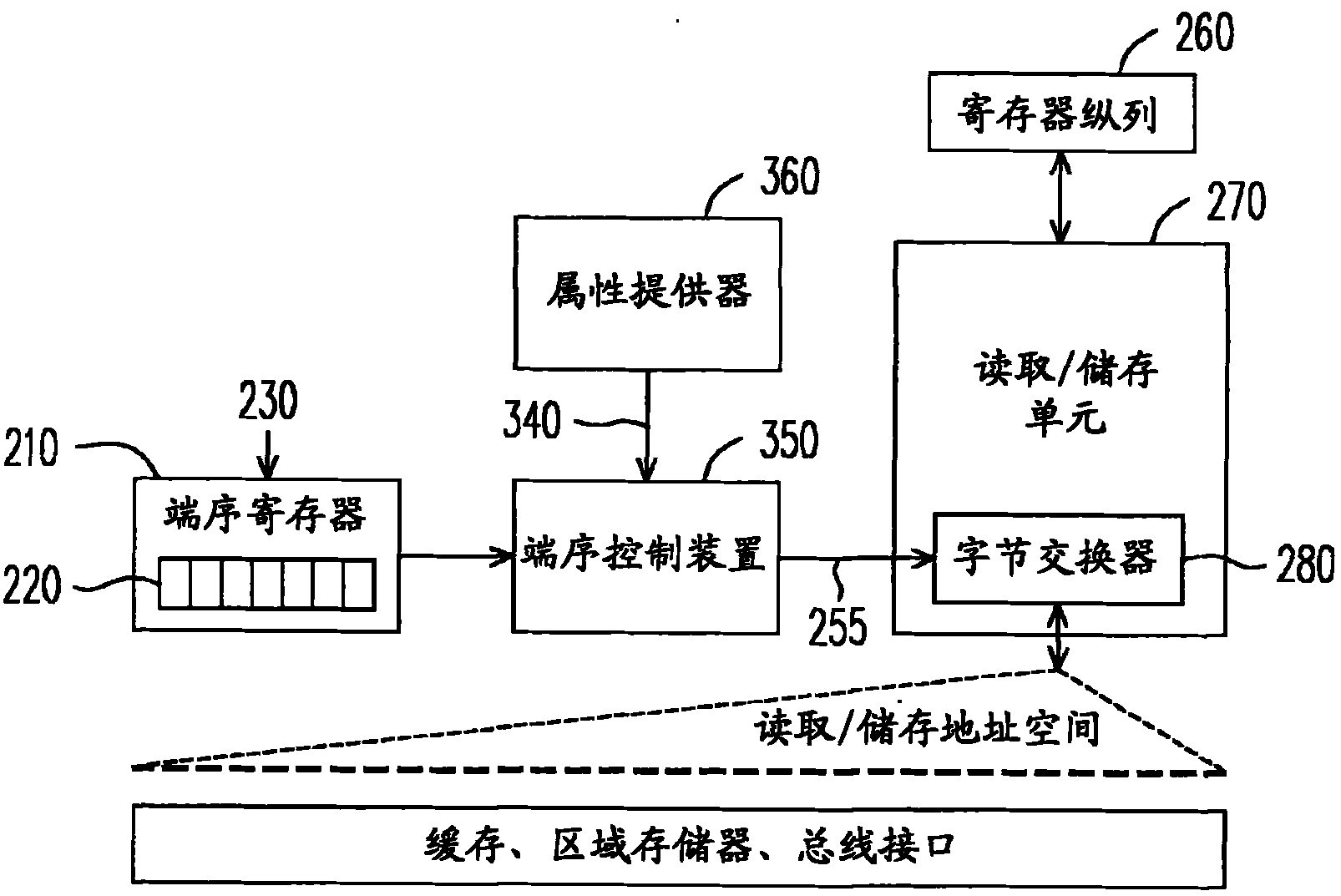

Data processing engine with integrated data endianness control mechanism

InactiveUS20110082999A1Simple software developmentMemory adressing/allocation/relocationMicro-instruction address formationEndiannessComputer science

A data processing engine is provided, which includes an endian register, an endian control device, and a byte swapper. The endian register stores a plurality of endian control bits. Each endian control bit indicates the default data endianness of a type of address space accessible to the data processing engine. Each endian control bit is in either a big-endian state or a little-endian state. The endian control device is coupled to the endian register. The endian control device provides an endian signal according to the endian control bits and the instruction executed by the data processing engine. The endian signal is in either the big-endian state or the little-endian state. The byte swapper is coupled to the endian control device. The byte swapper transmits data and changes the byte order of the data when the byte order of the data is inconsistent with the state of the endian signal.

Owner:ANDES TECH

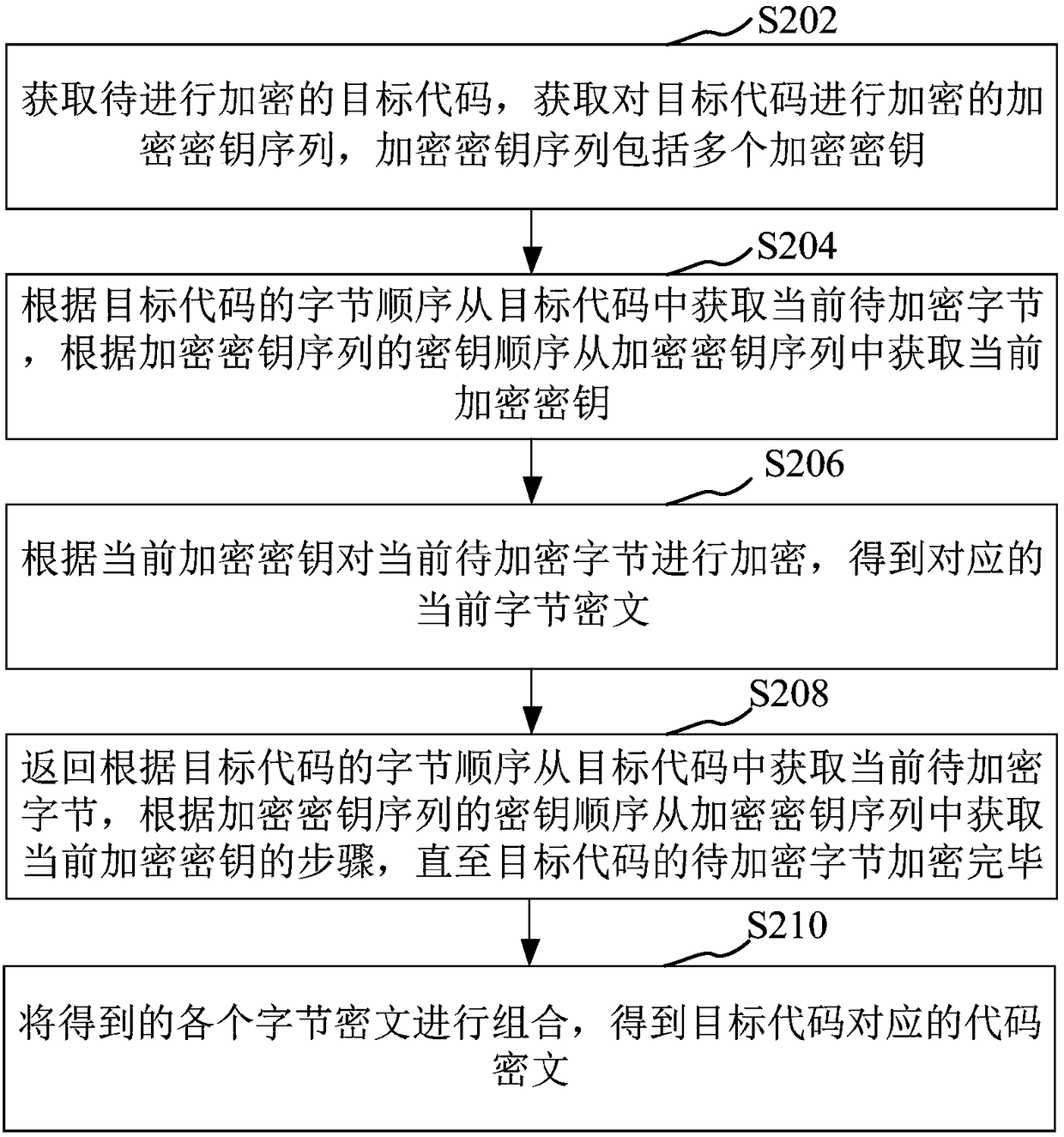

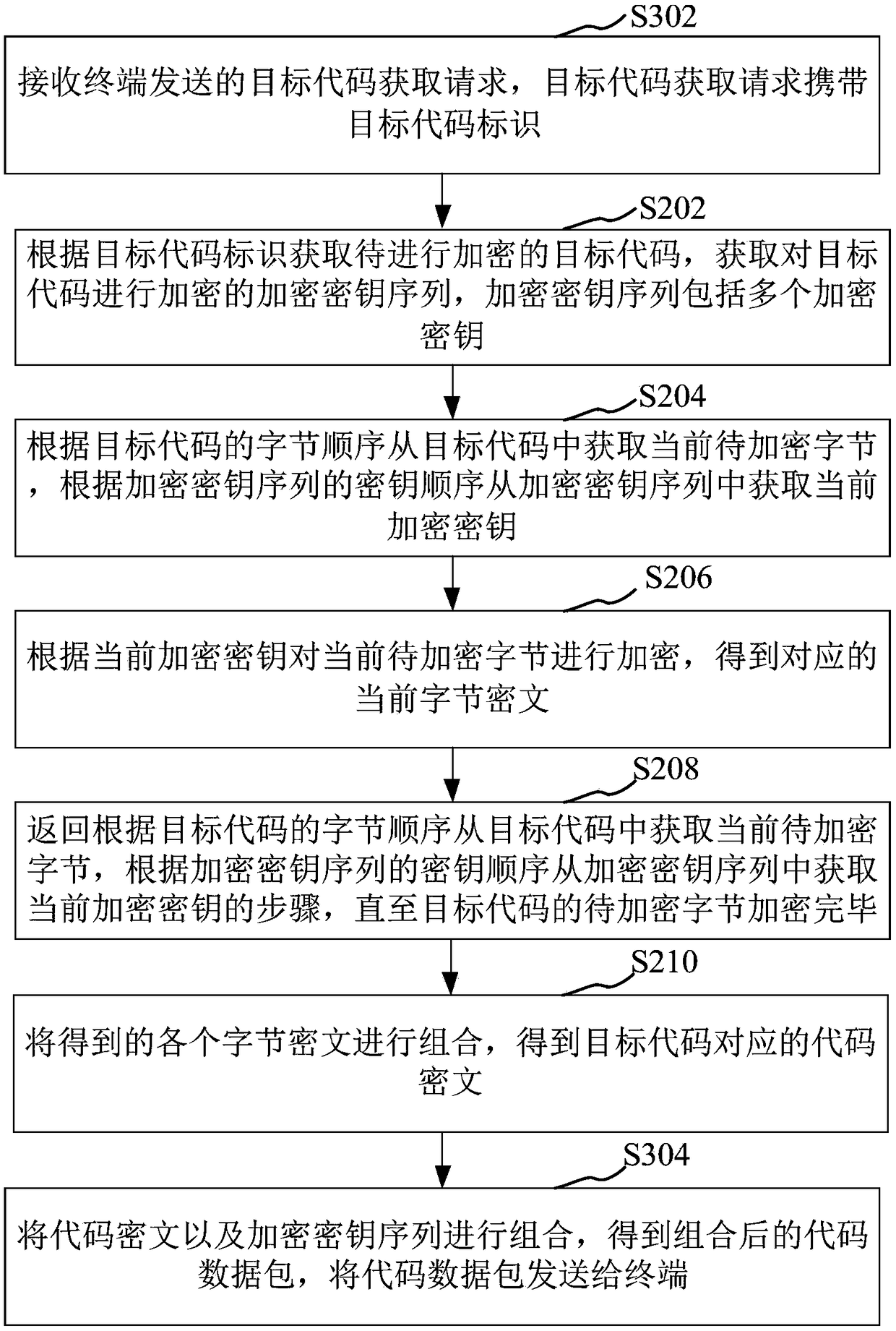

Code encryption and decryption methods and devices, computer device and storage medium

InactiveCN108390759AImprove securityIncrease the difficultyMultiple keys/algorithms usageEncryption apparatus with shift registers/memoriesEndiannessCiphertext

The invention relates to code encryption and decryption methods and devices, a computer device and a storage medium. The code encryption method comprises the steps of acquiring a to-be-encrypted target code, and acquiring an encryption key sequence for encrypting the target code, wherein the encryption key sequence comprises multiple encryption keys; acquiring a current to-be-encrypted byte from the target code according to a byte sequence of the target code, and acquiring a current encryption key from the encryption key sequence according to the key sequence of the encryption key sequence; encrypting the current to-be-encrypted byte according to the current encryption key, so as to obtain a corresponding current byte ciphertext; returning to the step of acquiring the current to-be-encrypted byte from the target code according to the byte sequence of the target code and acquiring the current encryption key from the encryption key sequence according to the key sequence of the encryptionkey sequence till all to-be-encrypted bytes of the target code are encrypted; and combining all obtained byte ciphertexts, so as to obtain a code ciphertext corresponding to the target code. The method can improve the code security.

Owner:PINGAN PUHUI ENTERPRISE MANAGEMENT CO LTD

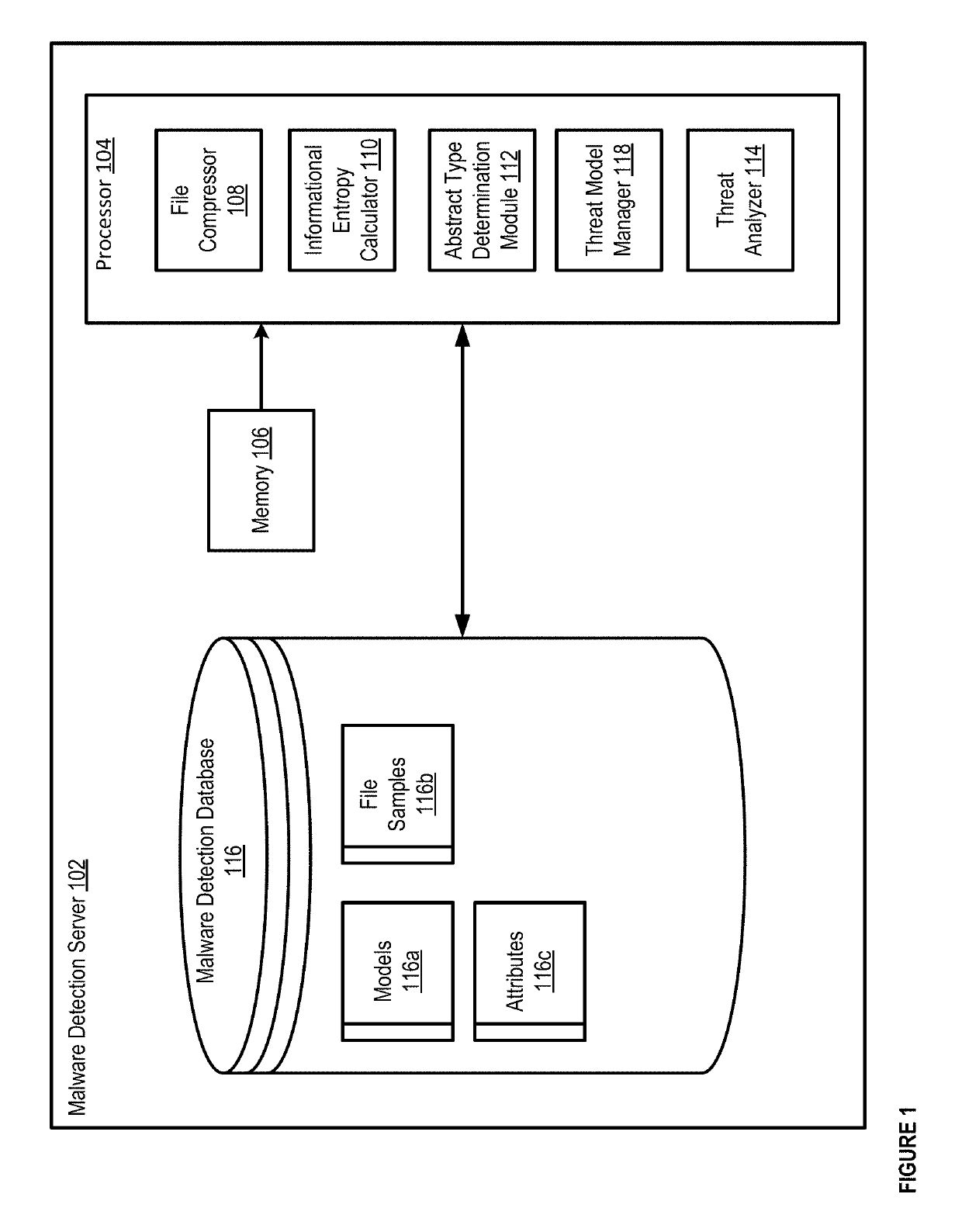

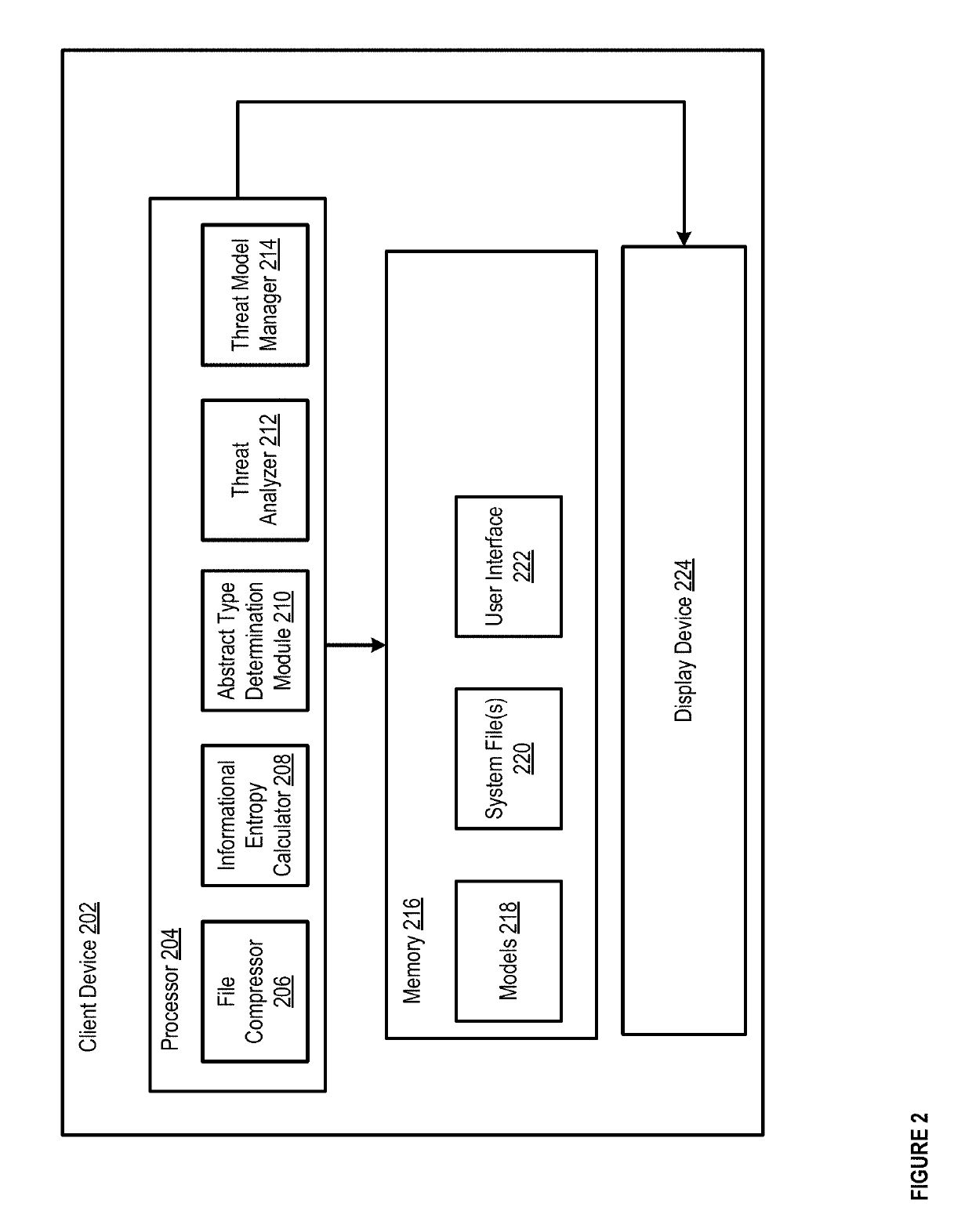

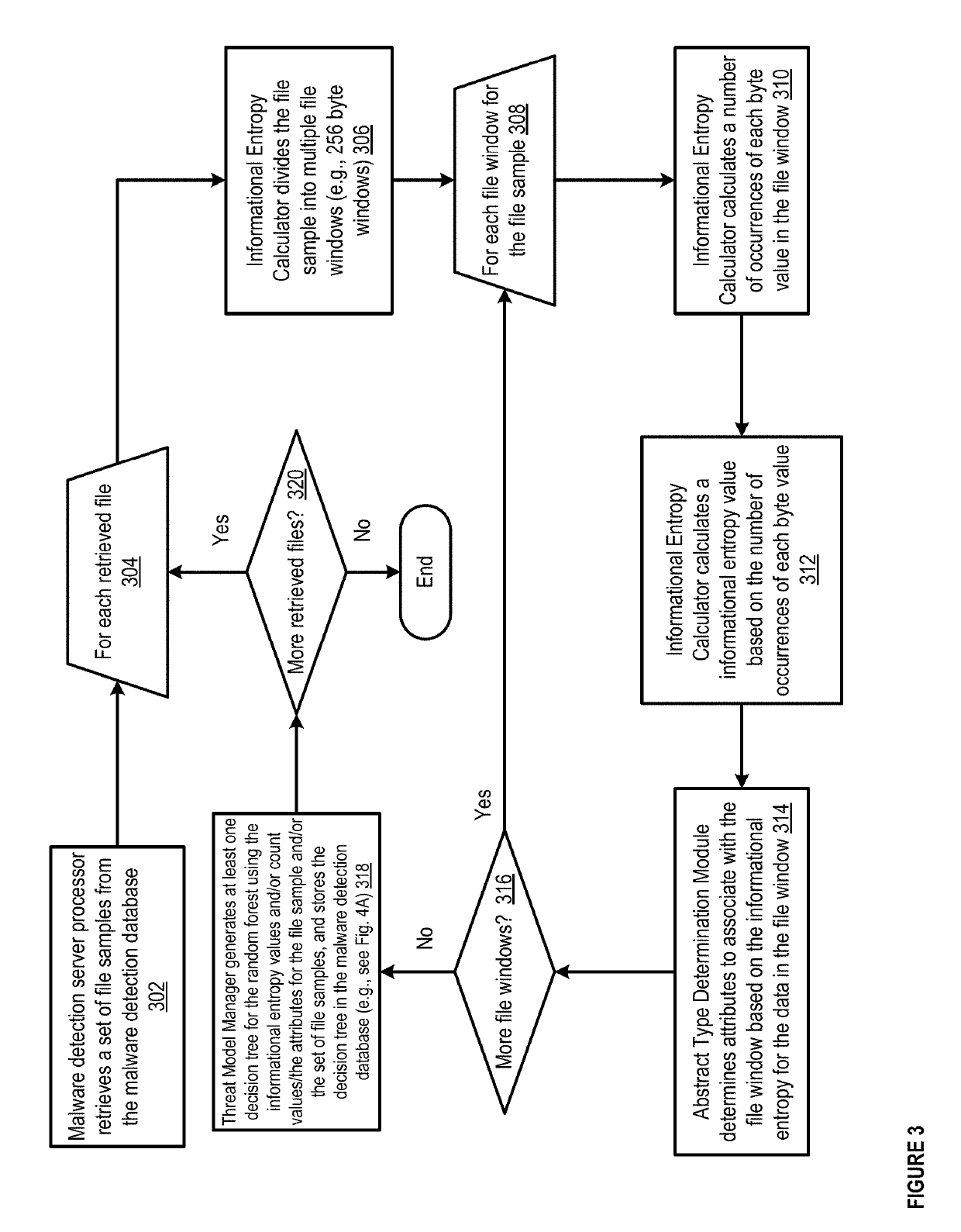

Methods and apparatus for machine learning based malware detection

Apparatus and methods describe herein, for example, a process that can include receiving a potentially malicious file, and dividing the potentially malicious file into a set of byte windows. The process can include calculating at least one attribute associated with each byte window from the set of byte windows for the potentially malicious file. In such an instance, the at least one attribute is not dependent on an order of bytes in the potentially malicious file. The process can further include identifying a probability that the potentially malicious file is malicious, based at least in part on the at least one attribute and a trained threat model.

Owner:INVINCEA

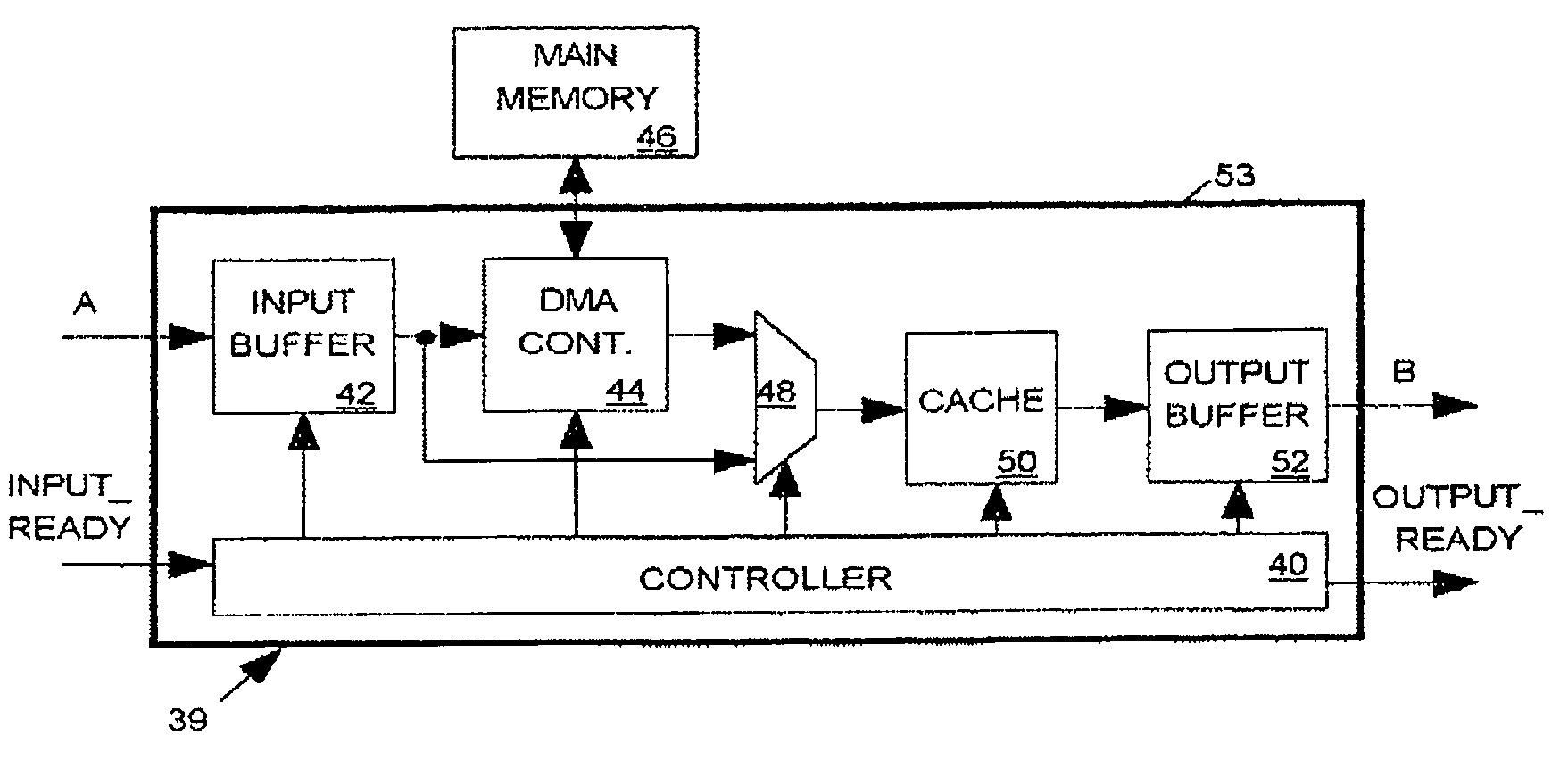

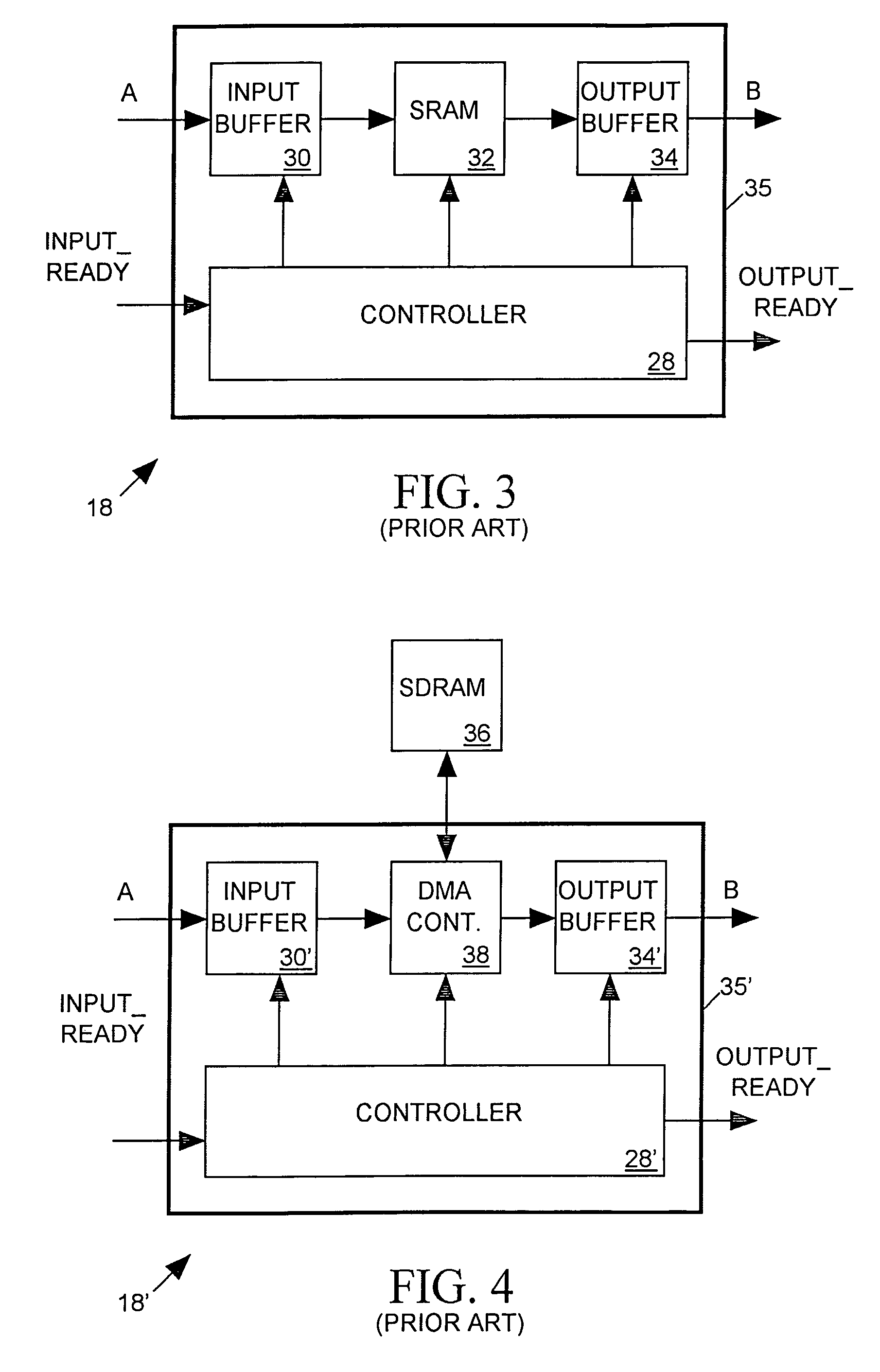

Convolutional interleaver and deinterleaver

ActiveUS7600163B2Improve throughputImprove transmission efficiencyMultiplex system selection arrangementsError correction/detection using convolutional codesEndiannessParallel computing

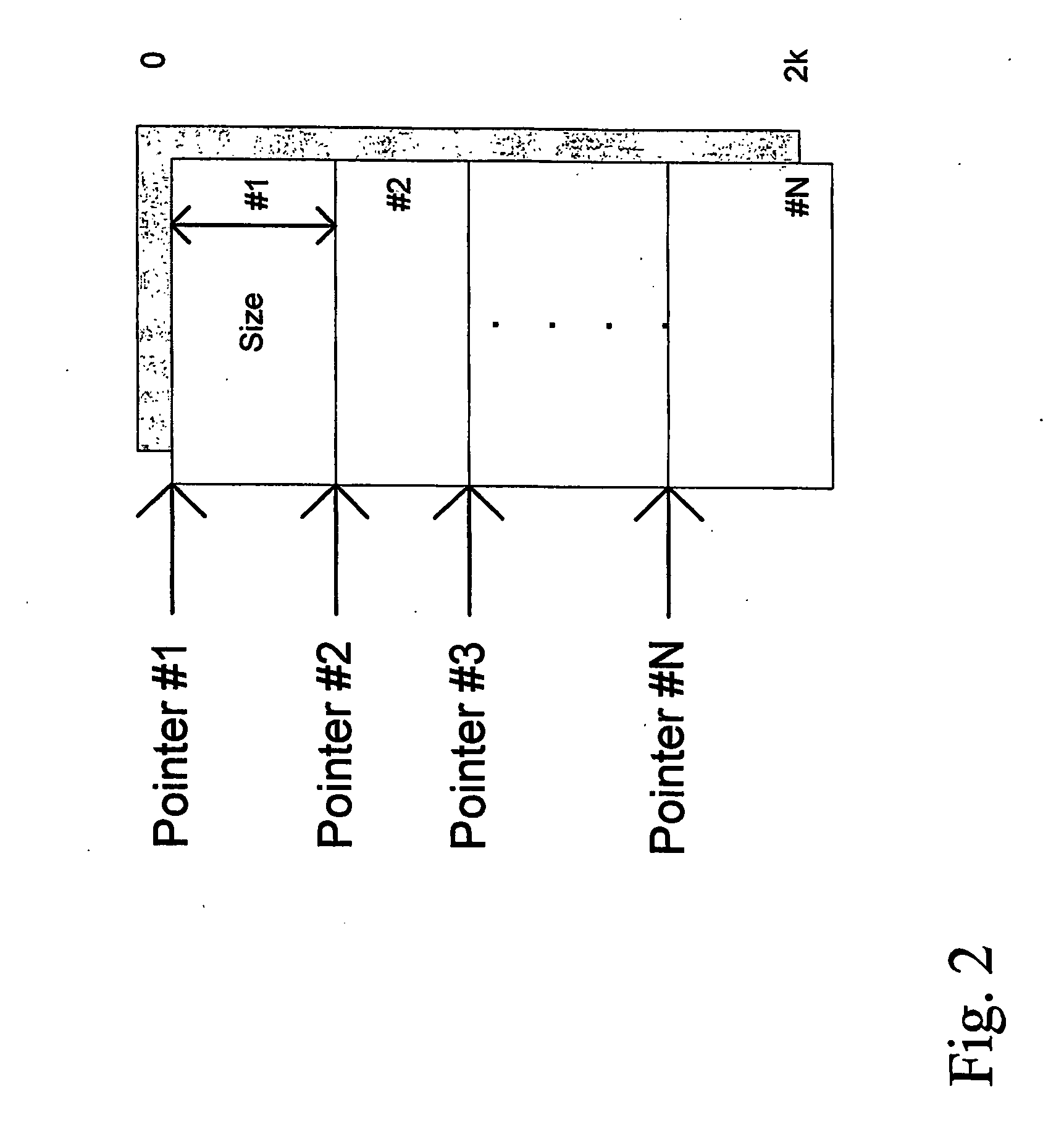

An apparatus for receiving and storing an incoming sequence and for forwarding the bytes of the incoming sequence as an outgoing sequence in a different byte order includes a cache memory and a main memory for storing bytes of the incoming sequence until they can be forwarded as bytes of the outgoing sequence. A control circuit selectively burst mode writes sequences of incoming bytes that need be stored for a relatively long time to blocks of sequential addresses of the main memory, writes individual bytes of the incoming sequence that need be stored for a relatively short time to selected addresses of the cache memory, and reads bytes out of the cache memory and the main memory when needed to form the outgoing sequence.

Owner:REALTEK SEMICON CORP

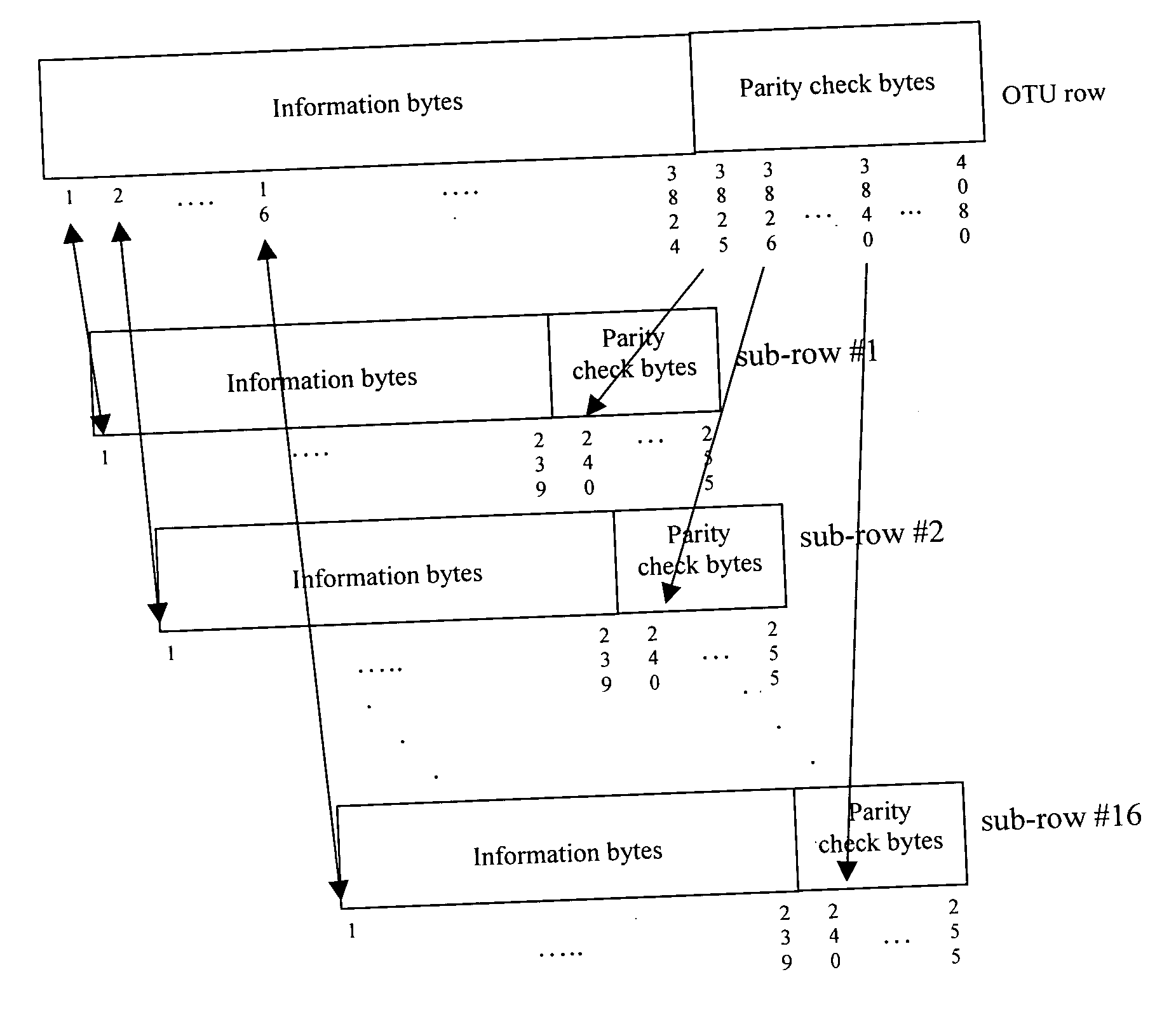

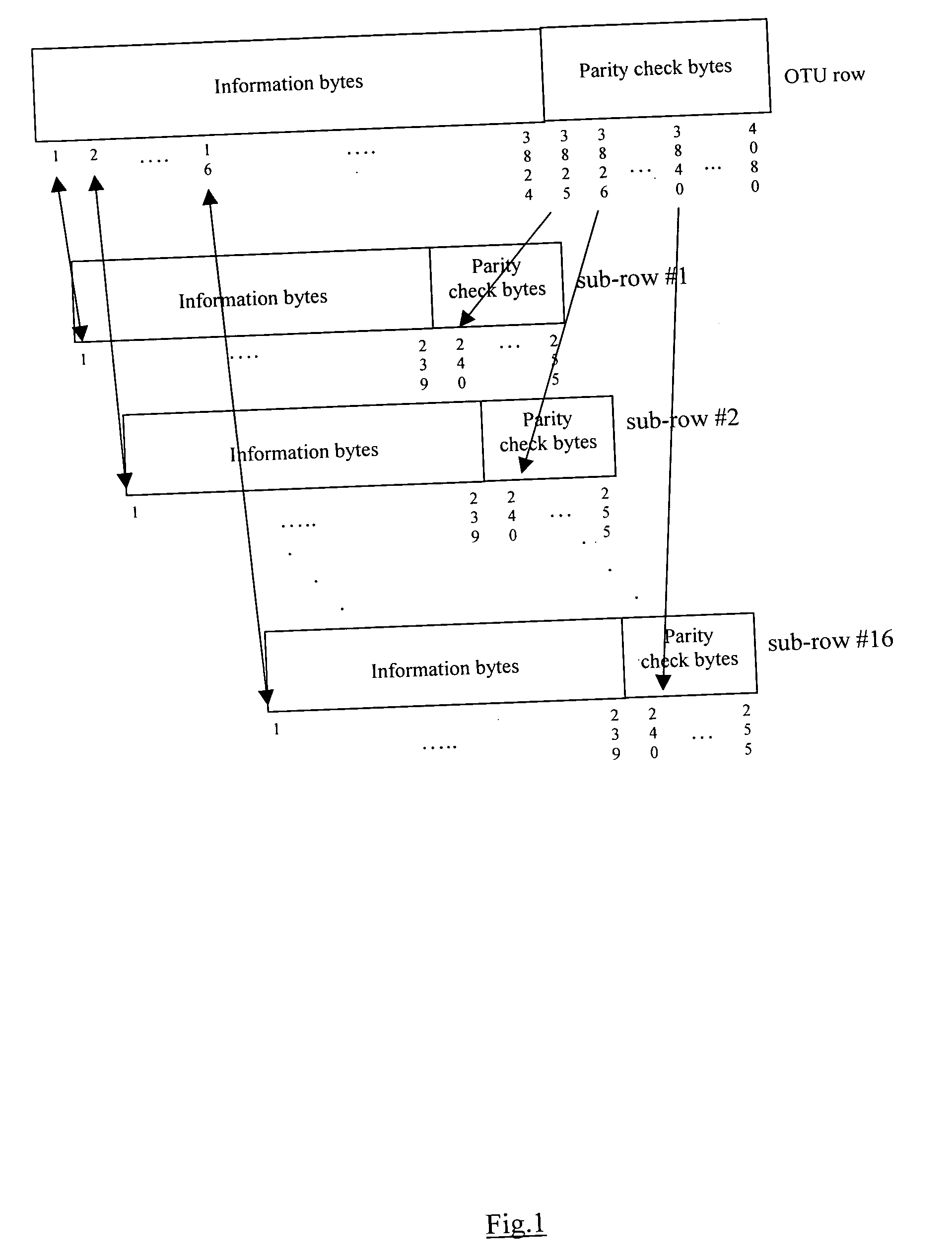

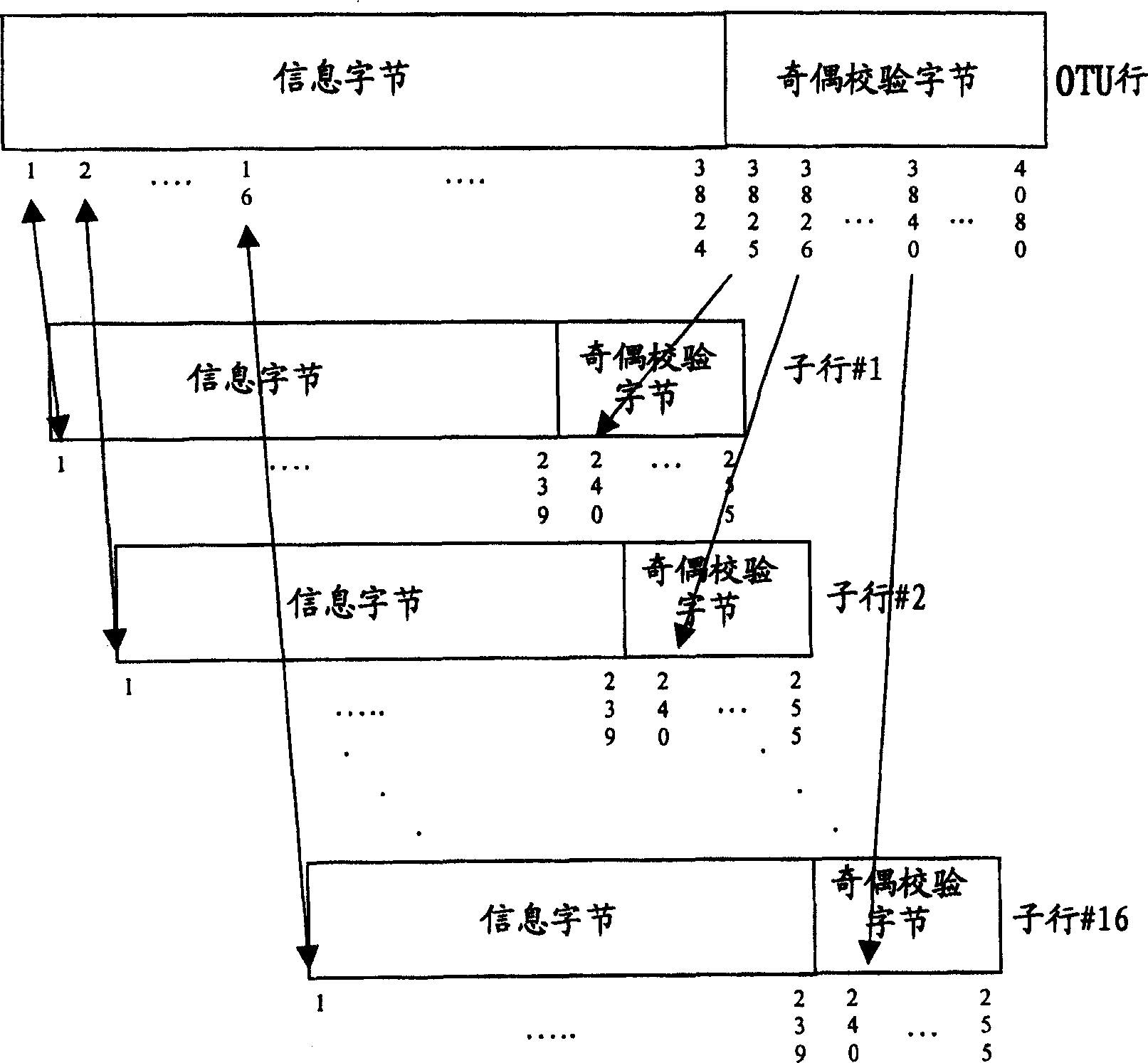

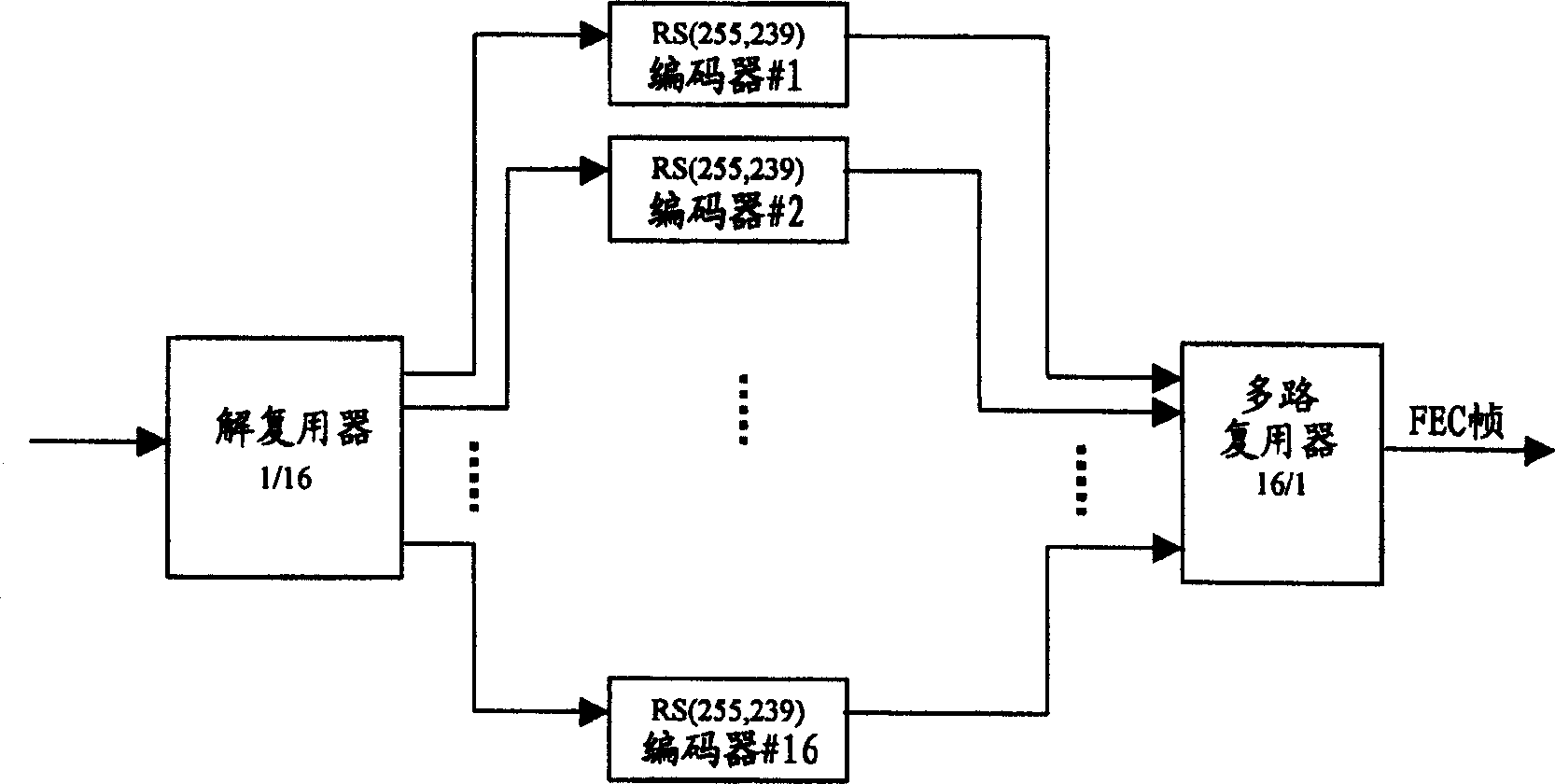

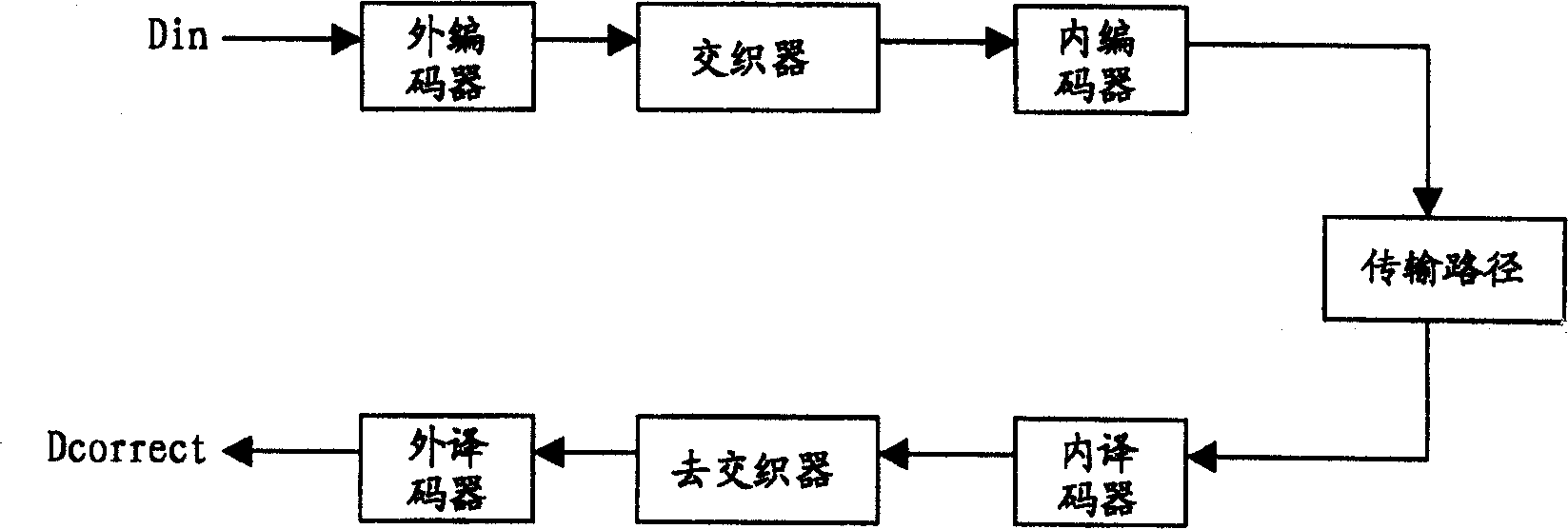

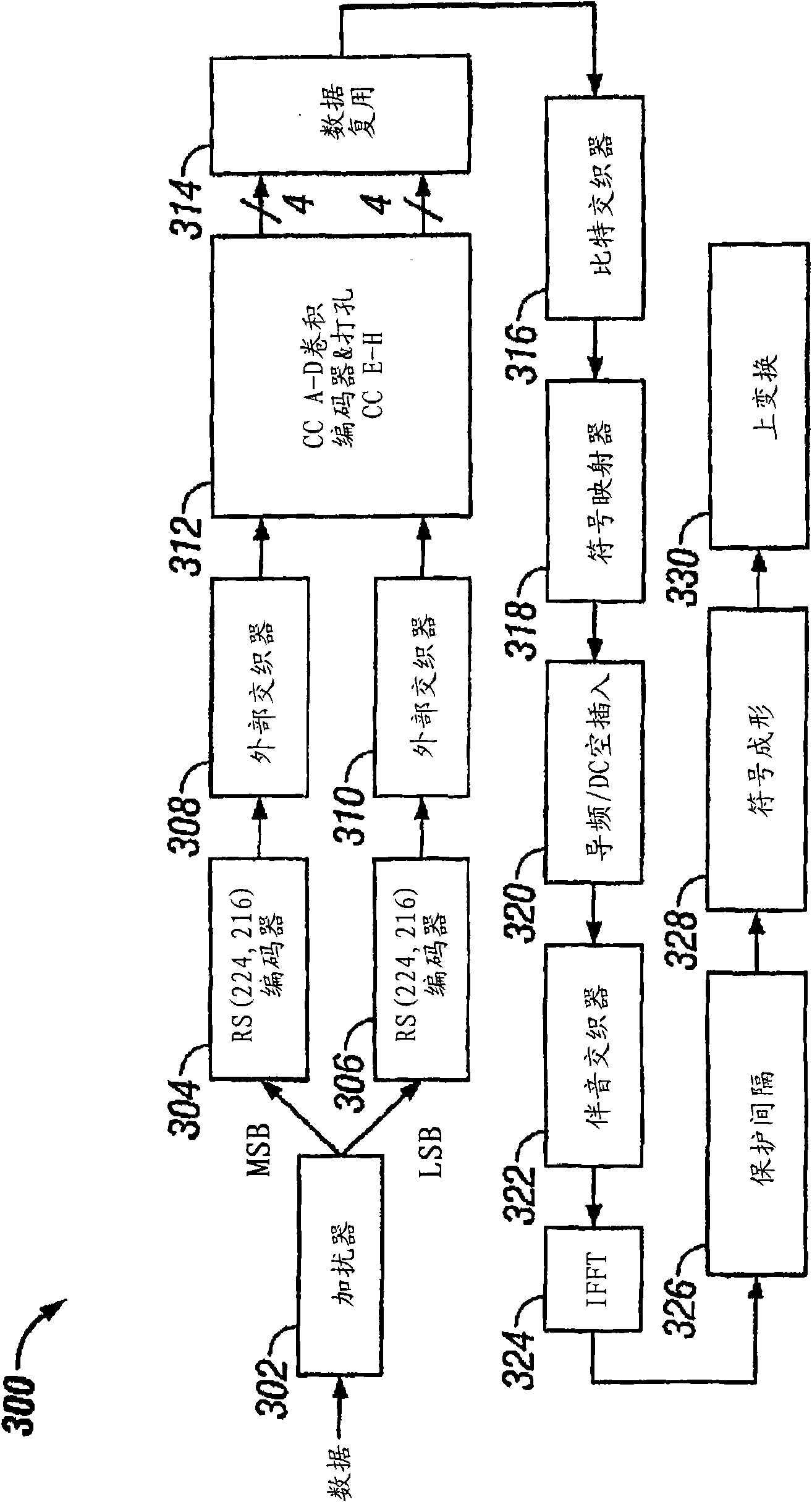

Optimized interleaving of digital signals

InactiveCN1630207AImprove transmission distanceIncrease capacityError preventionCode conversionEndiannessGain

A method is described for changing the order of bytes of digital signals transmitted in frames according to a cyclic rotation of the bytes and for changing the frame format. This method can advantageously be used in a concatenated coding scheme, e.g a serial concatenation of two Reed-Solomon codes, to achieve the best trade off between coding gain and line bit rate. The disclosed interleaving method is applicable to optical transport networks. <IMAGE>

Owner:ALCATEL LUCENT SAS

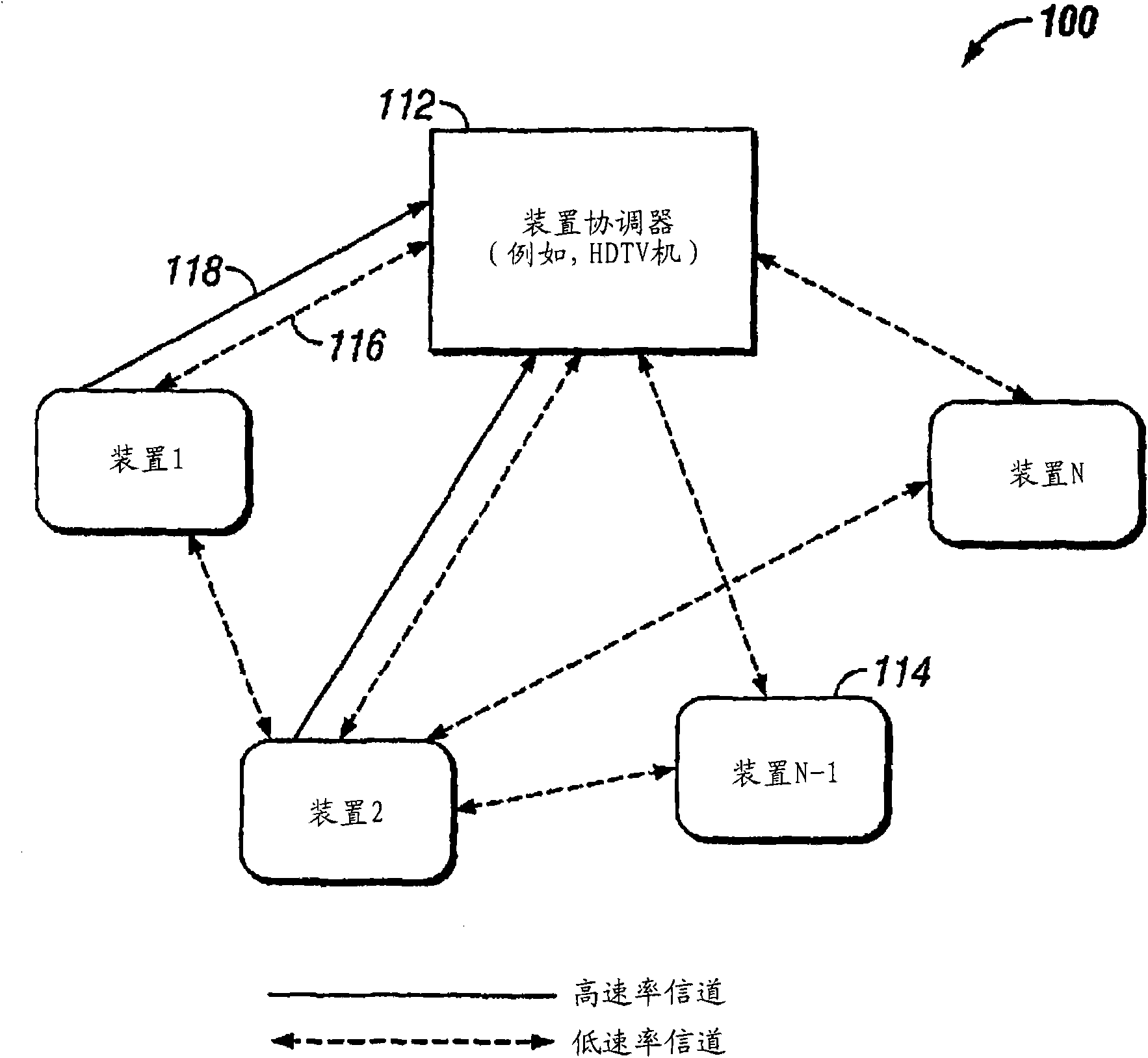

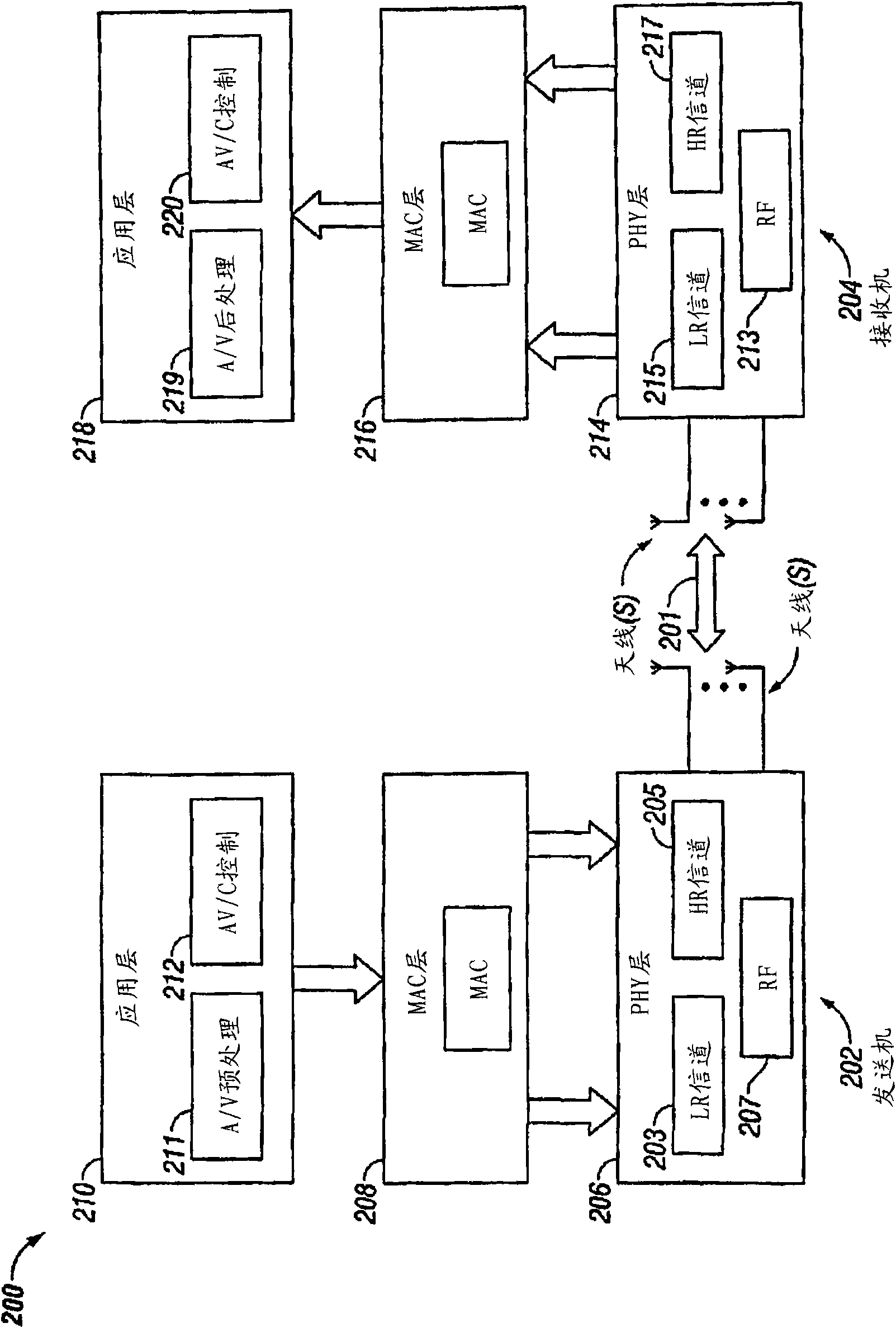

System and method for processing wireless high definition video data using a shortened last codeword

InactiveCN101675631AImprove decoding performanceError correction/detection using convolutional codesOther error detection/correction/protectionEndiannessHigh-definition video

A method and system for processing high definition video data to be transmitted over a wireless medium is disclosed. In one embodiment, the method includes receiving an information packet having the length of L bytes, wherein L=(MOEOE)+A, and where: M is the depth of an interleaver, n is the number of interleavers, K is an encoding code length and A is the number of remainder bytes with respect to MOEOE bytes, wherein the remainder bytes are located at the end of the information packet. MOEOE bytes represent MOE codewords, wherein the remainder bytes sequentially form a plurality of remaindercodewords, and wherein the plurality of remainder codewords comprise a last codeword which is located at the end of the remainder codewords. The method further includes i) shortening the last codeword such that the resultant shortened codeword is shorter in length than each of the remaining codewords of the information packet and ii) adding dummy bits to the outer encoded data so as to meet a predefined size requirement for an outer interleaver.

Owner:SAMSUNG ELECTRONICS CO LTD

Data sharing apparatus and processor for sharing data between processors of different endianness

InactiveUS7587557B2Simple structureDigital data processing detailsMemory adressing/allocation/relocationEndiannessData sharing

The data sharing apparatus in the present invention includes a first processor and a second processor, each of a different endianness, that are both connected to the memory via the data bus, in a byte order based on the endianness of the first processor. It also includes an address conversion unit which converts at least one lower bit of an address to indicate a reversed position of data in the data bus, and outputs the converted address to the memory, in the case where the second processor performs a memory access on the shared memory for data with a smaller width than the data bus.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

Methods and Systems to Accomplish Variable Width Data Input

Disclosed are methods and systems for variable width data input to a pattern-recognition processor. A variable width data input method may include receiving bytes over a data bus having a first width and receiving one or more signals indicating the validity of each of the one or more bytes The valid bytes may be sequentially provided to a pattern-recognition processor in an 8-bit wide data stream. In an embodiment, a system may include one or more address lines configured to provide the one or more signals indicating the validity of the bytes transferred over the data bus. The system may include a buffer and control logic to sequentially process the valid bytes.

Owner:MICRON TECH INC

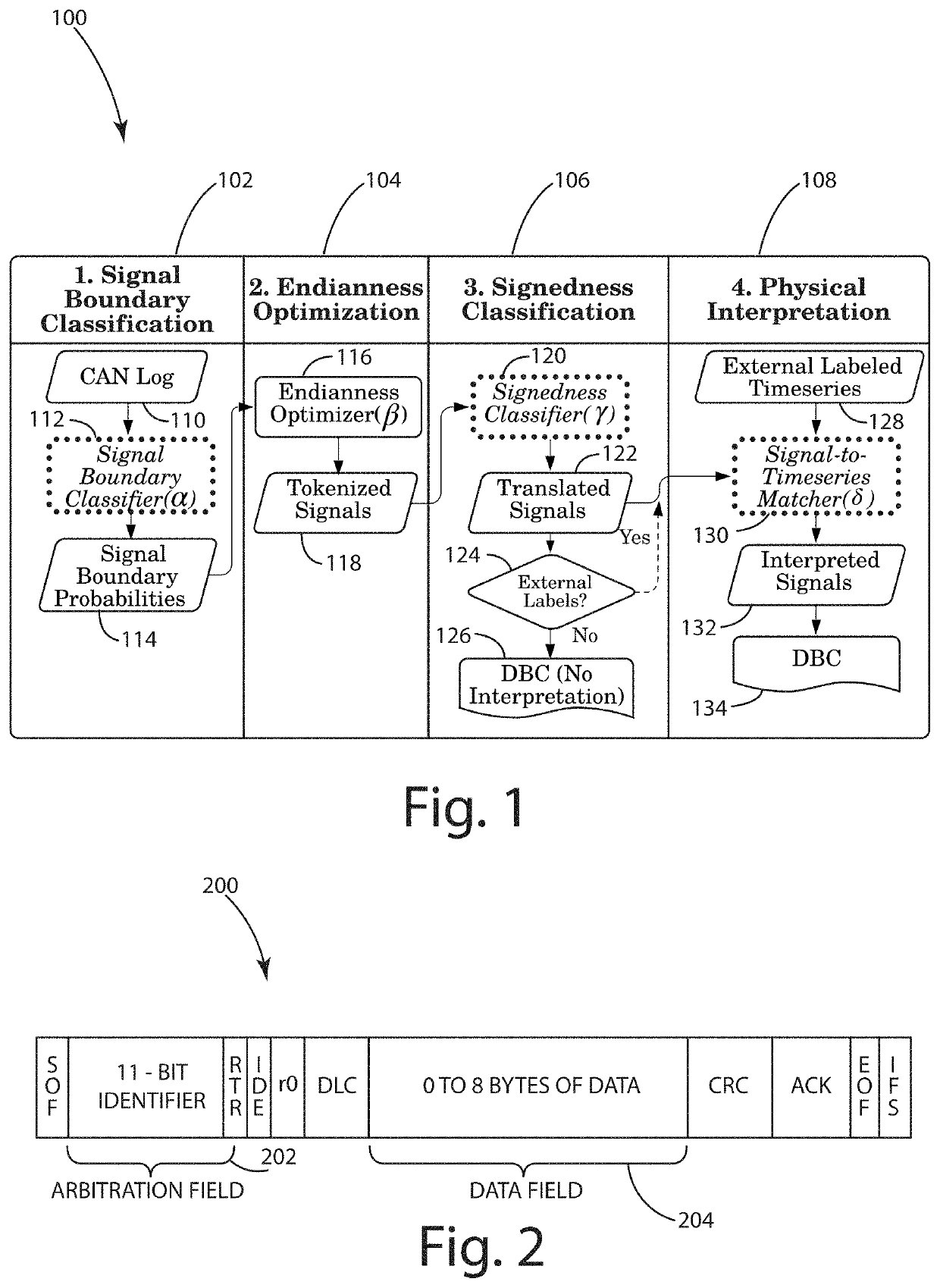

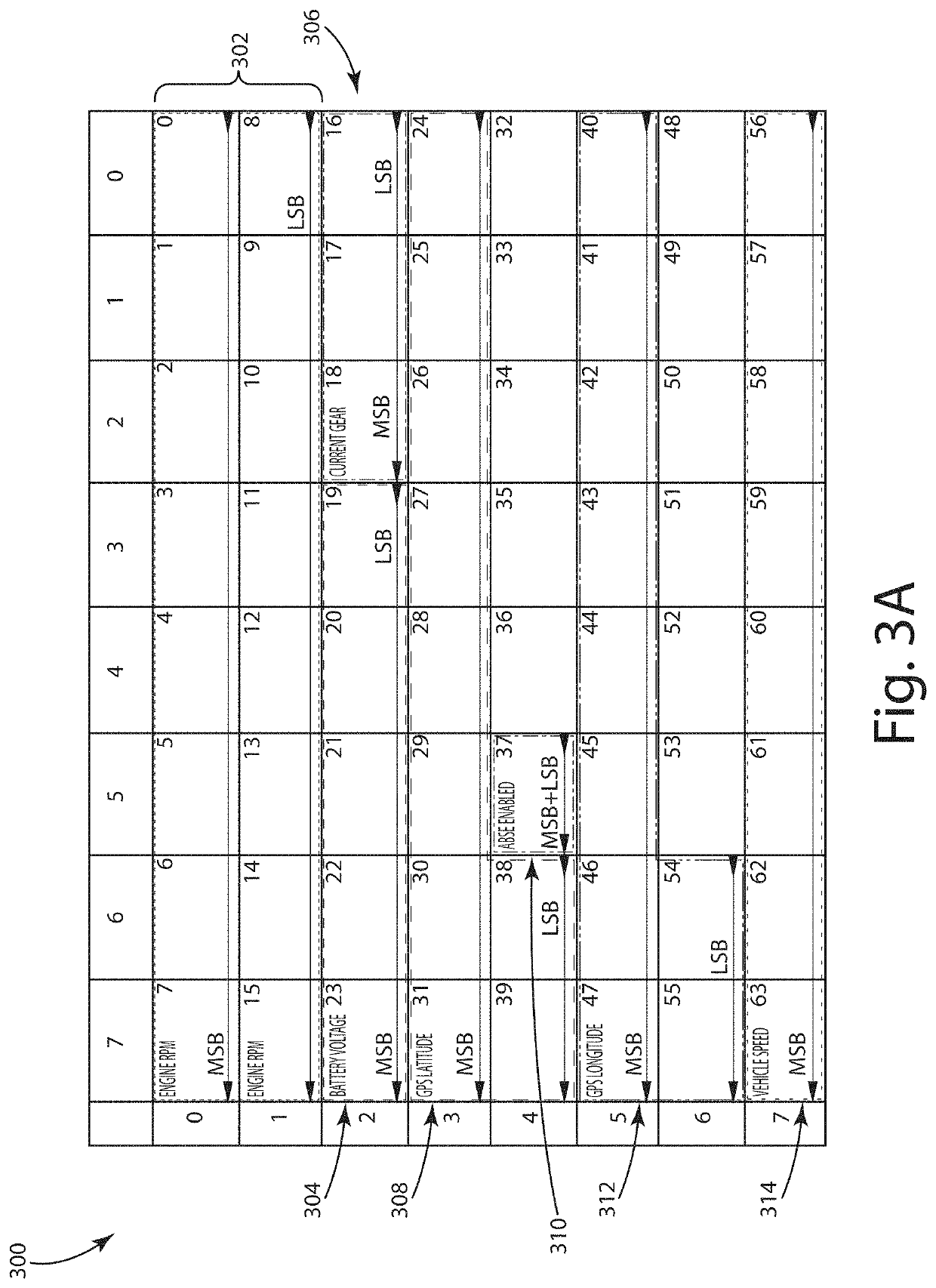

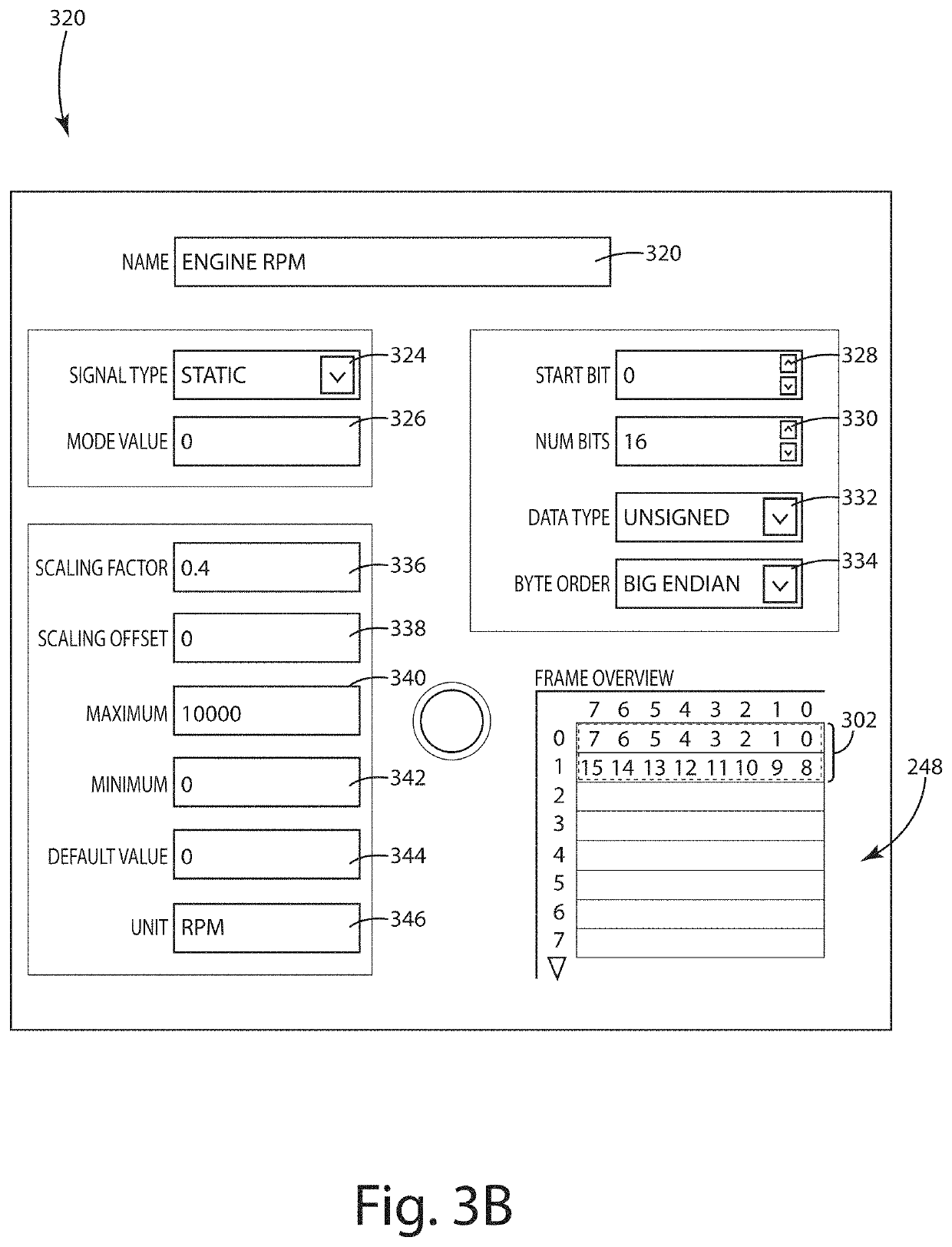

Controller area network decoder (can-d)

PendingUS20210178996A1Registering/indicating working of vehiclesMachine learningData packArea network

A system and method for decoding an unknown automotive controller area network (“CAN”) message definitions. CAN data vehicle signal mappings are typically held in secret and varied by automotive model and year. Without knowledge of the mappings, the wealth of real-time vehicle data hidden in the automotive CAN packets is uninterpretable—impeding research, after-market tuning, efficiency and performance monitoring, fault diagnosis, and privacy-related technologies. This technology can ascertain the CAN signals' boundaries (start bit and length), endianness (byte ordering), signedness (binary-to-integer encoding) from raw CAN data. This allows conversion of CAN data to time series. Interpreting the translated CAN data's physical meaning and finding a linear mapping to standard units (e.g., knowing the signal is speed and scaling values to represent units of miles per hour) can be achieved for many signals by leveraging diagnostic standards to obtain real-time measurements of in-vehicle systems. The system and method can be integrated into lightweight hardware enabling an OBD-II plugin for real-time in-vehicle CAN decoding or run on standard computers. The system can output a standard DBC file with the signal definition information.

Owner:UT BATTELLE LLC

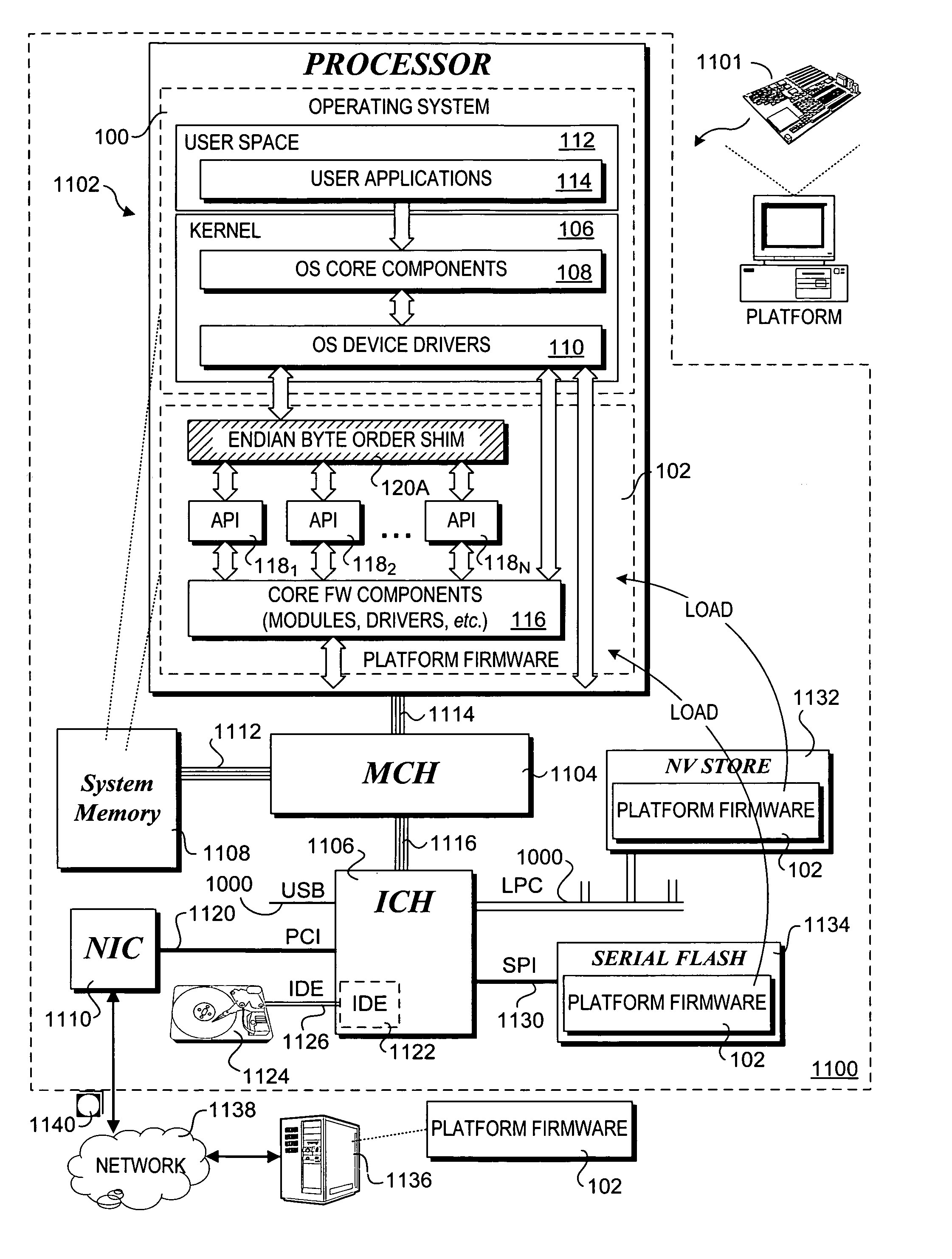

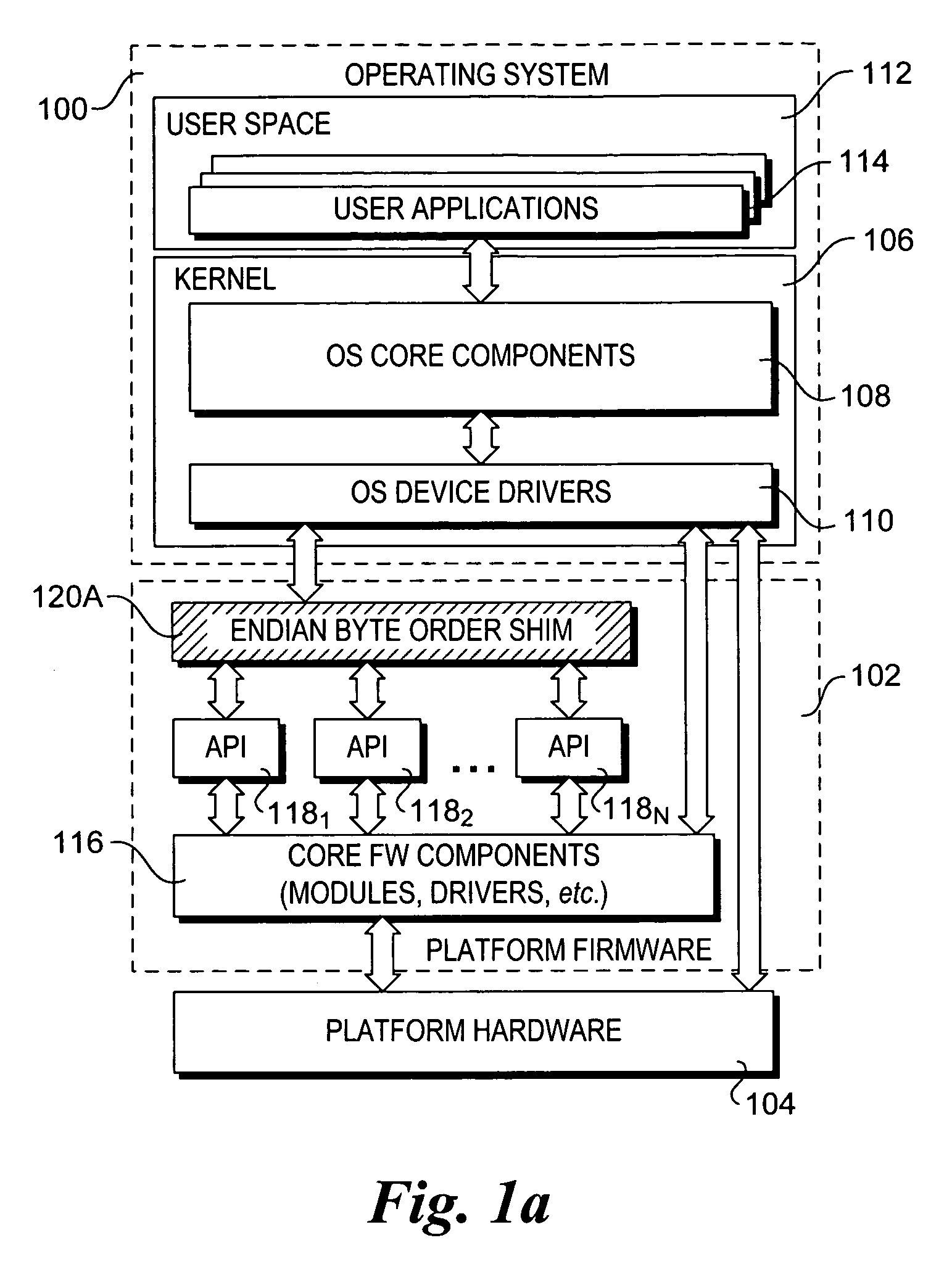

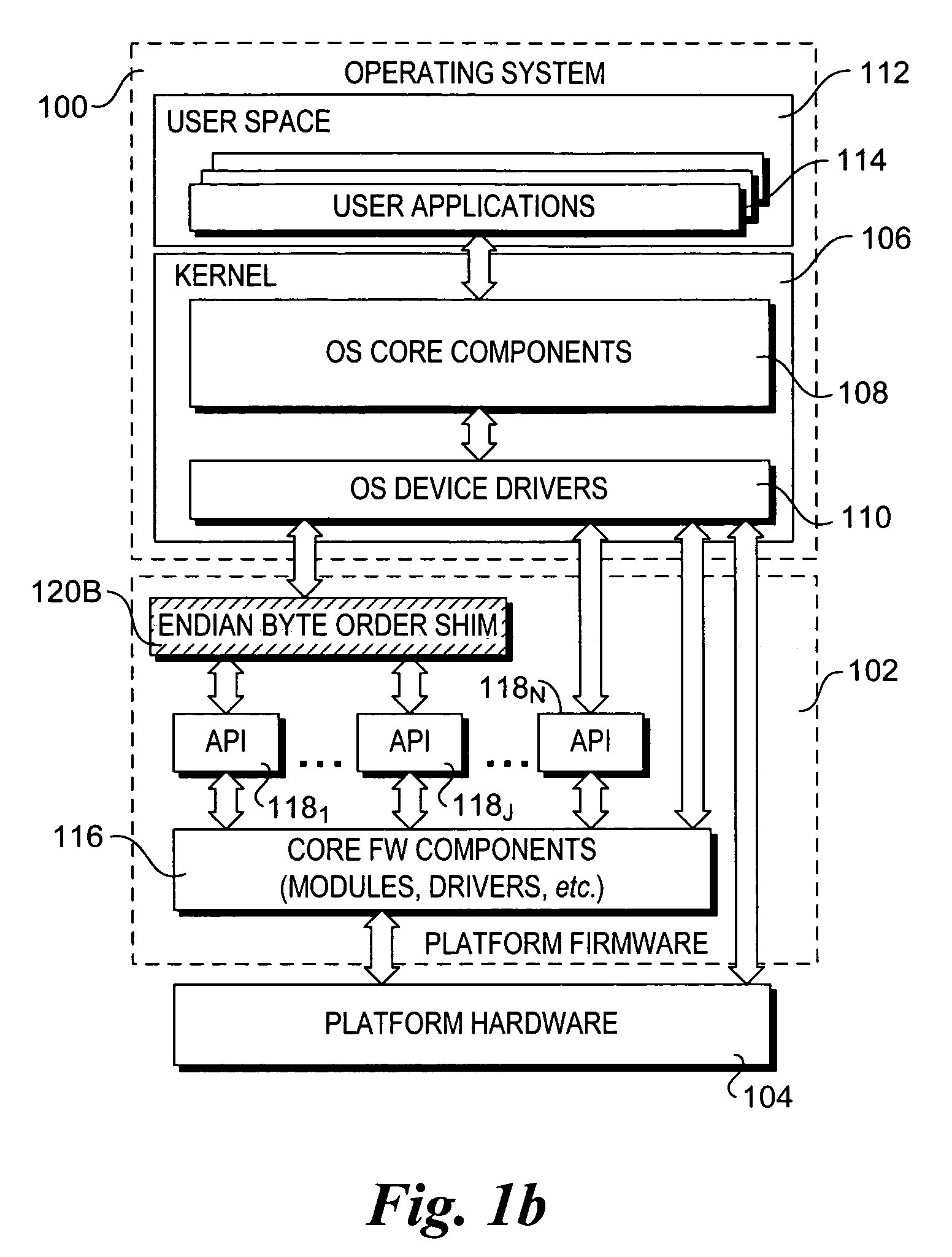

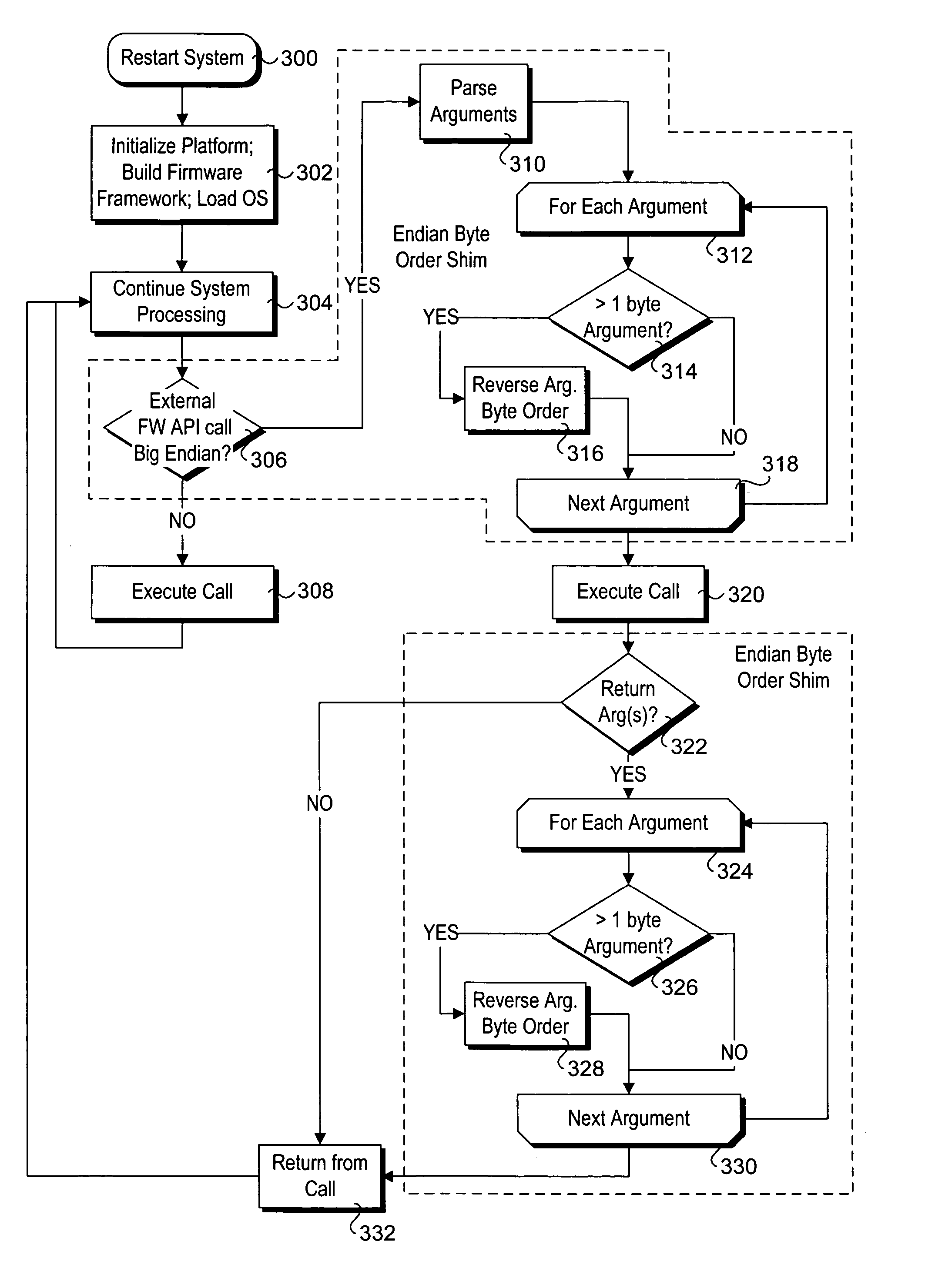

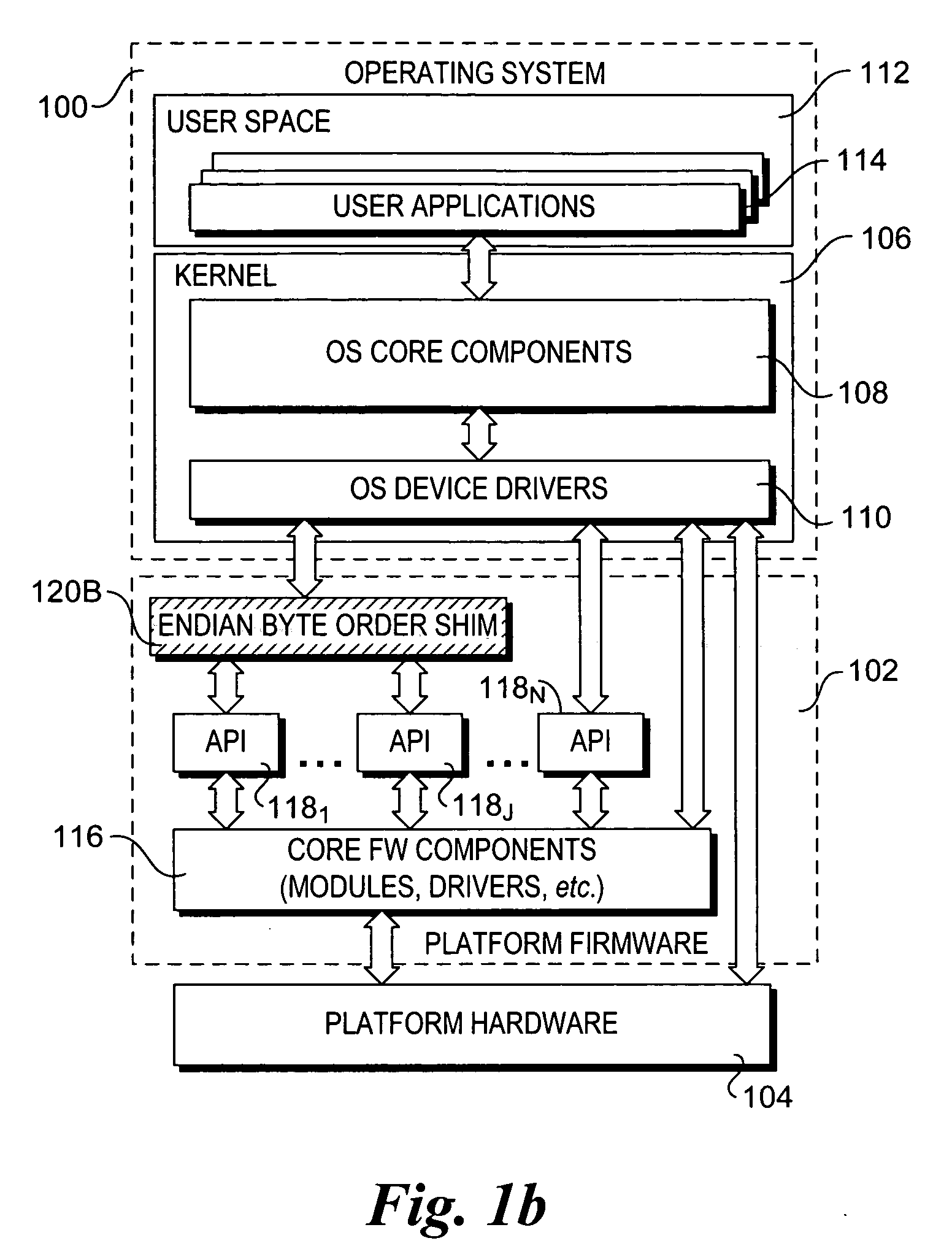

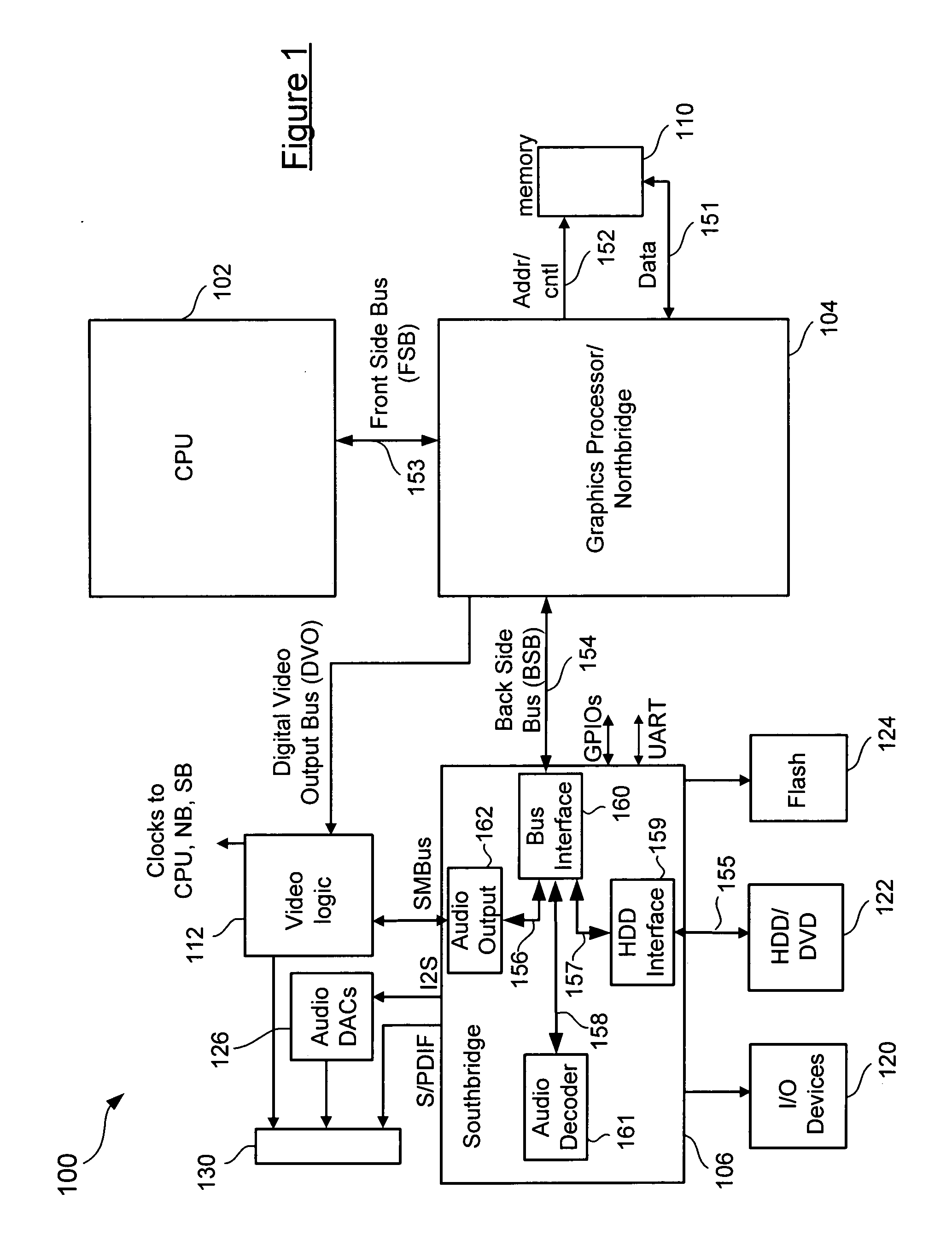

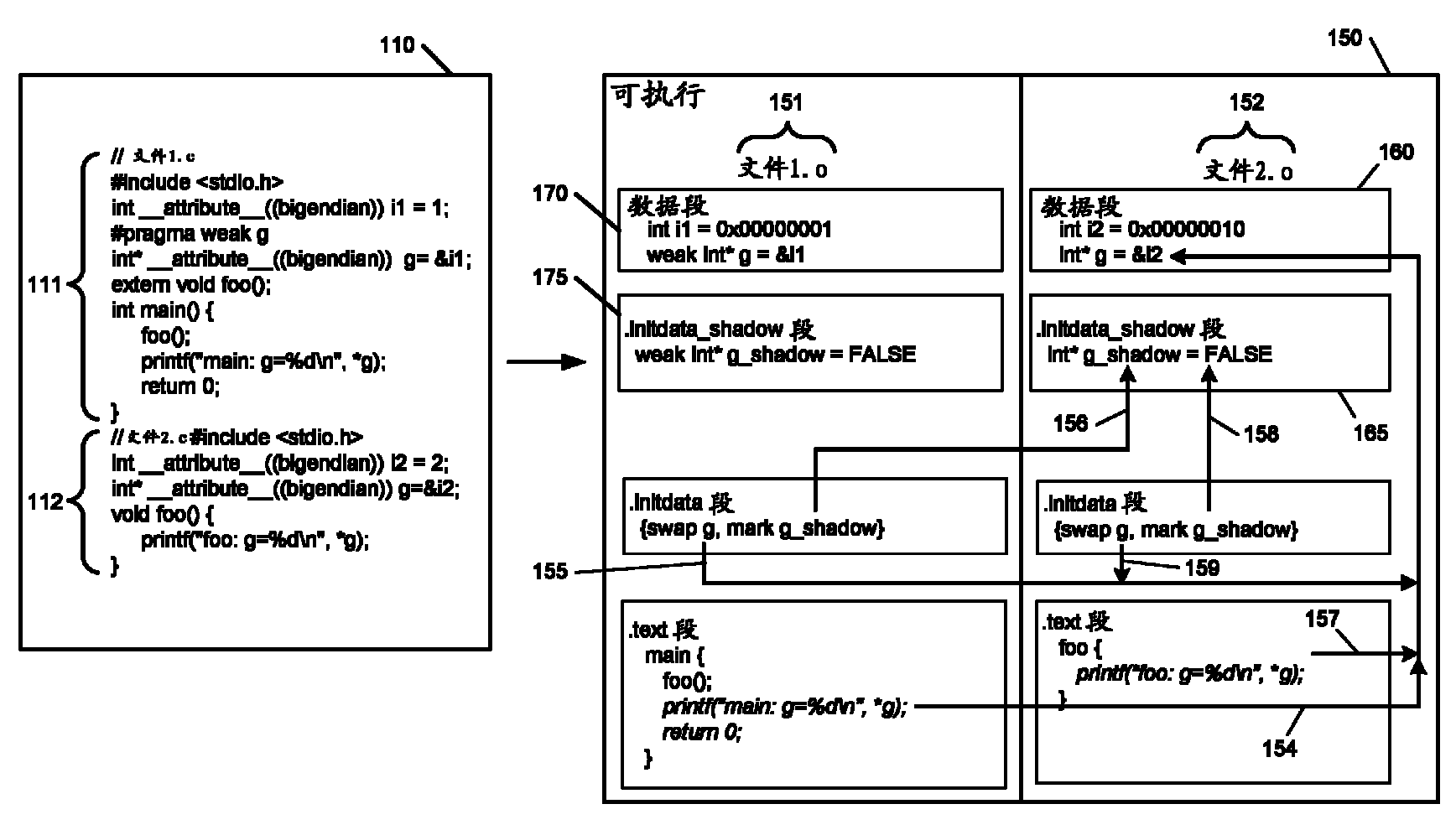

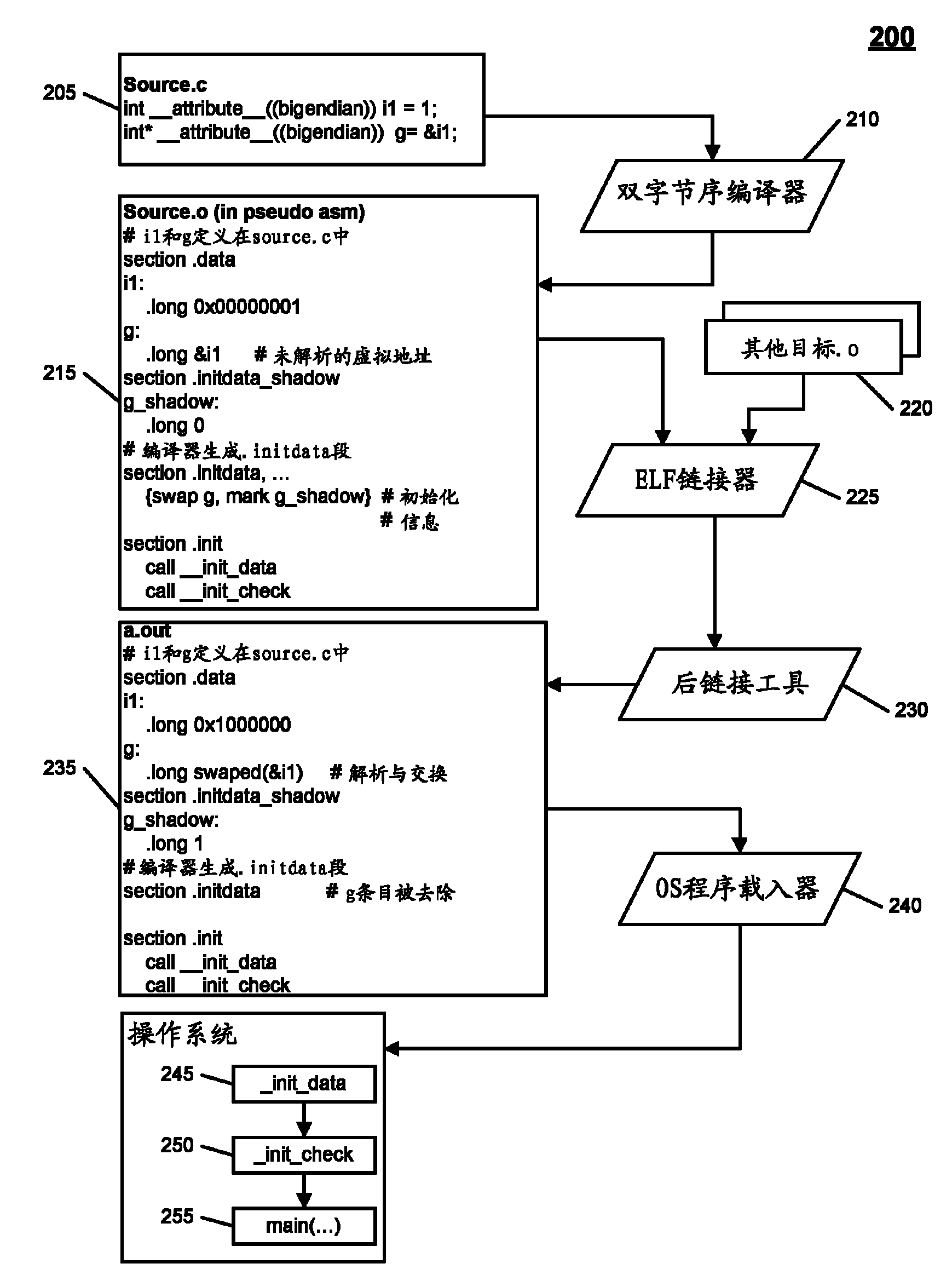

Mechanisms to support use of software running on platform hardware employing different endianness

Owner:INTEL CORP

Byte order adjustment method in binary translation

InactiveCN101763242AImprove performanceHandling data according to predetermined rulesMachine execution arrangementsMemory addressProgram segment

The invention discloses a byte order adjustment method in binary translation, belonging to the technical field of computers, which comprises the following steps: loading a source program executable image by the execution engine of a dynamic binary translation system, adjusting the byte orders of the contents of each program segment, and synchronously adjusting the number of loaded parameters, contents of the parameters and environmental variables; modifying the effective address of an intermediate command representing internal memory access so that the expression of the modified effective address accords with the semantic of the internal memory access of a source program so as to load or store correct data in an internal memory; translating the source program command into the intermediate command by a front decoder, adding the generated intermediate command to a constructed intermediate command basic block until the occurrence of direct skip or system call, finishing the construction of the current basic block, and sending the basic block to a back end for executing. The invention avoids the flitting of byte orders of internal memory data by using the method for modifying internal memory address, has high efficiency, correctness and commonality in the field of binary translation.

Owner:SHANGHAI JIAO TONG UNIV

Mechanisms to support use of software running on platform hardware employing different endianness

Methods, software / firmware, and apparatus to support use of software running on platform hardware employing different endianness. In one embodiment, an endian byte order shim is implemented in a firmware stack to facilitate the use of software running on a computer platform having a processor employing an endianness that is different from the endianness native to the software. In response to software calls into the firmware, the endian byte order shim converts the endian byte order of the call arguments, as necessary, and passes the converted arguments to the firmware. Similarly, return arguments generated via the firmware (and / or platform hardware) are converted back to the endian byte order native to the software prior to being returned to the software.

Owner:INTEL CORP

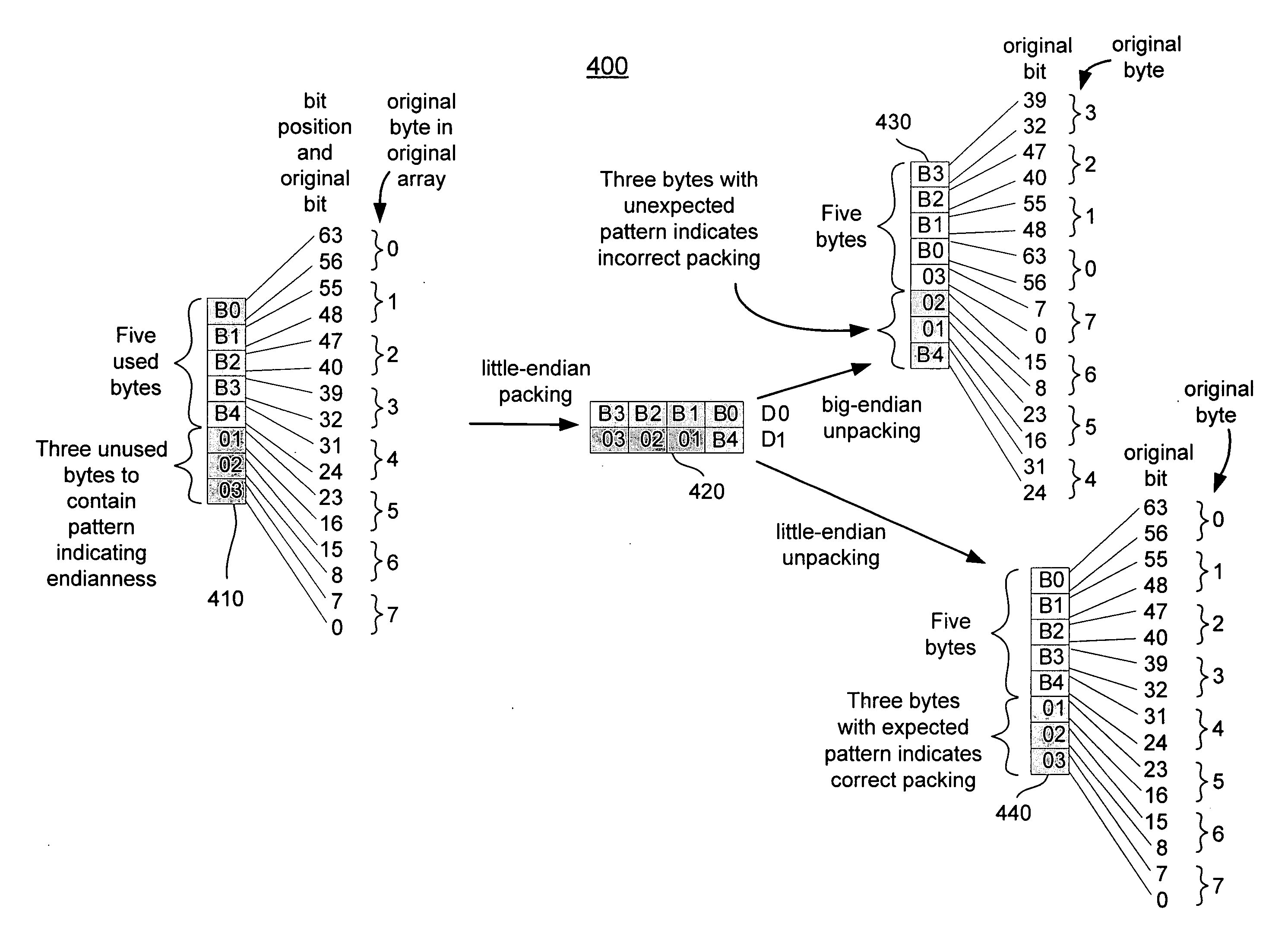

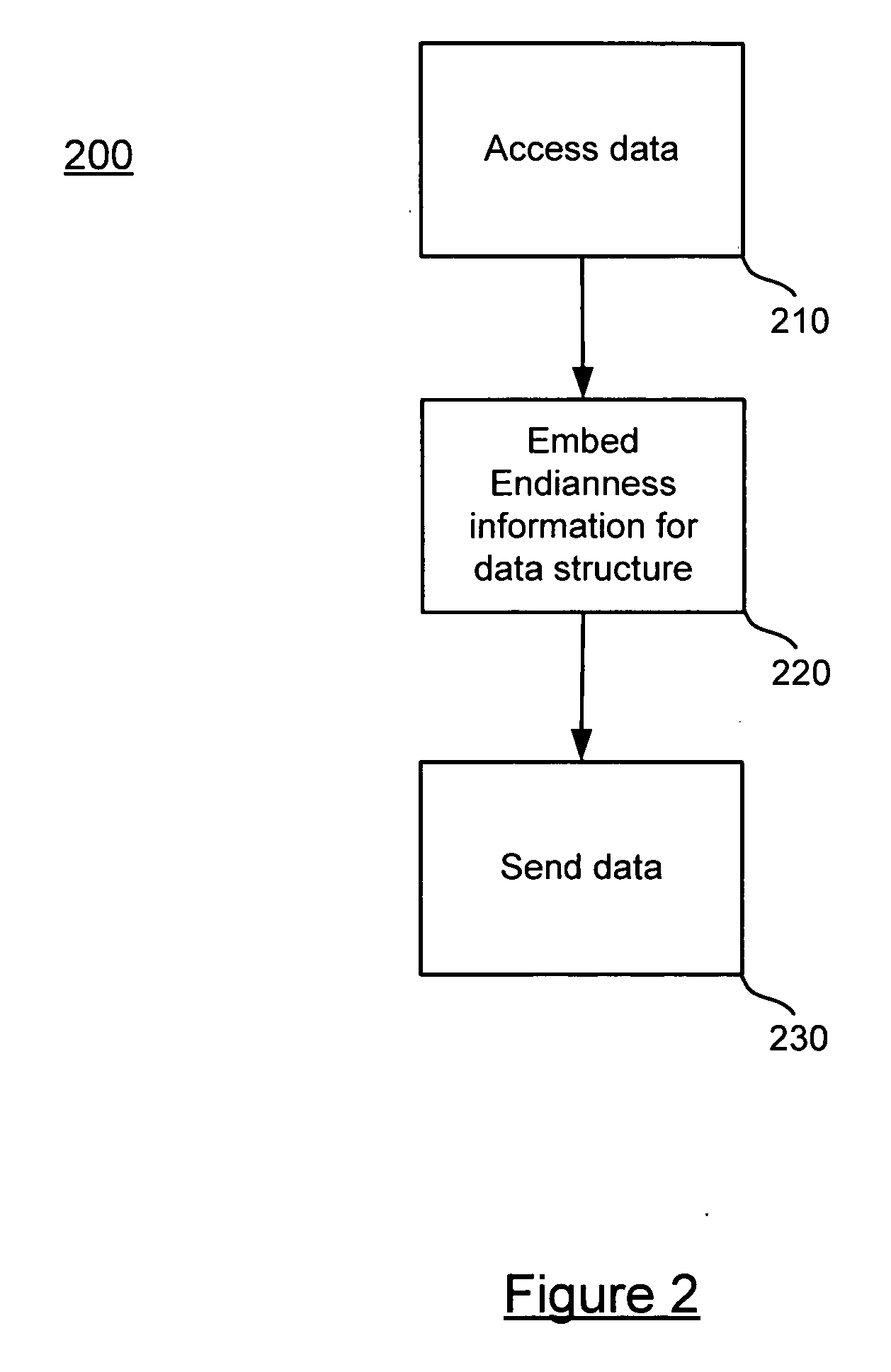

Endianness independent data structures

Embedding endianness information within data and sending and receiving data with the embedded endianness information. Data may be contained in a data structure. To embed endianness information in a data structure, unused bits in a data structure are identified. A number of the unused bits are then selected based on the possible unpacking combinations of the data structure. The endian bit values are set to a pattern to indicate the endianness of the data structure. Data that has been packed by a transmitting module can be unpacked by a receiving module based on the detected endian bits. An algorithm may be used to determine which unused bits to select as the endian bits.

Owner:MICROSOFT TECH LICENSING LLC

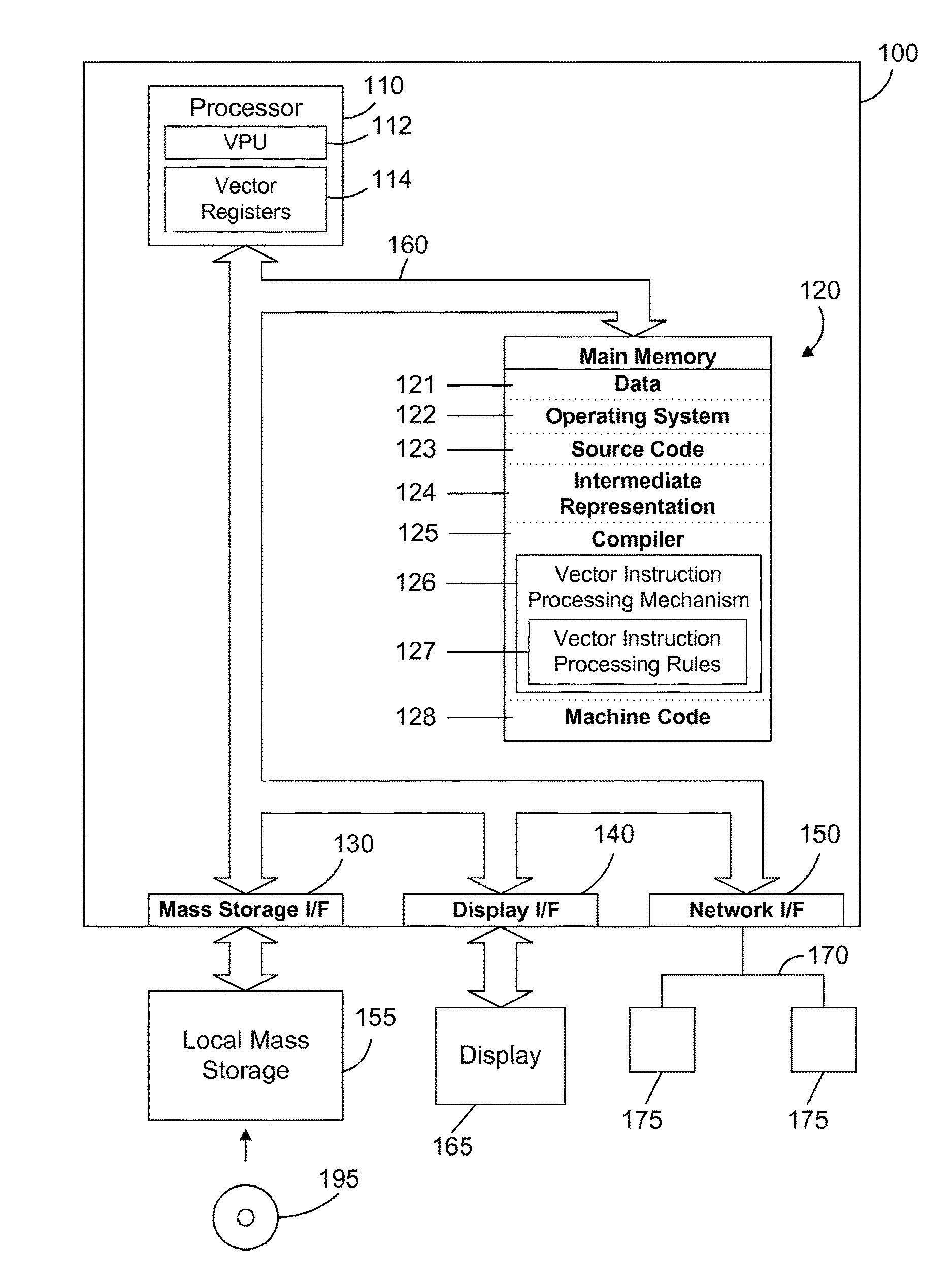

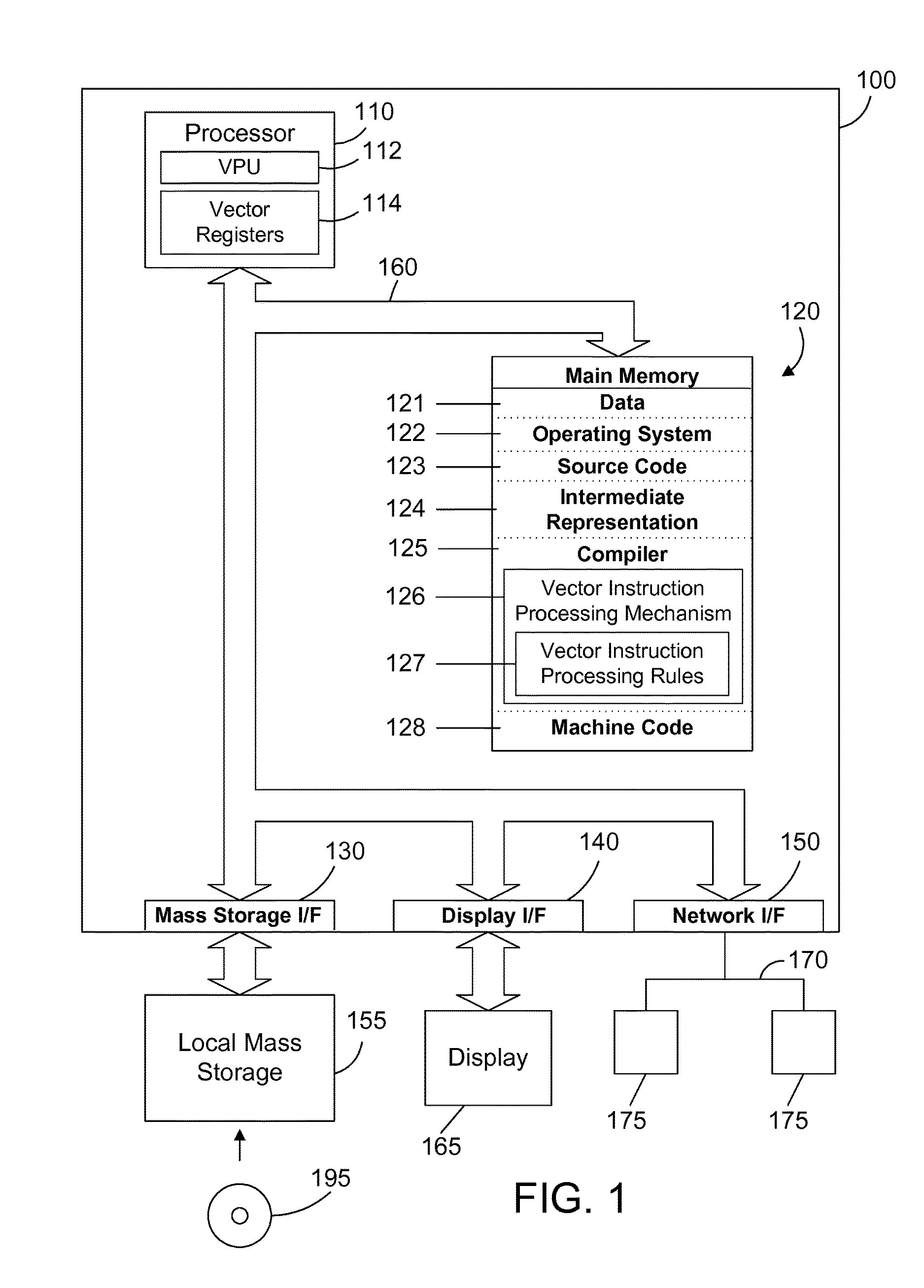

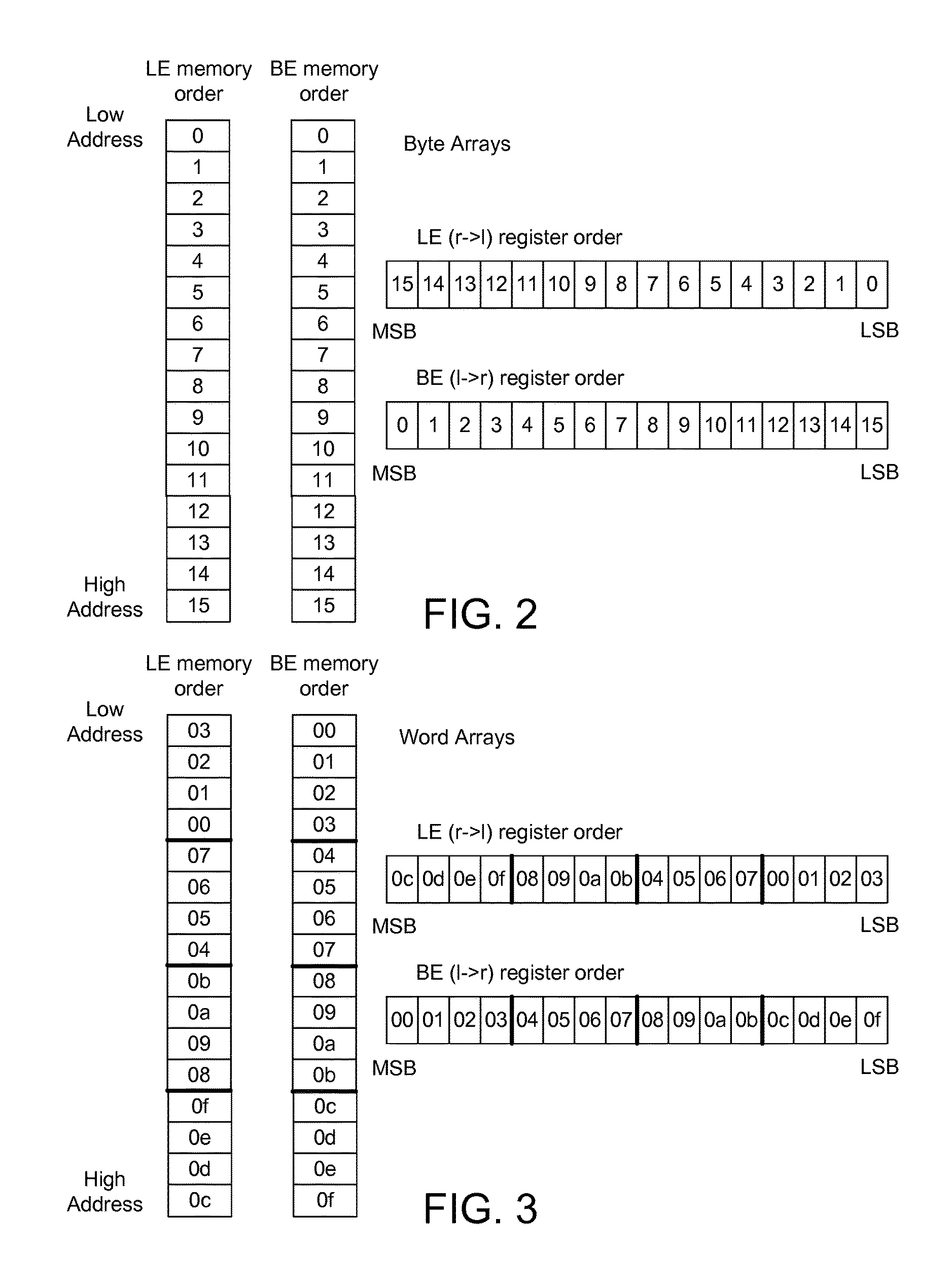

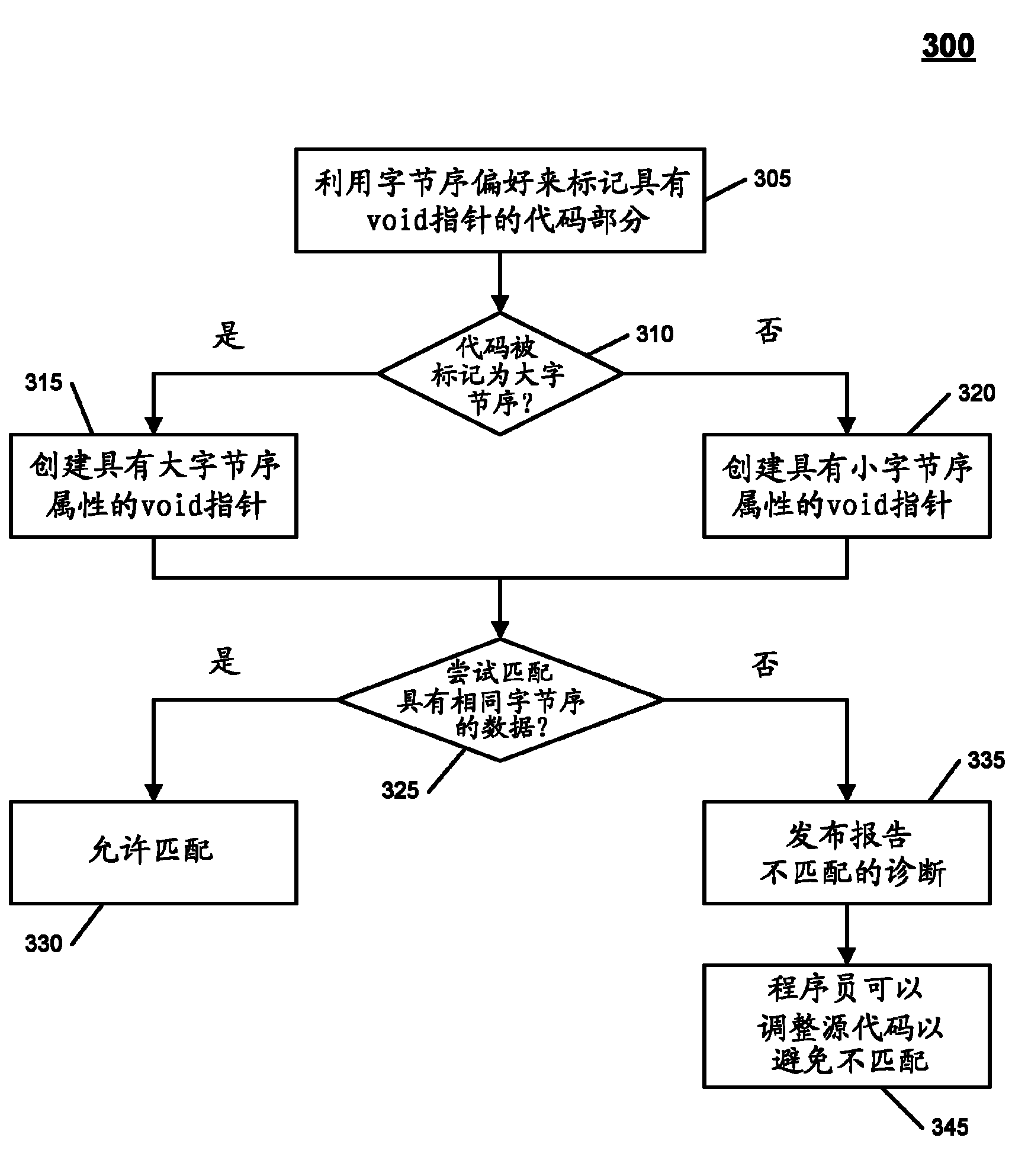

Compiler method for generating instructions for vector operations on a multi-endian processor

A compiler includes a vector instruction processing mechanism that generates instructions for vector instructions in a way that assures correct operation in a bi-endian environment, wherein the processor architecture contains instructions with an inherent endian bias. The compiler uses a code generation endian preference that is specified by the user, and that determines a natural element order. When the compiler processes a computer program, it generates instructions for vector operations by determining whether the vector instruction has an endian bias that matches the specified endian preference (i.e., the inherent element order of the vector instruction matches the natural element order). When the vector instruction has no endian bias, or when the endian bias of the vector instruction matches the specified endian preference, the compiler generates one or more instructions for the vector instruction as it normally does. When the endian bias of the vector instruction does not match the specified endian preference, the compiler generates instructions to fix the mismatch.

Owner:IBM CORP

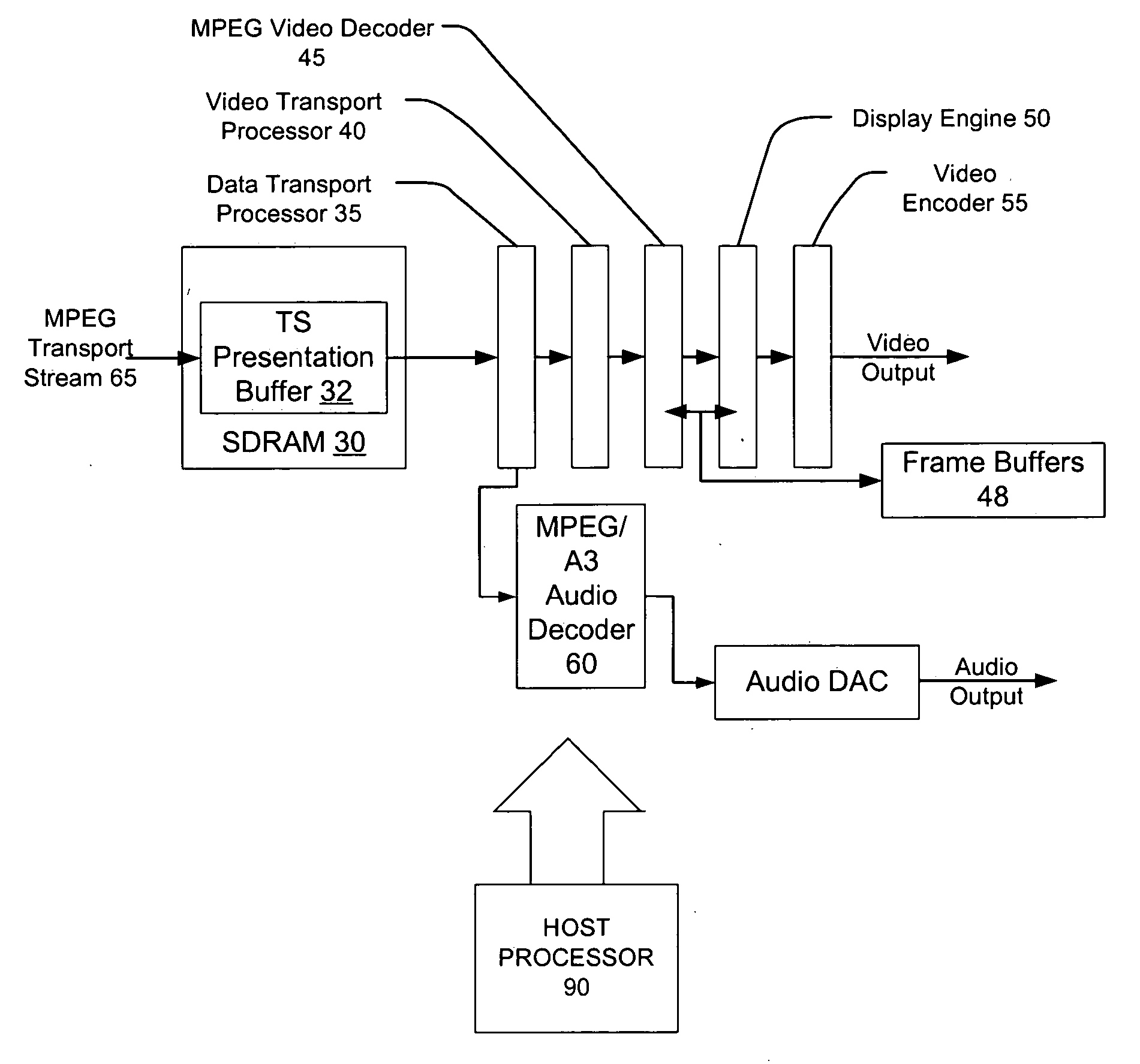

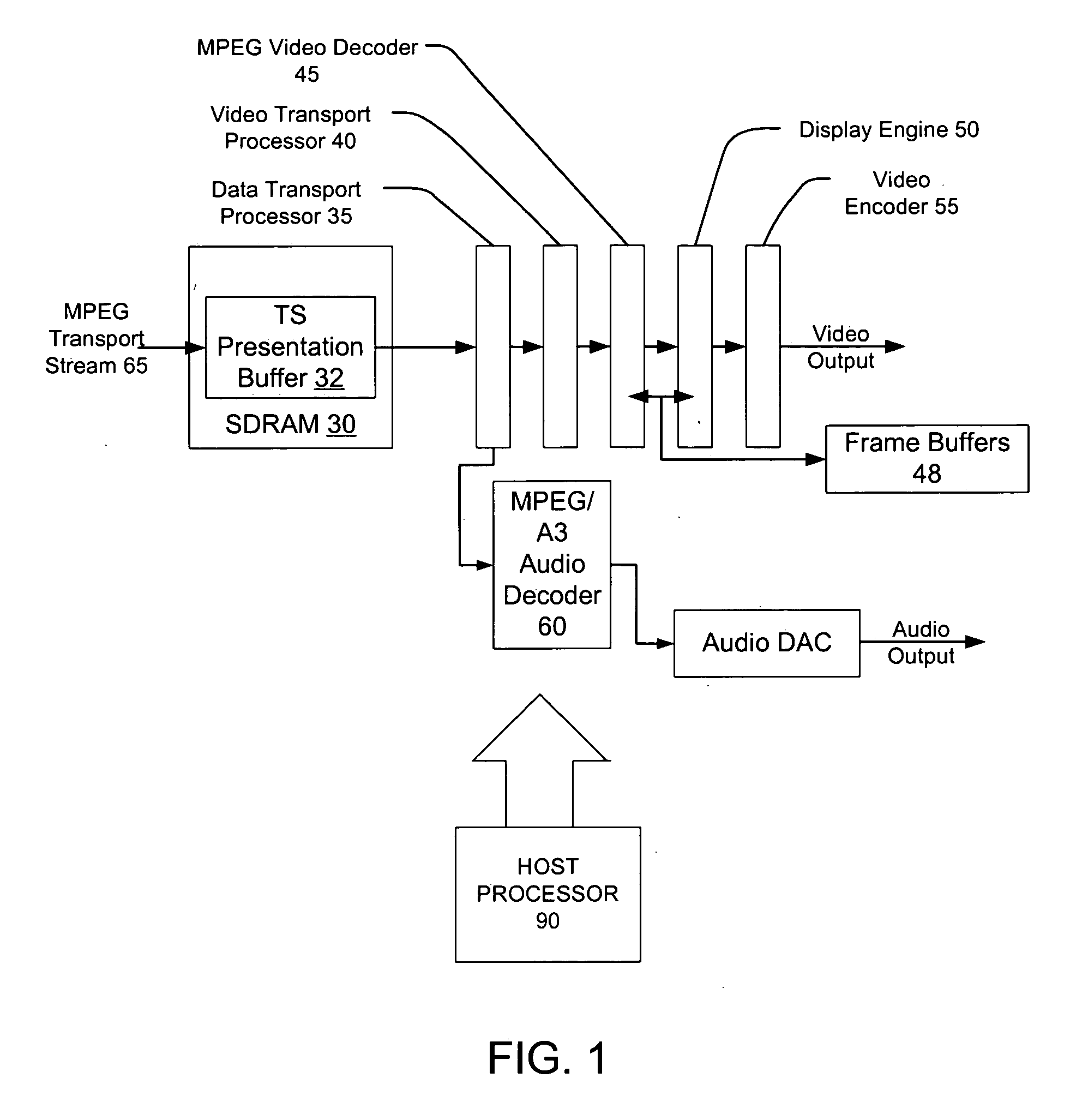

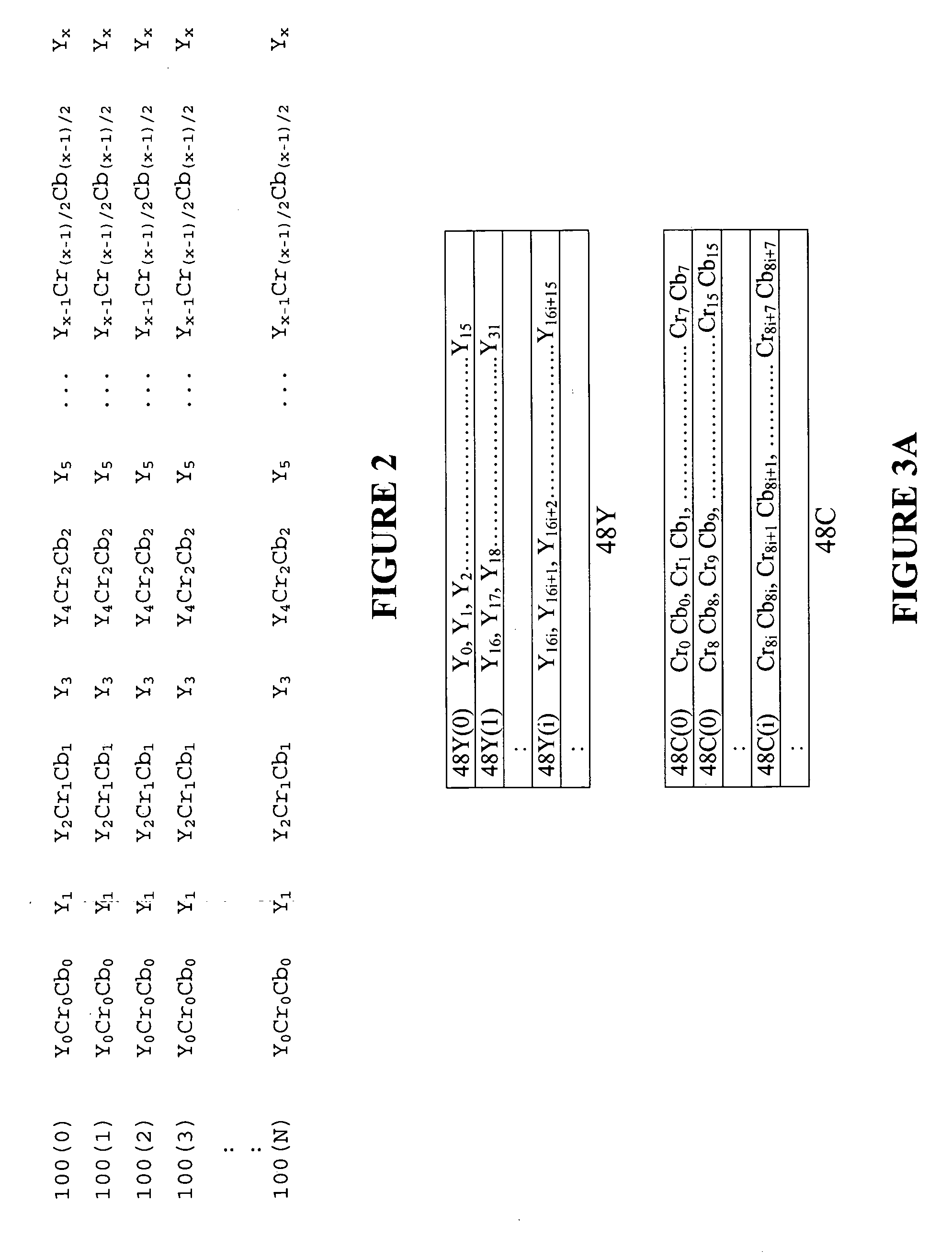

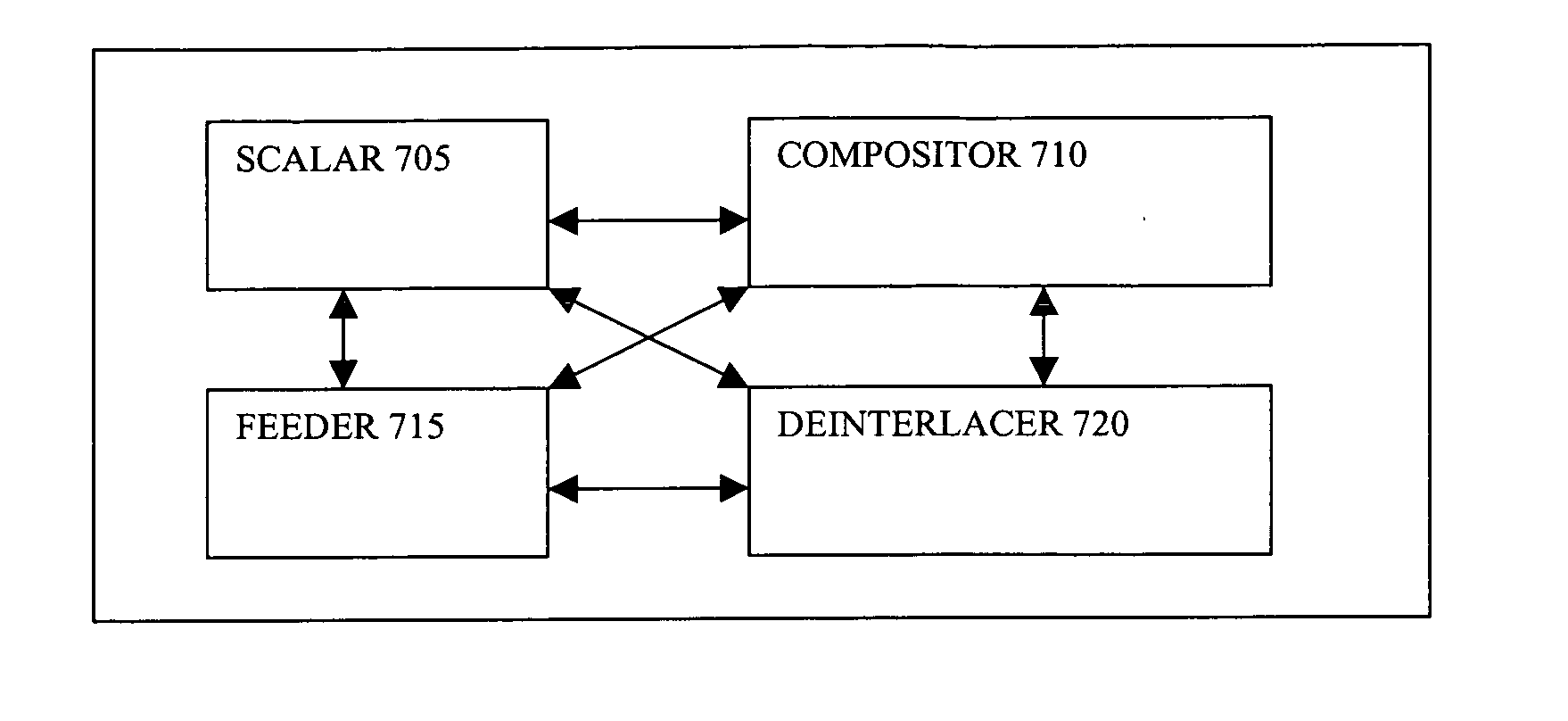

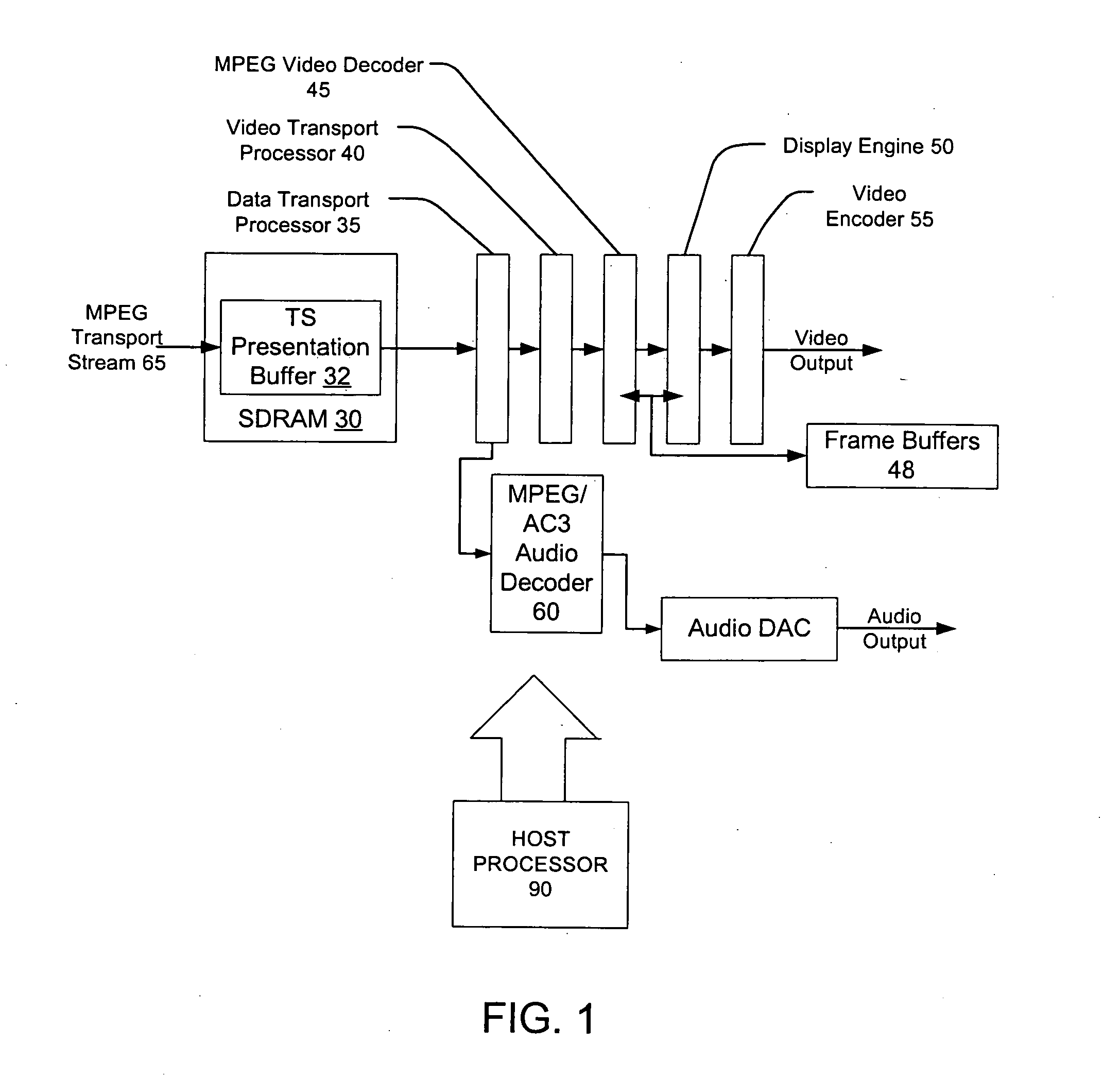

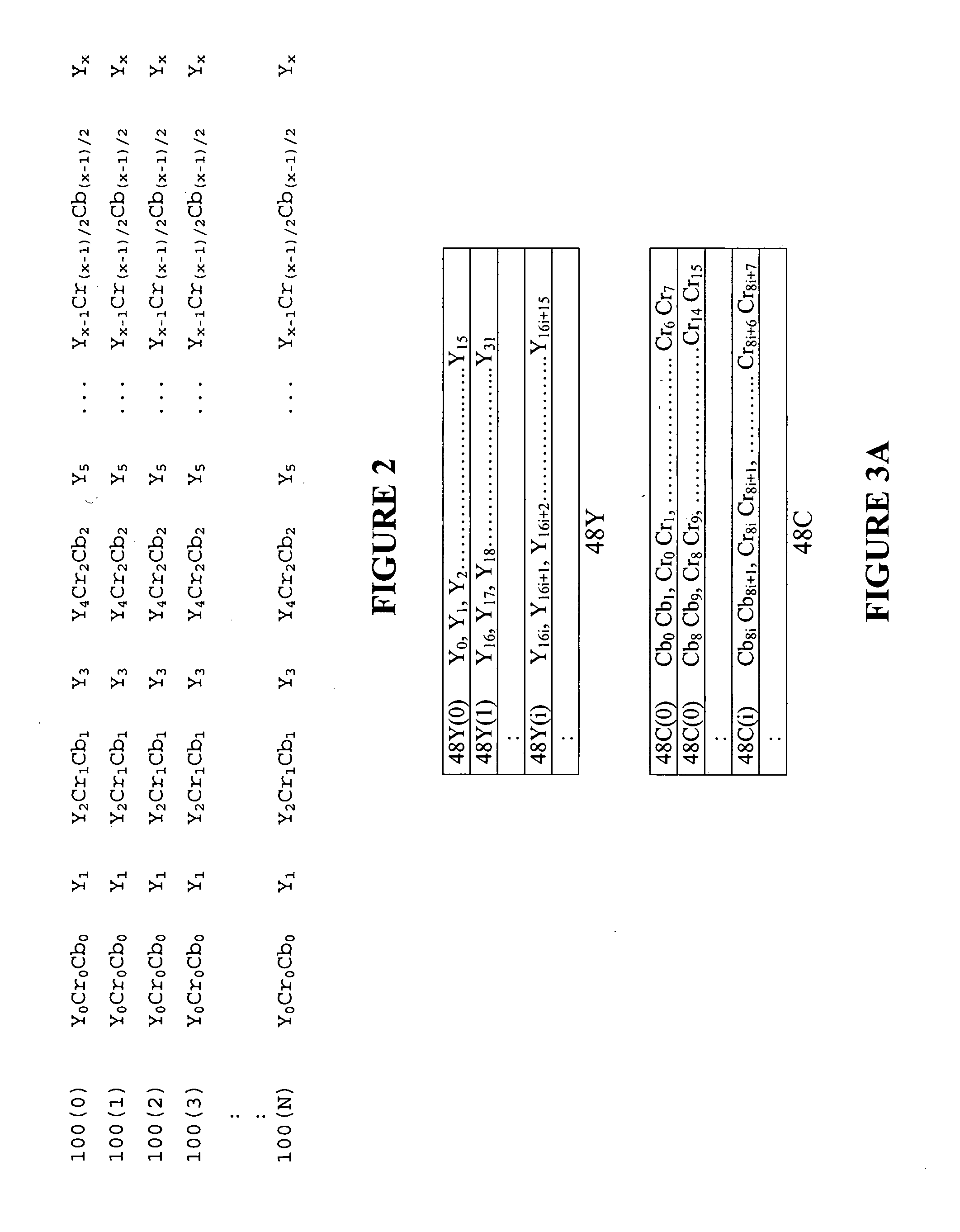

Pixel reordering and selection logic

InactiveUS20050036696A1Picture reproducers using cathode ray tubesPicture reproducers with optical-mechanical scanningEndiannessComputer graphics (images)

Presented herein are systems and methods for pixel reordering and selection. A decoded frame is stored in a frame buffer with a particular pixel order and byte order. A pixel feeder fetches portions of the decoded frame and stores portions of the frame in a double buffer with the same pixel order and byte order. An endian swizzle converts the byte ordering to a predetermined format, as needed. Reordering logic changes the pixel order to a predetermined order. Selection logic selects luma and chroma pixels from fetched pixels and provides the luma pixels to a luma pixel register, chroma Cr pixels to a chroma Cr pixel register, and chroma Cb pixels to a chroma Cb pixel register.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

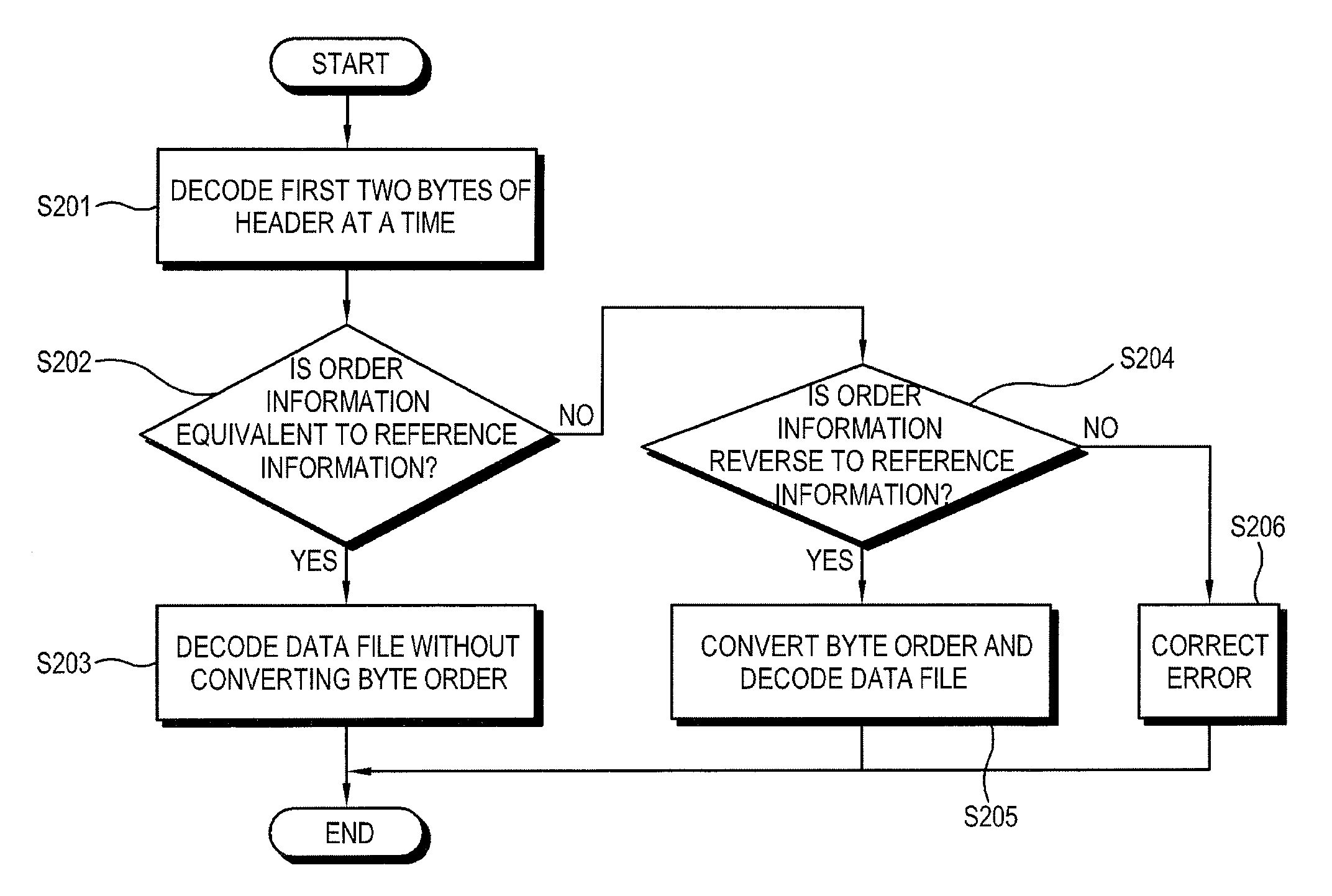

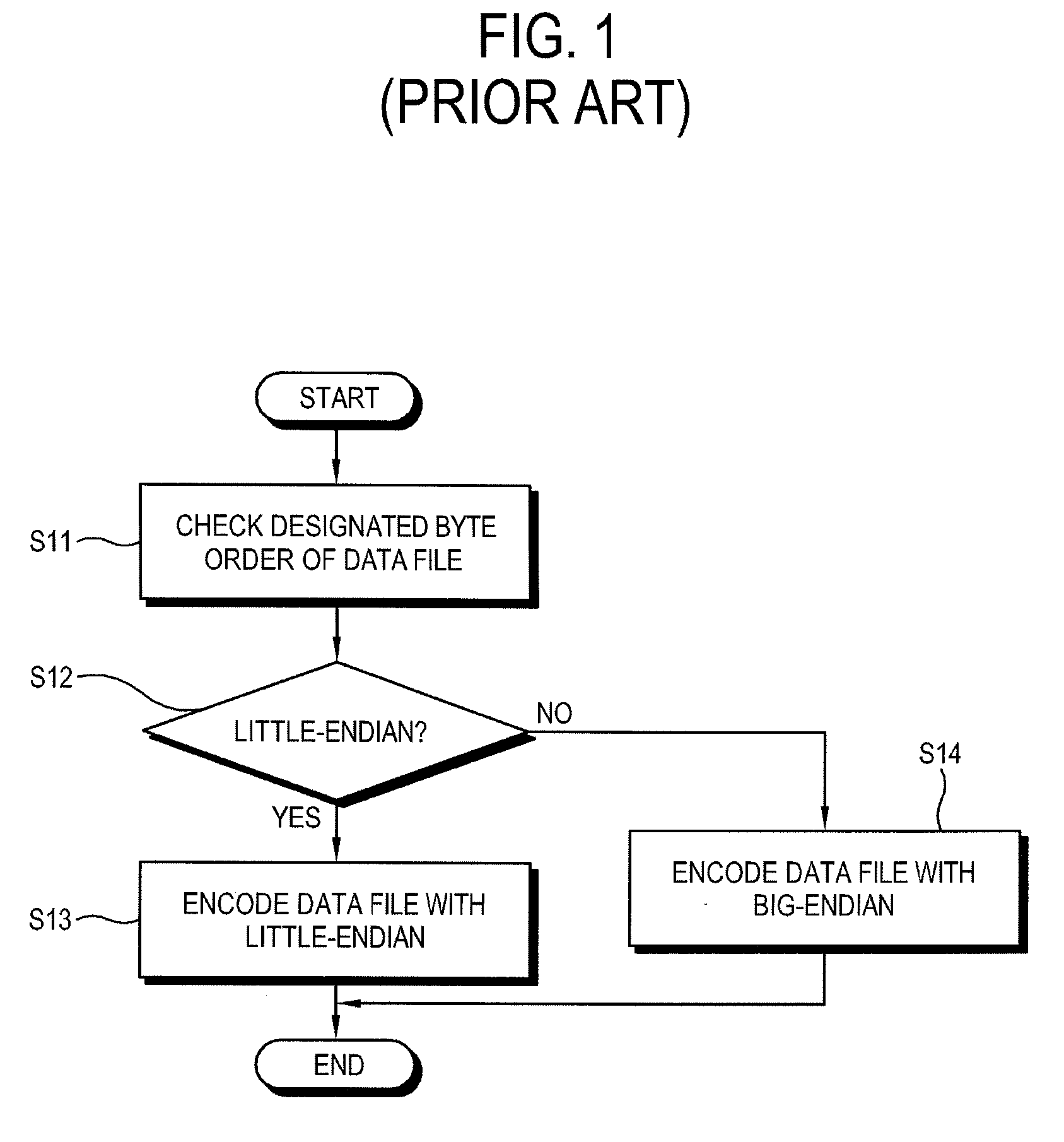

Data processing apparatus and data processing method

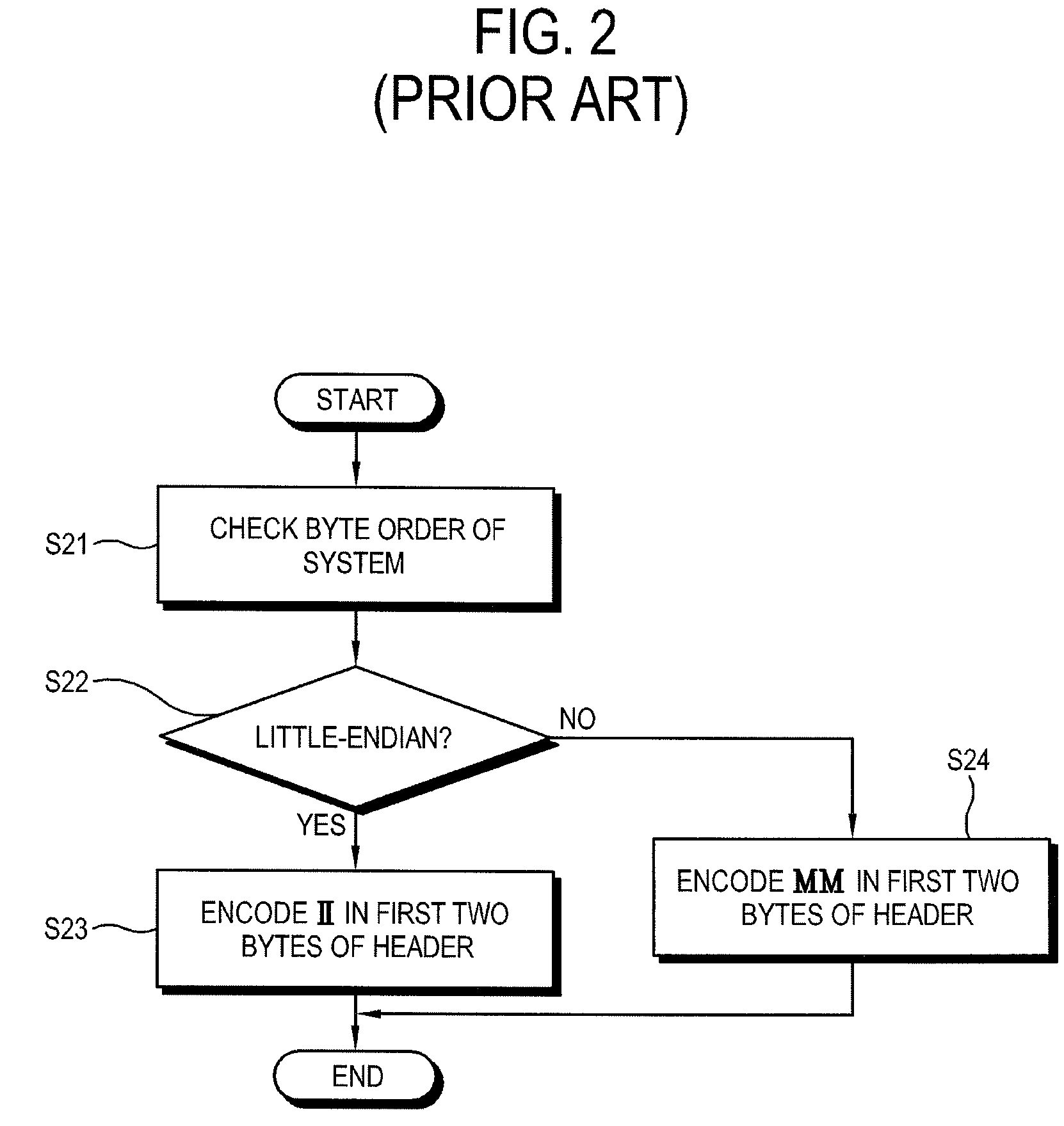

ActiveUS20090006485A1Efficient processingEfficiently processes byte orderCharacter and pattern recognitionComparison of digital valuesEndiannessData file

A data processing apparatus and a data processing method include reading order information included in a data file according to one of a pair of byte orders, comparing the read order information with preset reference information, and decoding the data file if the order information is equal to the reference information.

Owner:HEWLETT PACKARD DEV CO LP

Data processing engine

A data processing engine is provided, which includes an endian register, an endian control device, and a byte swapper. The endian register stores a plurality of endian control bits. Each endian control bit indicates the default data endianness of a type of address space accessible to the data processing engine. Each endian control bit is in either a big-endian state or a little-endian state. The endian control device is coupled to the endian register. The endian control device provides an endian signal according to the endian control bits and the instruction executed by the data processing engine. The endian signal is in either the big-endian state or the little-endian state. The byte swapper is coupled to the endian control device. The byte swapper transmits data and changes the byte order of the data when the byte order of the data is inconsistent with the state of the endian signal.

Owner:ANDES TECH

Data pack preprocessing method and bus interface and data processing unit thereof

InactiveCN1148667CHybrid switching systemsElectric digital data processingMain processing unitEndianness

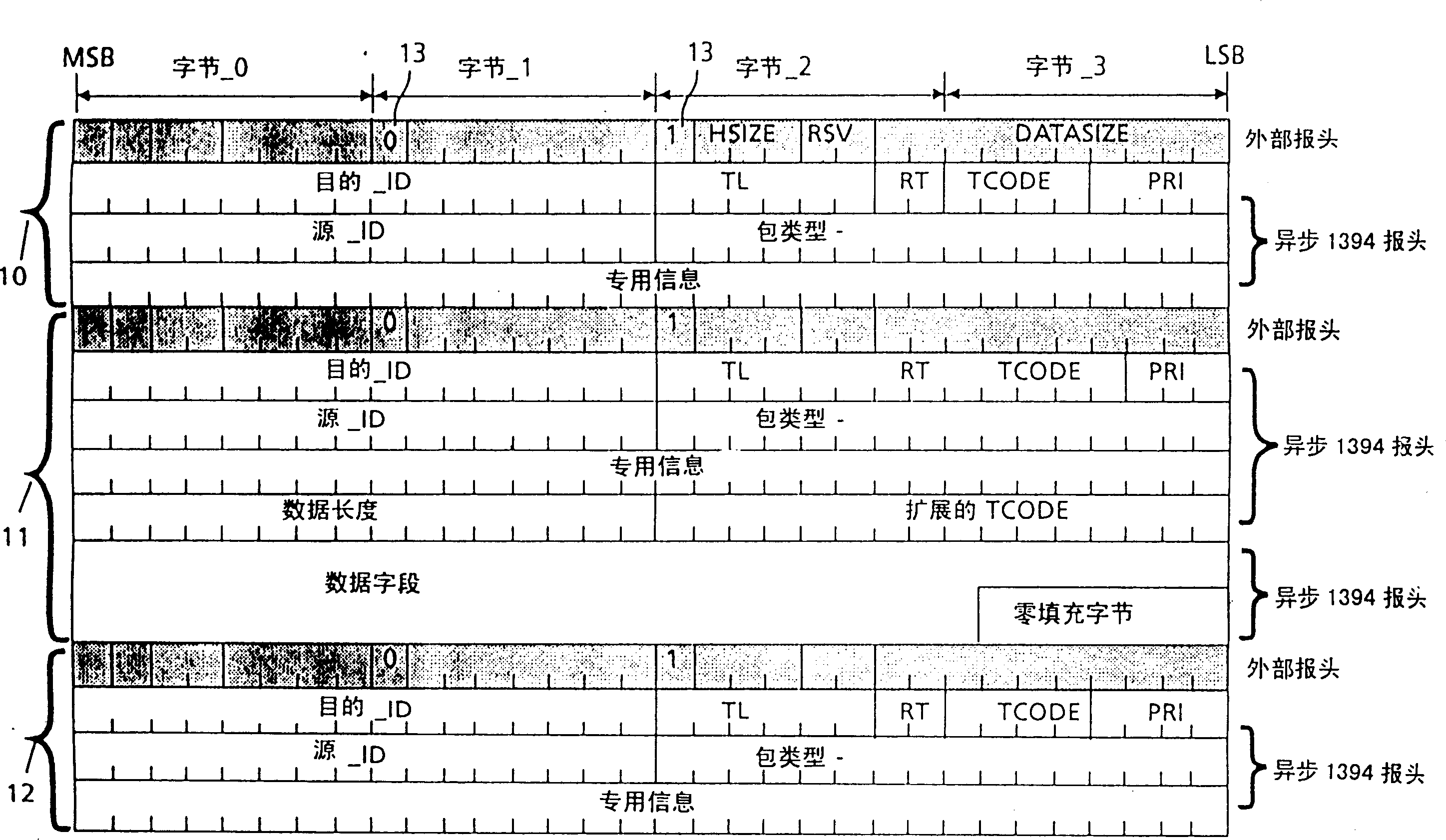

The IEEE1394 bus communication protocol has three layers: physical layer, link layer, and transaction layer. A link layer IC implements the interface to an external application and prepares data for sending on the bus, or interprets incoming data packets from the IEEE1394 bus. A physical layer IC implements the direct electrical connection to the bus and controls many functions including arbitration for sending data on the bus. A problem exists due to the fact that the header data of the IEEE1394 asynchronous data packets consists of 32 bit words which have to be interpreted as 32 bit words in the connected application data processing unit (30). The IEEE1394 bus interface unit (20) is defined to be of big endian type. In a little endian type application data processor (30) the data word order can only be correctly interpreted after a byte order change. According to the invention the byte order change is performed in the data link layer unit (21) automatically with hardware circuitry for asynchronous data packets.

Owner:DEUTSCHE THOMSON-BRANDT GMBH

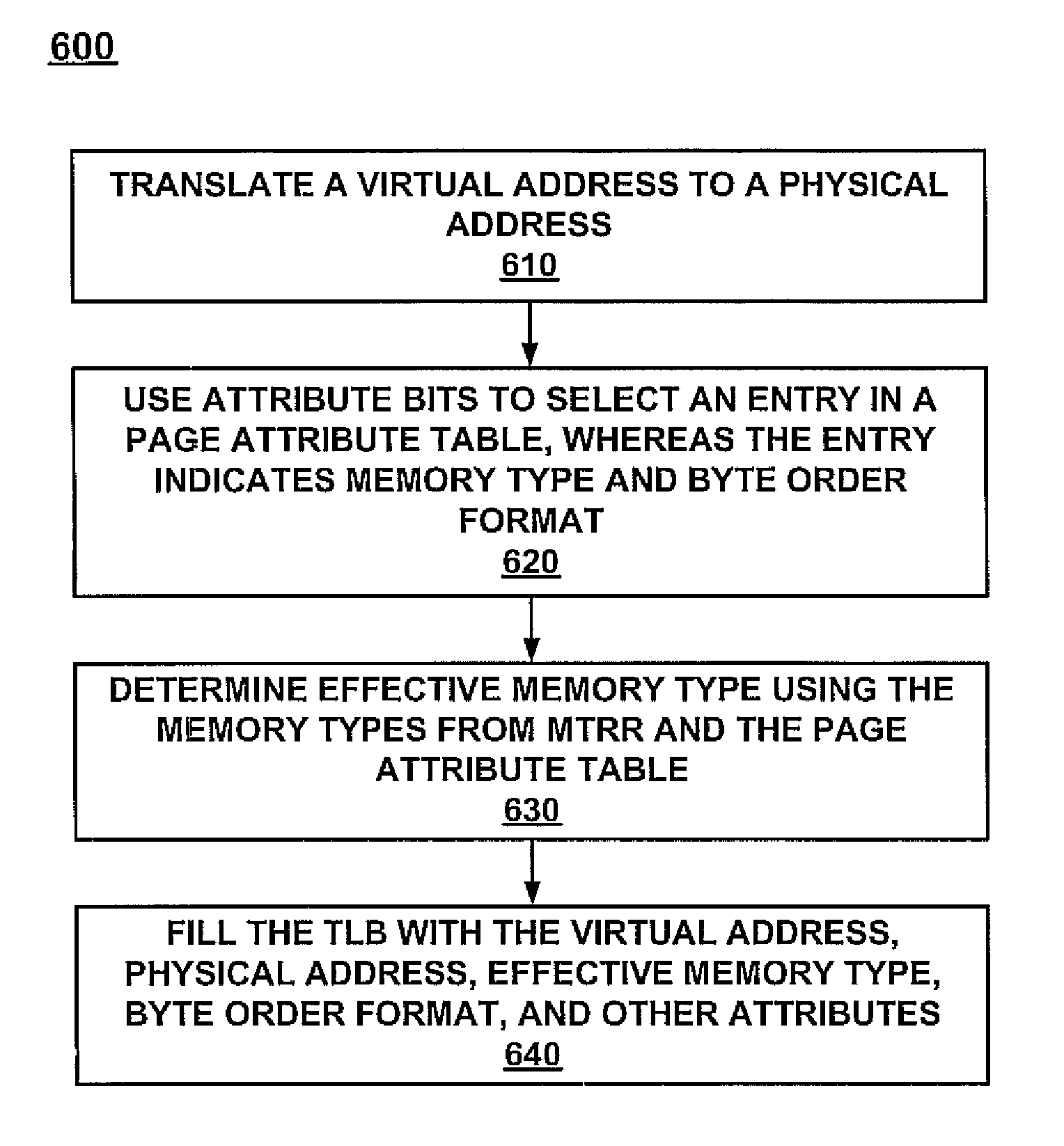

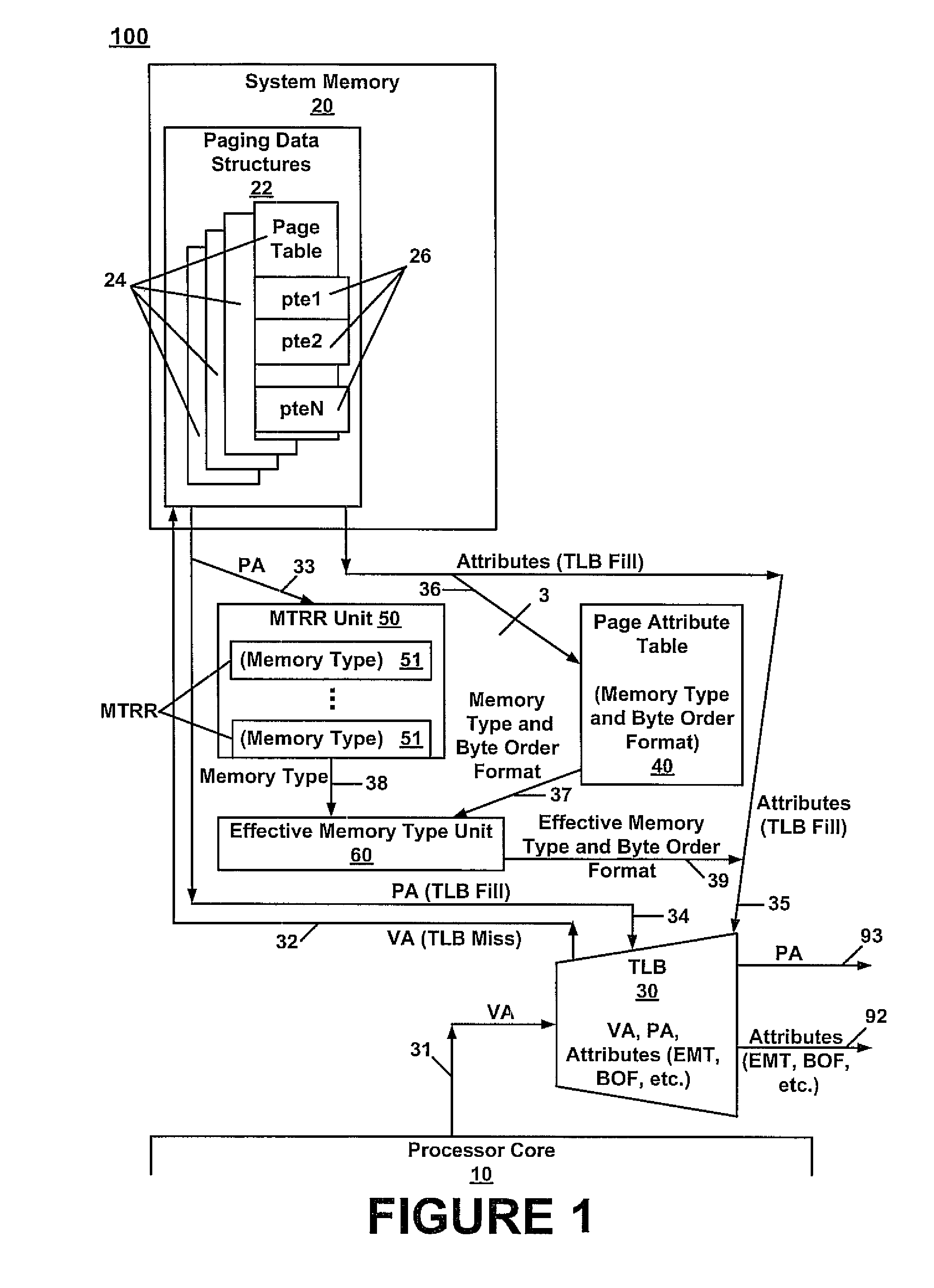

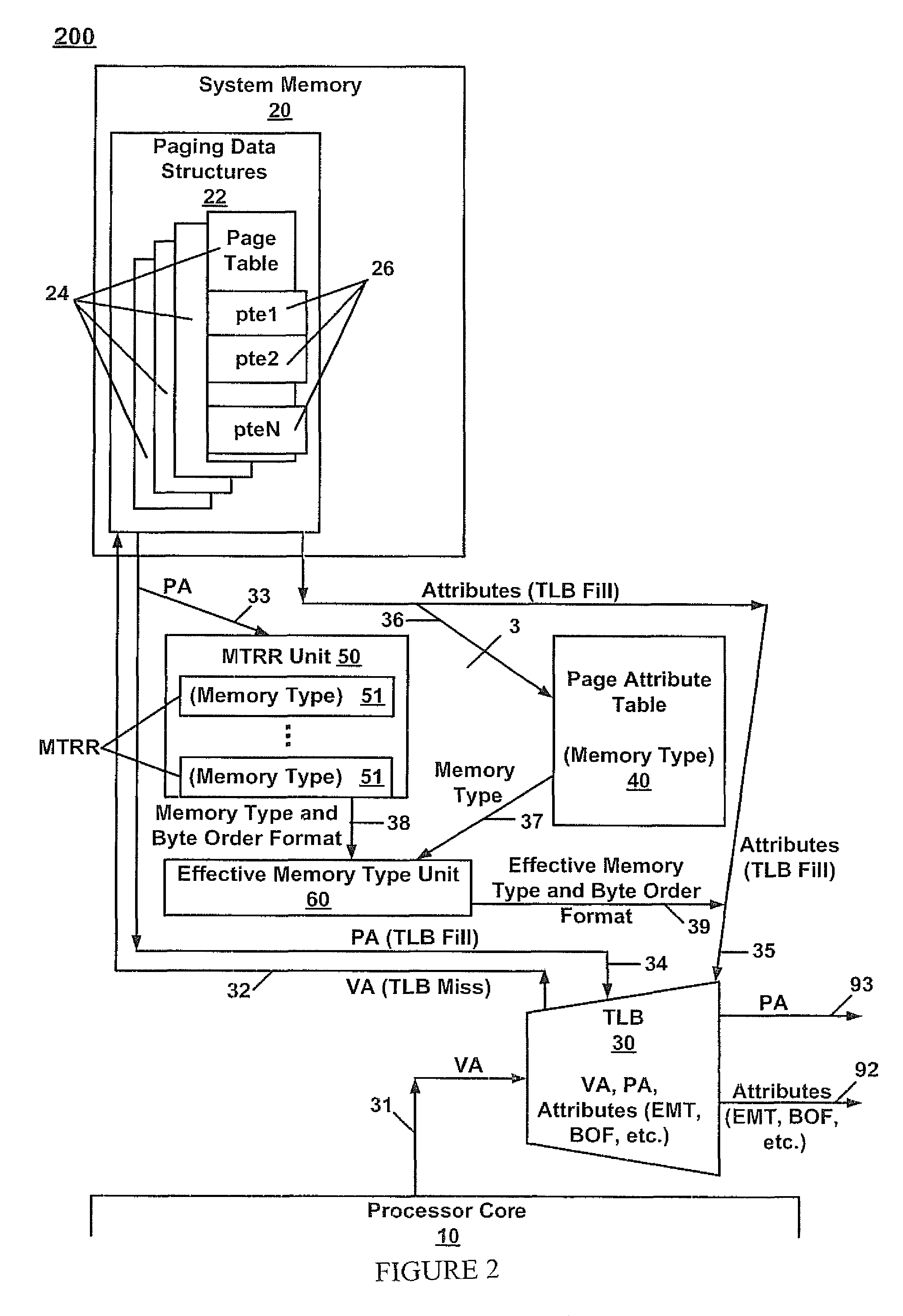

Supporting multiple byte order formats in a computer system

ActiveUS8156308B1Memory systemsMicro-instruction address formationMemory type range registerEndianness

Owner:INTELLECTUAL VENTURES HOLDING 81 LLC

Endian conversion tool

InactiveCN102103481AByte swap suppressionCode compilationMachine execution arrangementsEndiannessSource code

In one embodiment of the invention code (e.g., compiler, tool) may generate information so a first code portion, which includes a pointer value in a first endian format (e.g., big endian), can be properly initialized and executed on a platform having a second endian format (e.g., little endian). Also, various embodiments of the invention may identify problematic regions of code (e.g., source code) where a particular byte order is cast away through void pointers.

Owner:INTEL CORP

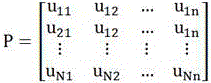

Encryption method for information access in cloud computing

InactiveCN106611127AAddressing deficiencies in security issuesGuaranteed confidentialityDigital data protectionTransmissionInformation accessOriginal data

The invention provides a method for solving an unknown positive integer on the basis of a congruence theory of the positive integer, and builds an encryption and decryption method for information storage and extraction in a distributed cache. The method comprises the steps of firstly converting data D into a matrix with N rows and n columns according to a byte order, defining a pairwise coprime integer set and constructing a unary linear congruence equation set by original data and the defined integer set according to the congruence theory; solving a solution, transforming the solution into a matrix and converting the matrix into data columns according to the scheme of constructing the matrix according to the original data, namely obtaining a ciphertext; and constructing a matrix by using the ciphertext during decoding, reversely solving congruence equations to obtain the matrix of the original data and reconstructing original data columns.

Owner:SICHUAN YONGLIAN INFORMATION TECH CO LTD

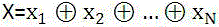

Transmitting system and method of processing digital broadcast signal in transmitting system, receiving system and method of receiving digital broadcast signal in receiving system

InactiveUS8488716B2Improve reception performanceSmooth communicationAmplitude-modulated carrier systemsForward error control useEndiannessExclusive or

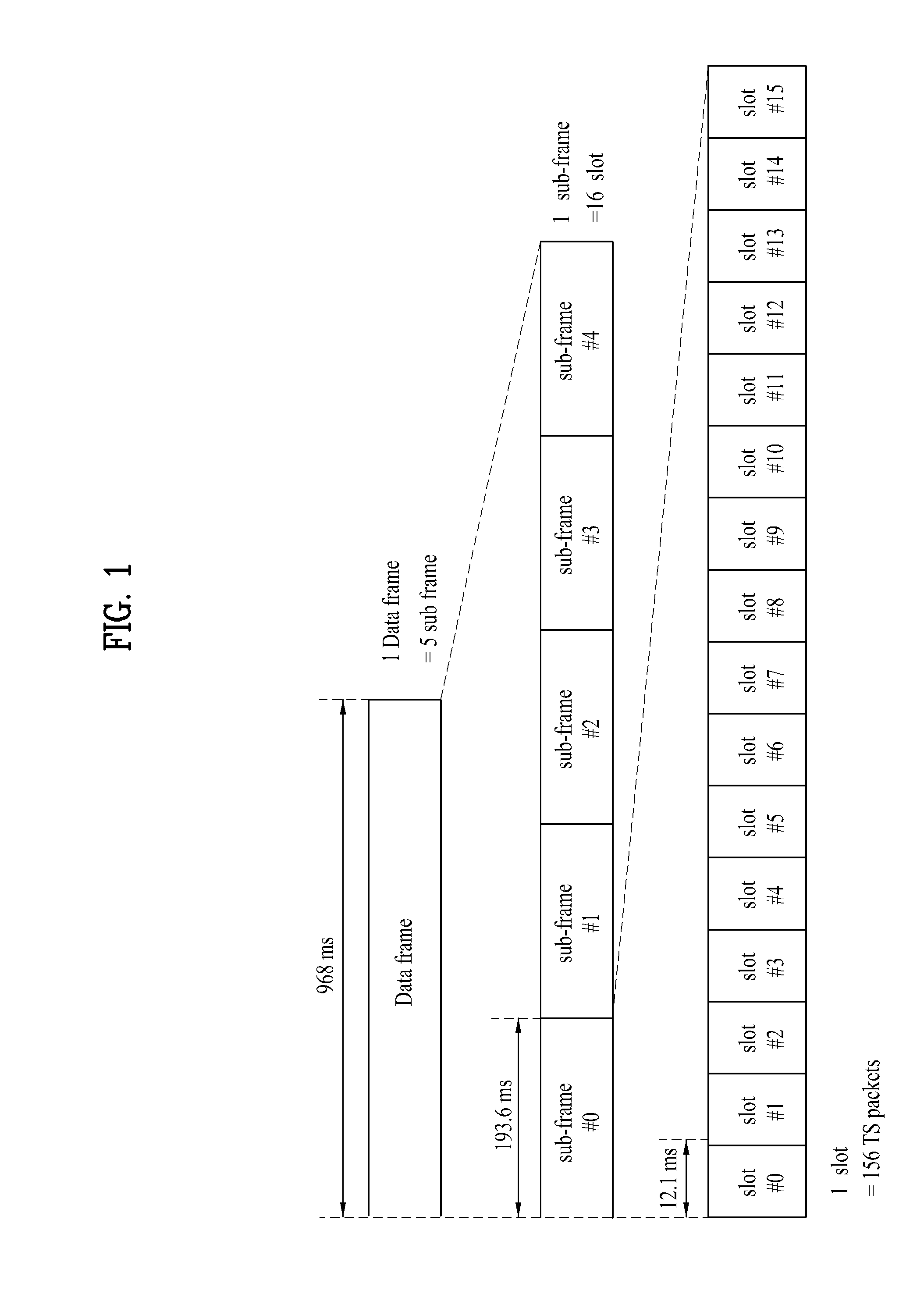

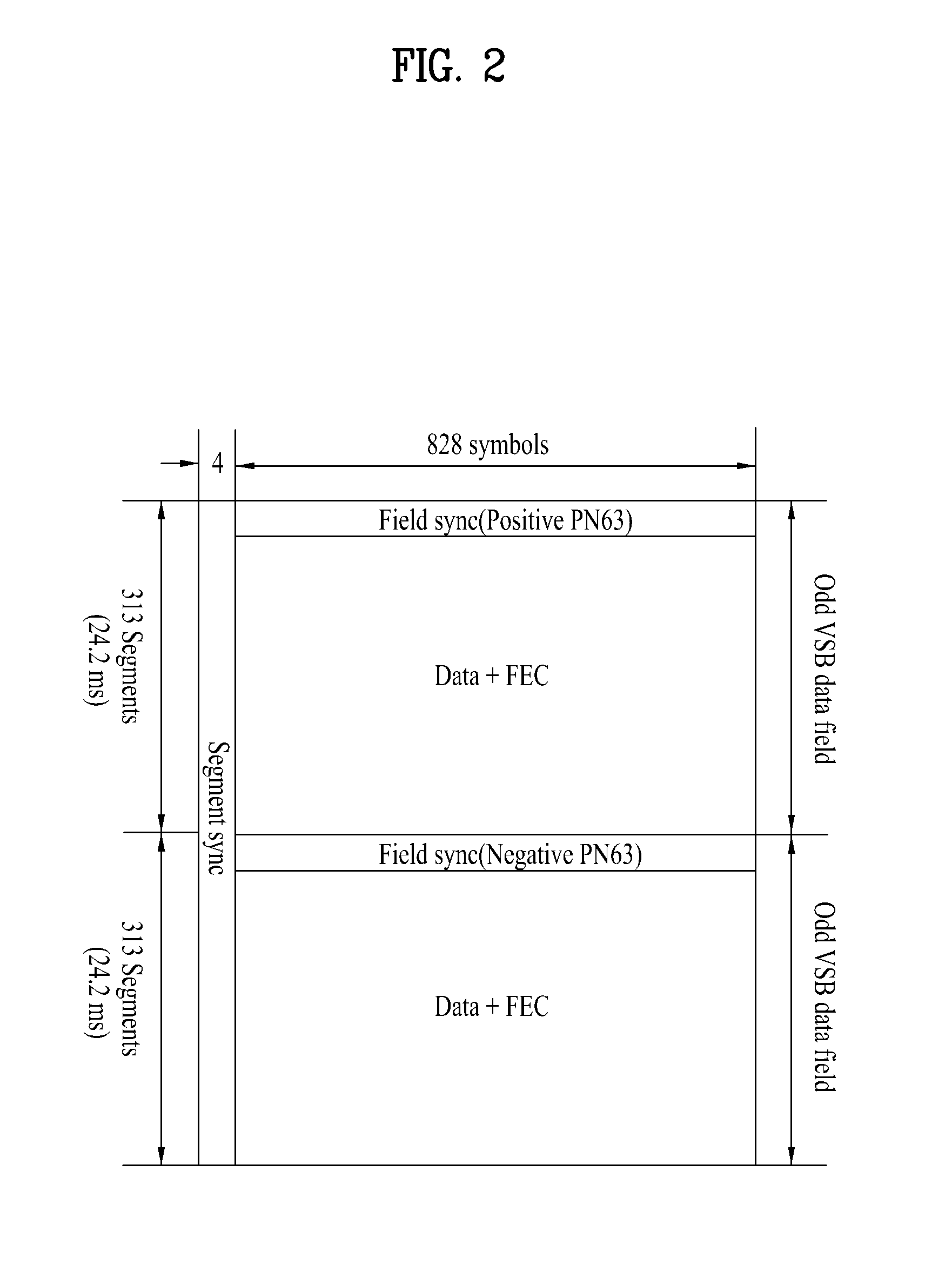

A transmitting system and a method of transmitting digital broadcast signal are disclosed. The method of transmitting digital broadcasting signal in a transmitter includes forming a data group including mobile data, known data sequences, trellis initialization data bytes, wherein the known data sequences are sequentially concatenated with the trellis initialization bytes, interleaving data in the data group, wherein the data group includes a plurality of data blocks and scalable data blocks, wherein the known data sequences inserted in a predetermined area of the data group, trellis encoding on the interleaved data and initializing memories for the trellis encoding using initial bits of the trellis initialization data bytes in the interleaved data, wherein the initial bits of the trellis initialization data bytes are calculated using exclusive or operation with predetermined memory values of the memories for the trellis encoding, transmitting a broadcast signal including the trellis encoded data during a slot.

Owner:LG ELECTRONICS INC

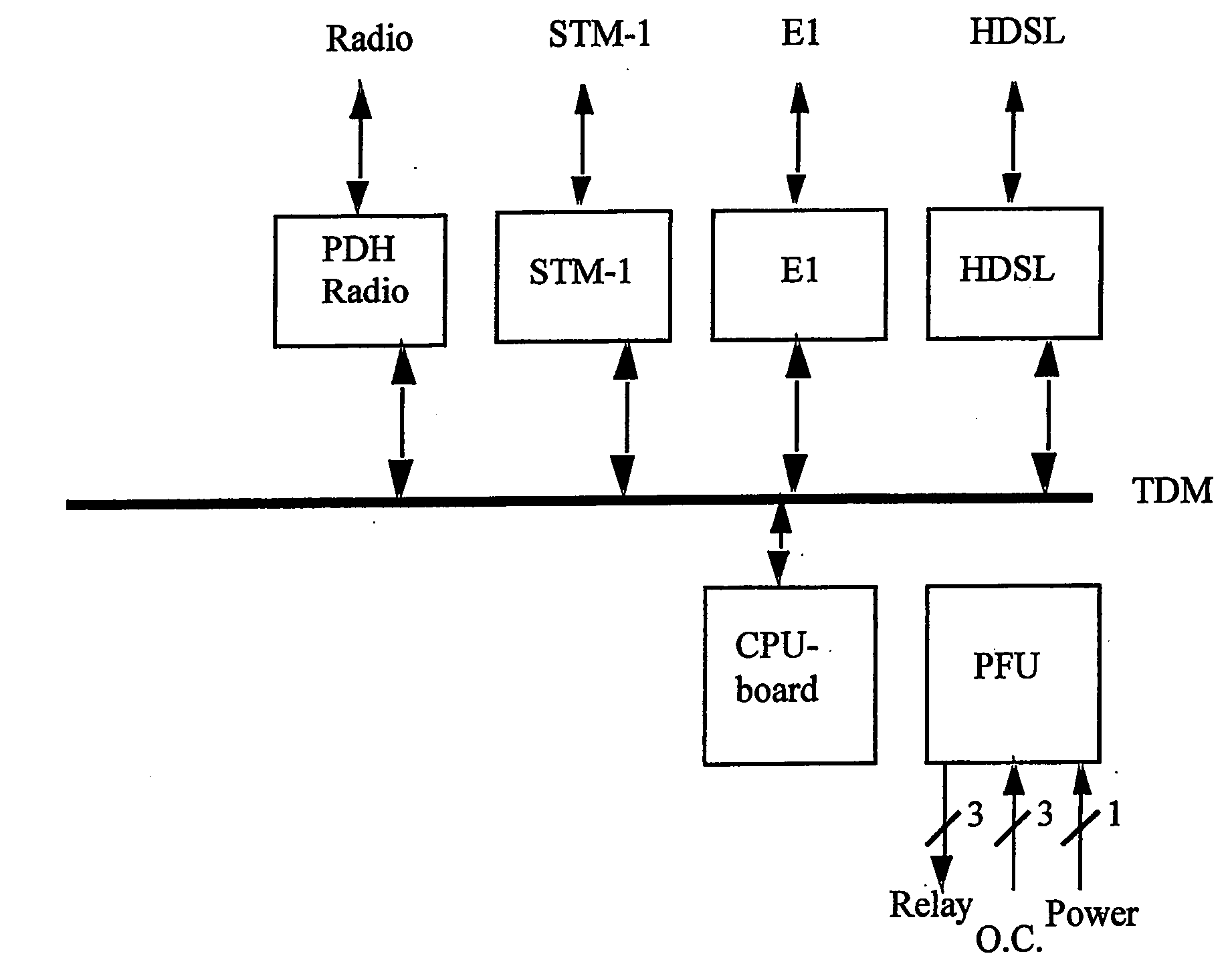

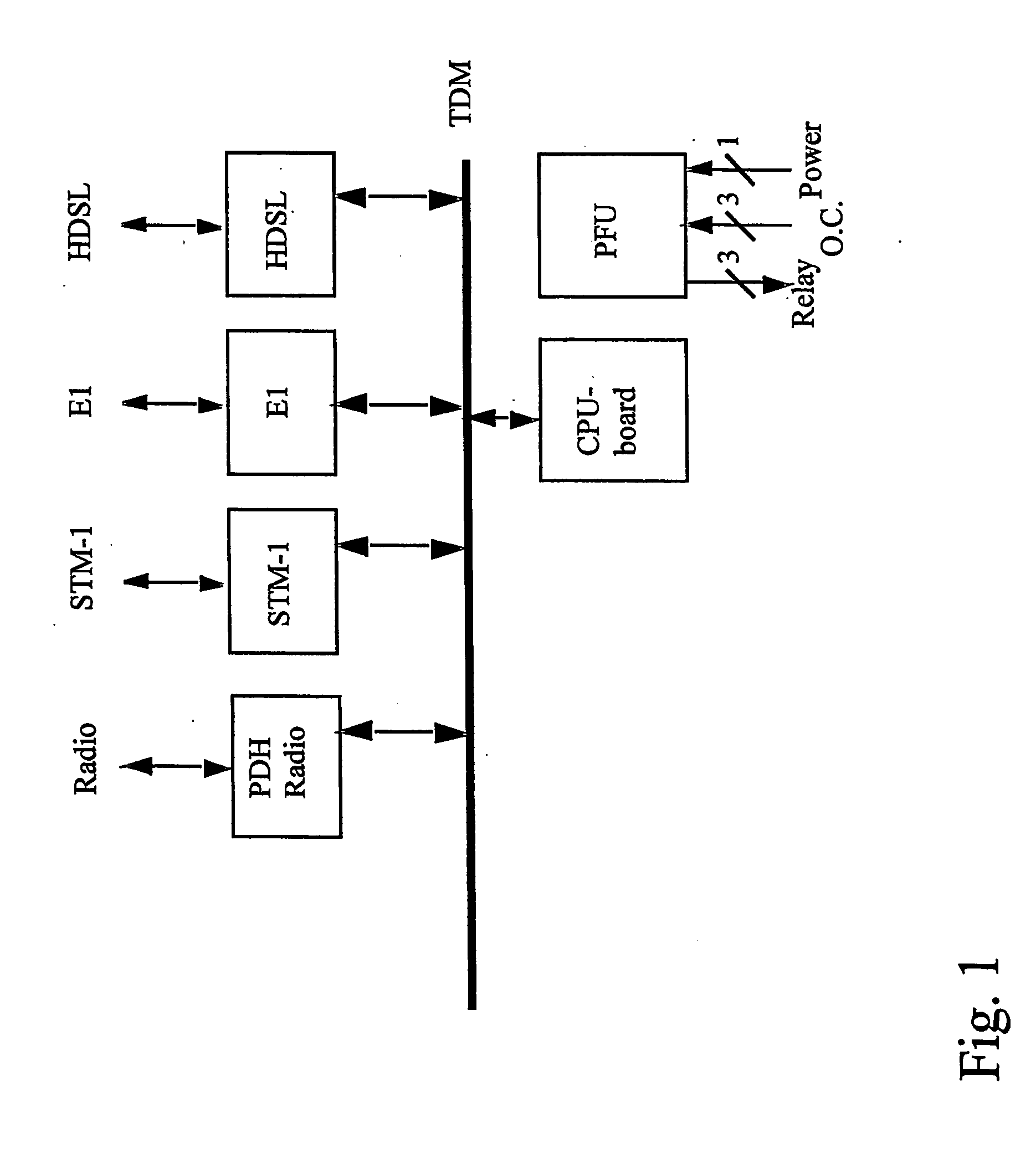

Switching arrangement including time-slot buses and serveral buffers

InactiveUS20060002398A1Drawback can be obviatedData switching by path configurationStore-and-forward switching systemsData streamConnection table

An arrangement for transmitting independent serial data streams through synchronous Time Division Multiplexing (TDM) switches with a number of input and output lines is disclosed. At the receiving side of a switch, there is one data buffer per TDM bus buffering the data before transfer on the bus. A connection table associated with each buffer includes entries addressing the bytes in the buffer. The order of the addresses determines the order of the bytes as they are transferred over the bus. Also, at the transmitting side, there is one data buffer per bus, but only one common connection table. The connection table is divided into one memory area per output line, and determines the order of the data bytes, as they will occur at the respective output lines.

Owner:TELEFON AB LM ERICSSON (PUBL)

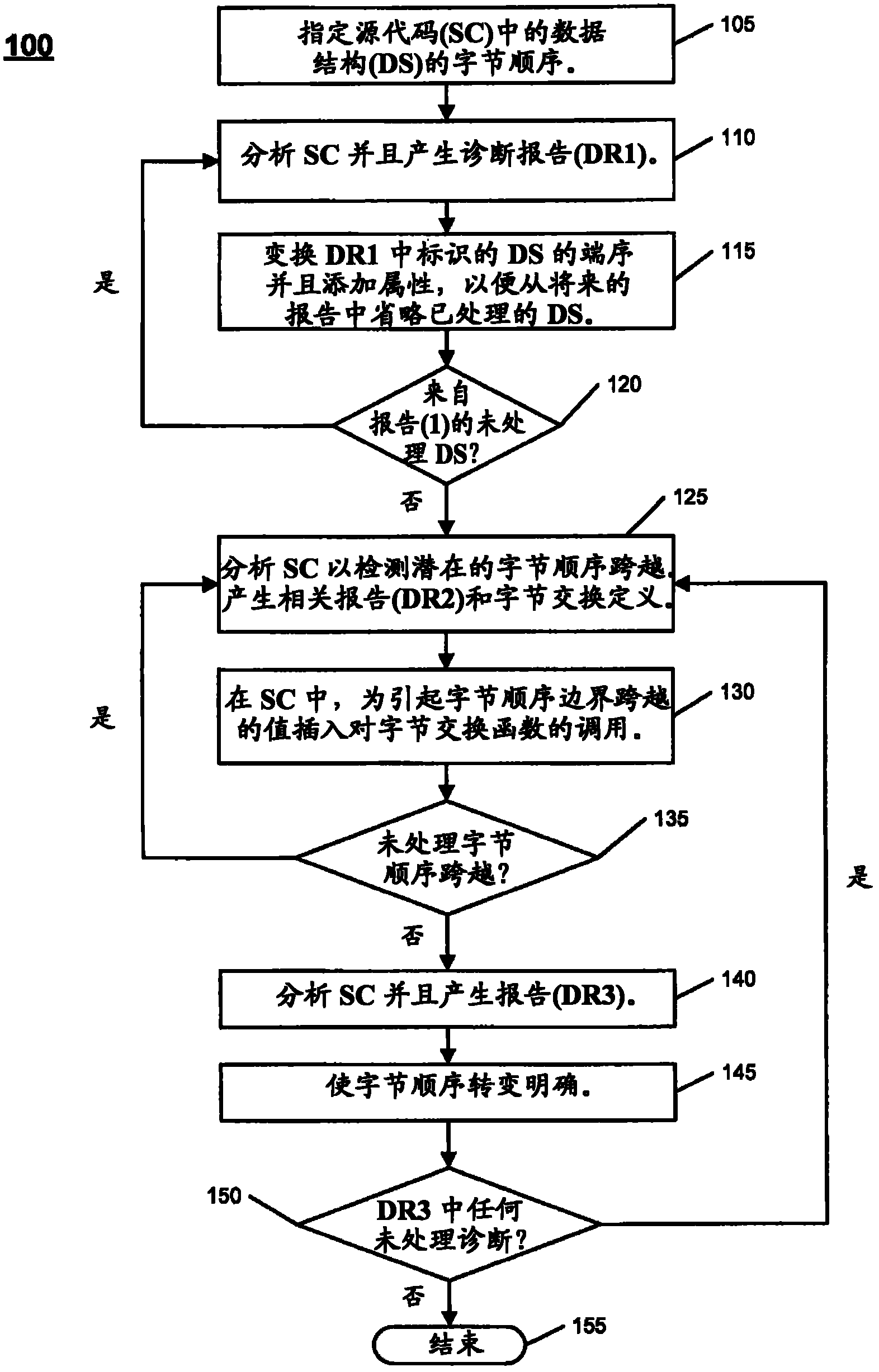

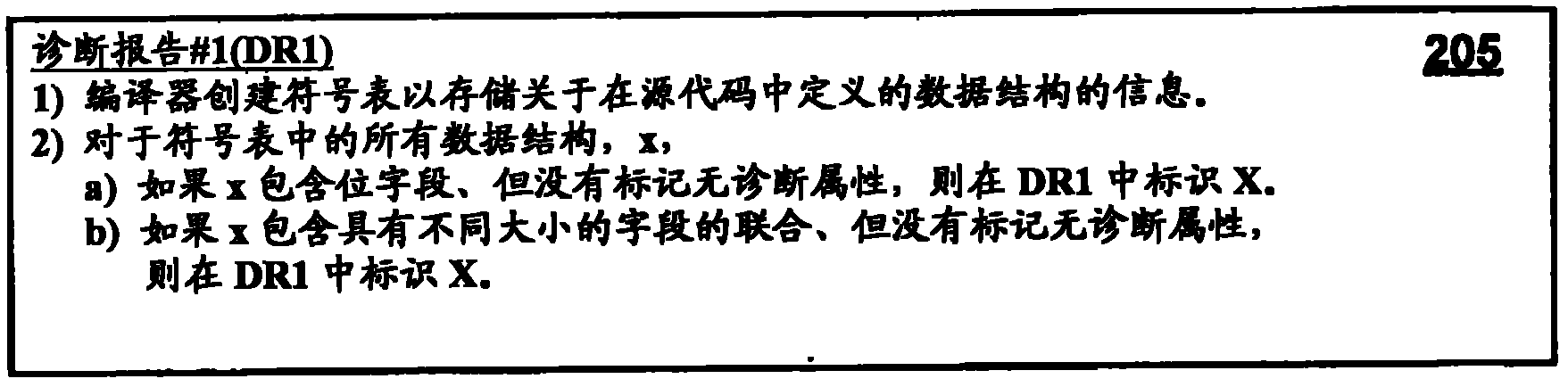

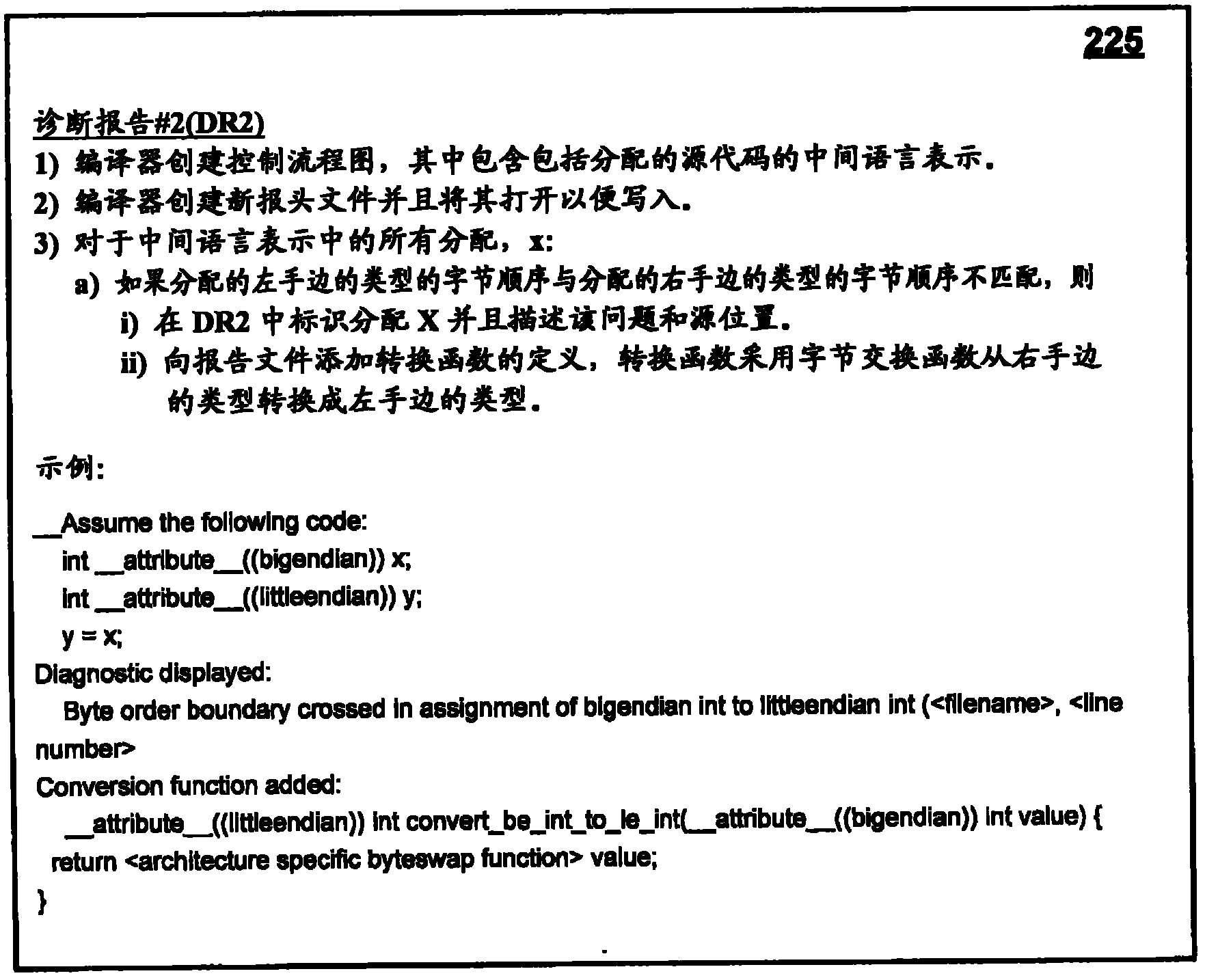

Methods and apparatuses for endian conversion

An embodiment of the invention includes code, such as a compiler, that enables byte order dependent code to execute on opposite byte order dependent architectures or systems. The compiler analyzes source code and produces diagnostic reports that indicate where source code changes are desirable to produce 'endian neutral' source code versions that are compatible with opposite byte order dependent architectures or systems. Such source code changes may be desirable for code portions that will produce implicit byte order changes or byte order border crossings. The modified source code that is generated may include the semantics of the desired endian conversion, as opposed to generated executable code that includes proper endian formats but which may limit the architectures to which the code is applicable.

Owner:INTEL CORP

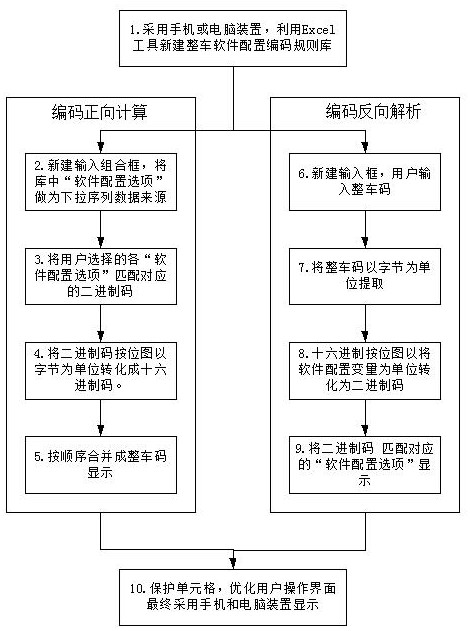

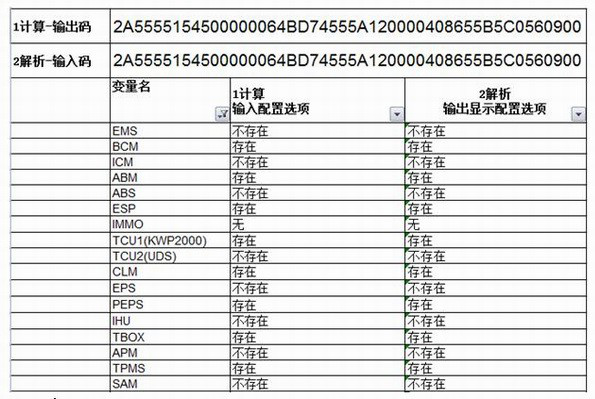

A method of excel to realize the calculation and analysis of vehicle software configuration code

ActiveCN109063006BImprove work efficiencyEasy to useText processingSpecial data processing applicationsEndiannessHexacode

Owner:CHERY AUTOMOBILE CO LTD

Pixel reordering and selection logic prior to buffering

InactiveUS20050036060A1Television system detailsTelevision system scanning detailsEndiannessComputer graphics (images)

Presented herein are systems and methods for pixel reordering and selection. A decoded picture is stored in a frame buffer with a particular pixel order and byte order. A input data write unit fetches portions of the decoded picture and stores portions of the picture in a double buffer with the same pixel order and byte order. An endian swizzle converts the byte ordering to a predetermined format, as needed. Reordering logic changes the pixel order to a predetermined order. Selection logic selects luma and chroma pixels from fetched pixels and provides the luma pixels to a luma pixel register, chroma Cr pixels to a chroma Cr pixel register, and chroma Cb pixels to a chroma Cb pixel register.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE