Three dimensional CMOS integrated circuits having device layers built on different crystal oriented wafers

A three-dimensional integration and device technology, used in circuits, semiconductor devices, electrical solid devices, etc., can solve problems such as poor electrical properties, difficult to control the surface orientation of the recrystallized layer, and low-level device and circuit performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

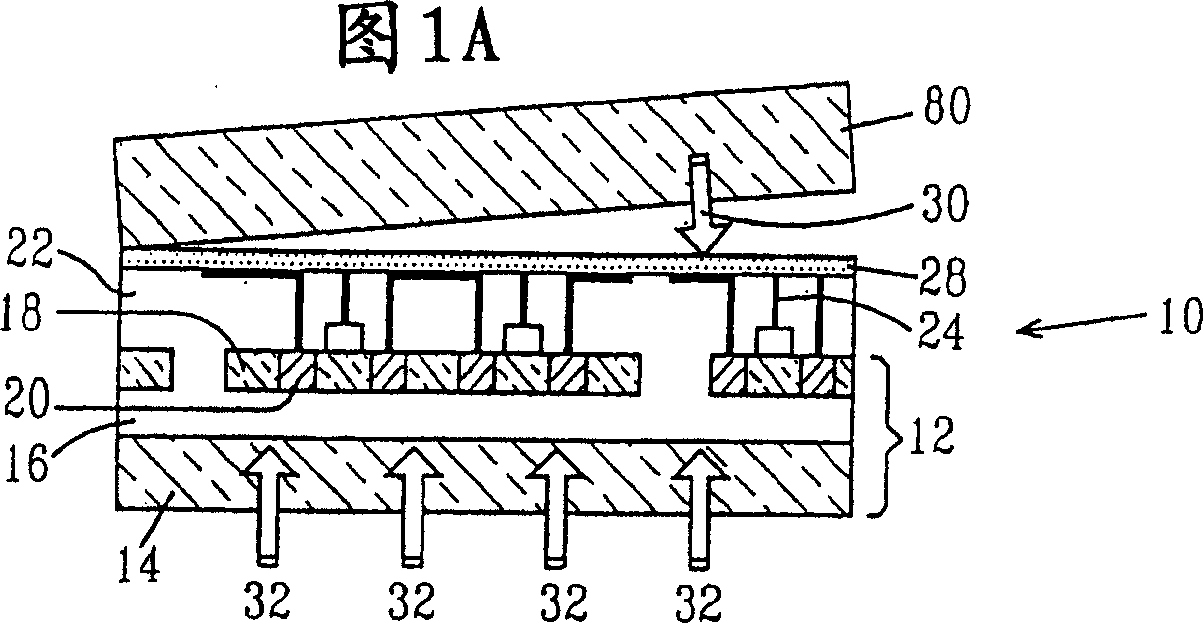

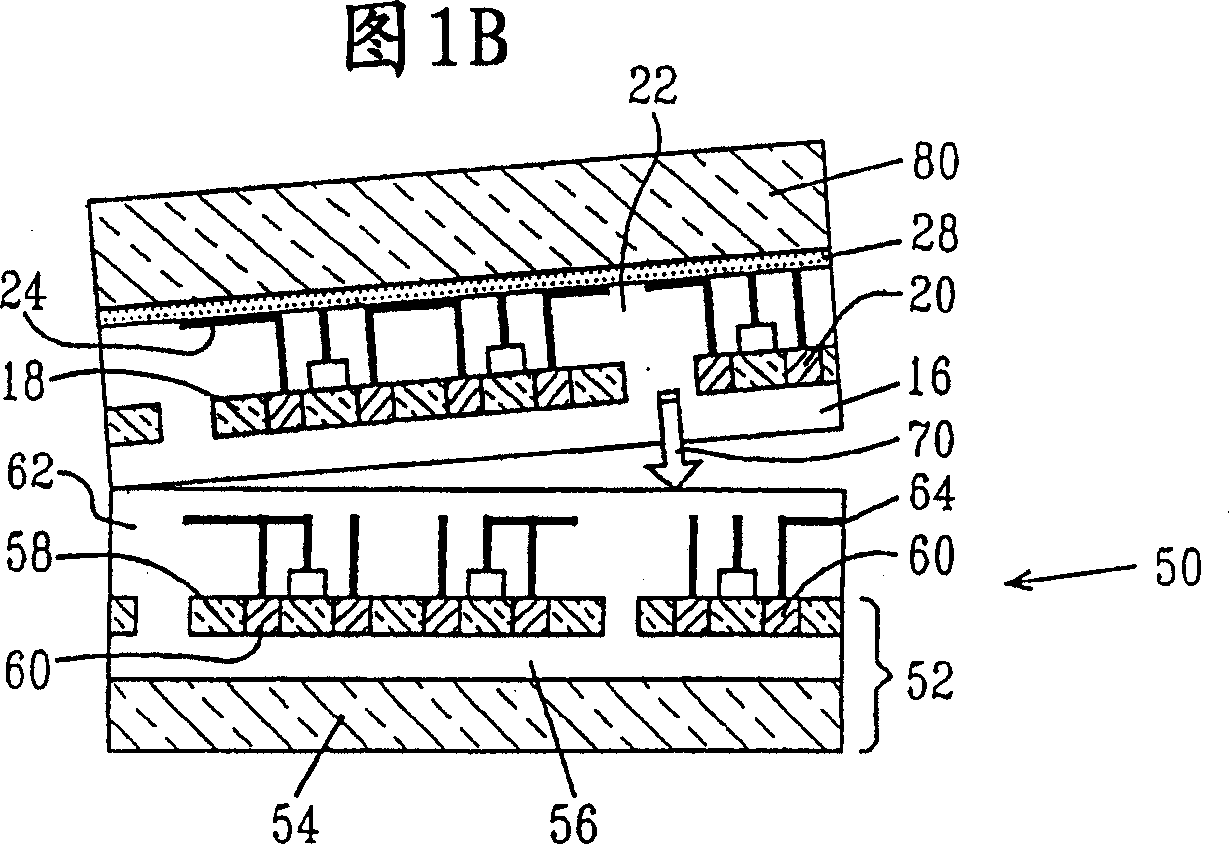

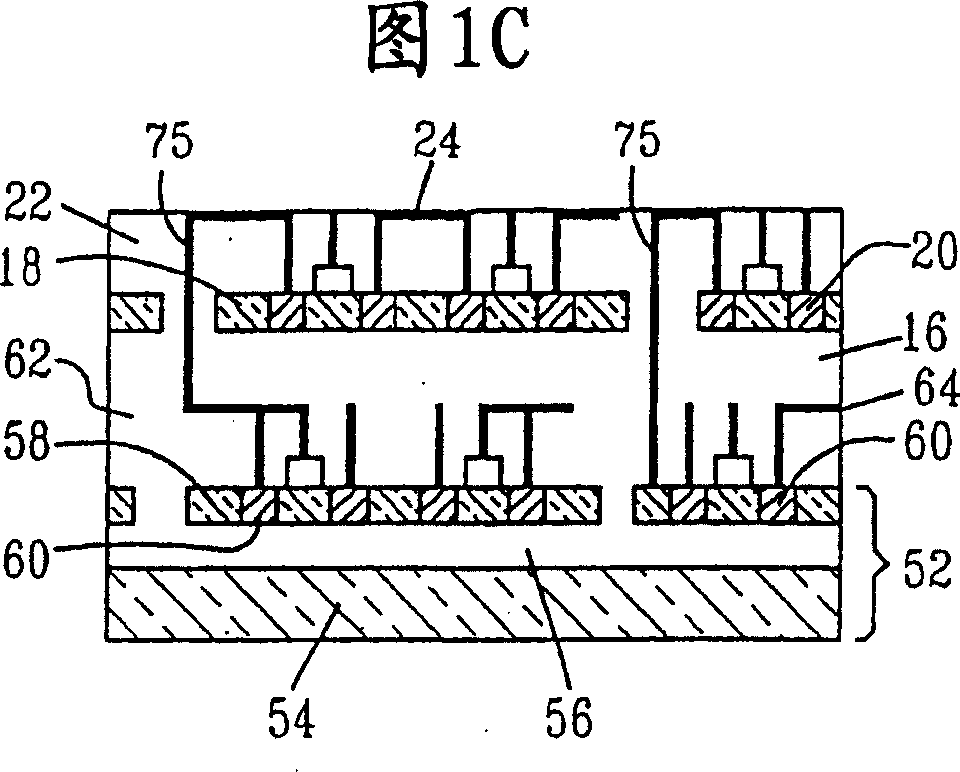

[0031] The present invention will be described in more detail below with reference to the accompanying drawings of the present invention. The present invention provides a three-dimensional integration scheme for fabricating three-dimensional CMOS integrated circuits with device layers formed on SOI wafers with different crystal orientations. In these drawings, similar reference numerals are used to designate similar and / or corresponding elements.

[0032] In the present invention, the term "silicon-on-insulator" or "SOI" wafer (the term "substrate" can be used interchangeably with the term "wafer") is used to define a semiconductor structure in which a buried oxide layer is used. The buried insulating layer separates the top silicon-containing layer (also called SOI layer or device layer) from the bottom silicon-containing substrate layer. The term "silicon-containing" is used in the present invention to mean a semiconductor material including silicon. Illustrative examples of such ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More